如何在cadence中观察放大器的增益

模拟技术

描述

Cadence可以实现电路图输入(Schematic Input)、电路仿真(Analog Simulation)、版图设计(Layout Design)、版图验证(Layout Verification)、寄生参数提取(Layout Parasitic Extraction)以及后仿真(Post Simulation)。

这篇文章我们来学习对共源放大器(包括纯电阻负载和有源负载)做DC、AC和Tran分析,验证它的输入输 出特性曲线,学习如何在cadence软件中观察放大器的增益和各种波形,学习在Results Displaying Window中查看各种电路参数,以及对放大器做参数化扫描。

01 电阻负载仿真

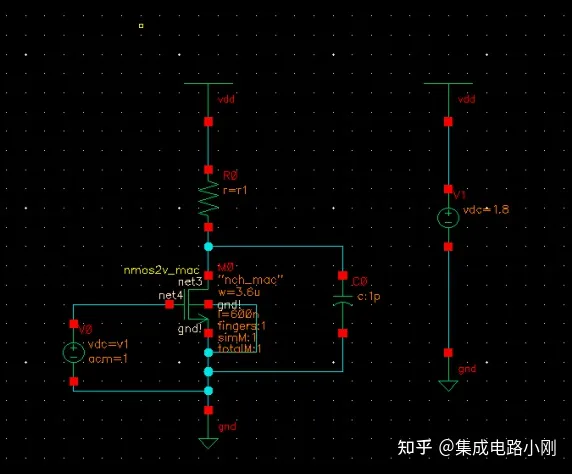

(总电路图)

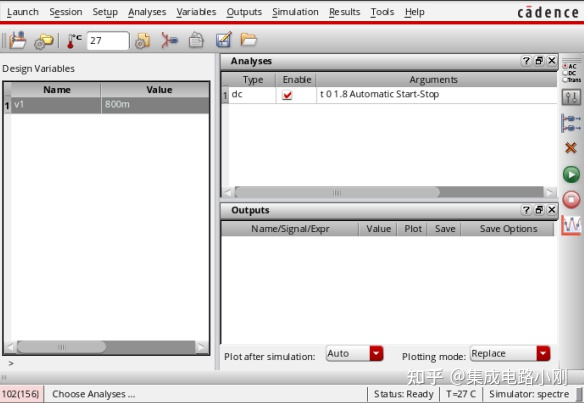

1)DC仿真

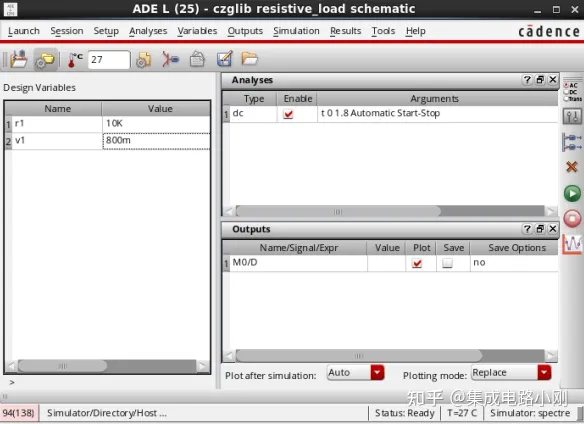

(DC仿真参数设置)

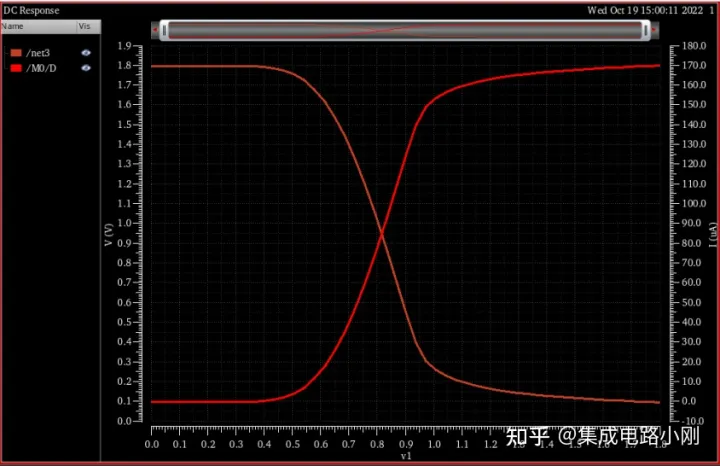

(仿真结果)

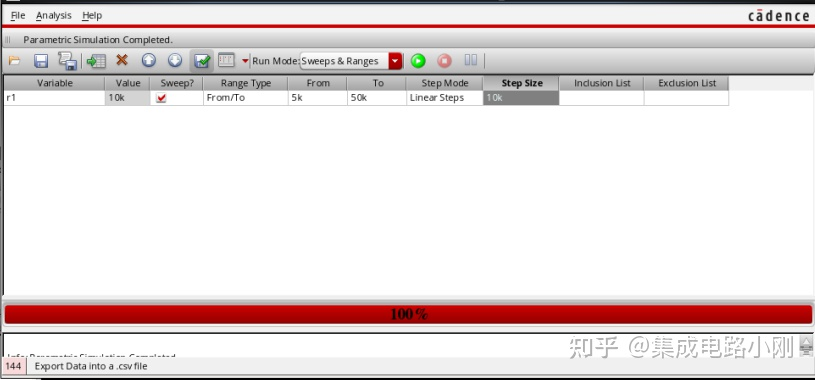

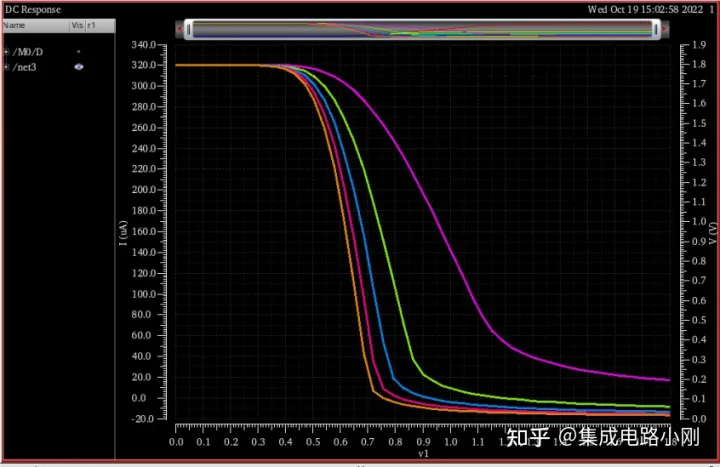

对电阻值进行参数扫描

(参数设置)

(仿真结果)

从图中可以看出,共源放大器的增益(图中斜线的斜率)随输出电阻的增大而增大,而输入输出摆幅却随输出电阻的增大而变小。因此在增益和摆幅之间存在折中。

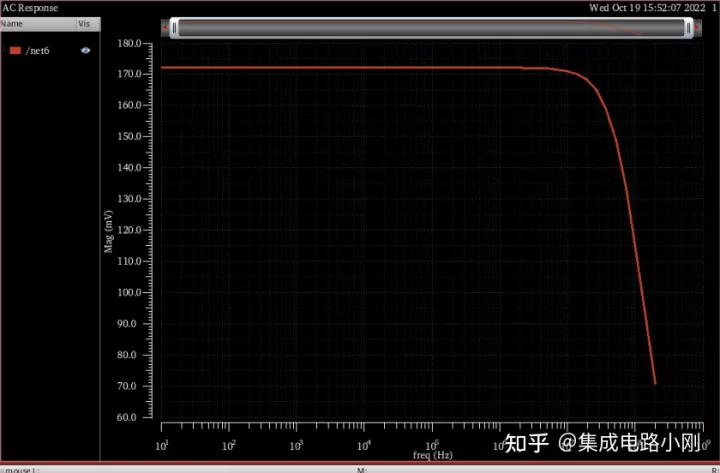

2)AC仿真

(参数设置)

(仿真结果)

从图中可以看出此时放大器低频时的增益为5.6,当频率超过447Hz时,增益开始下降。由公式

Au=-RDµnCoxW/L(Vin—VTH)=-gmRD

可知在偏置电压不变的情况下,固定输出电阻和mos管的宽长比两个参数中的一个,则放大器增益与另一个呈正比。可以自己调节这两个参数,来观察增益的变化情况。

但是当RD大于一定的值,MOS管会进入线性区,例如当RD=100K时,MOS进入线性区,可以看到管子的增益下降。

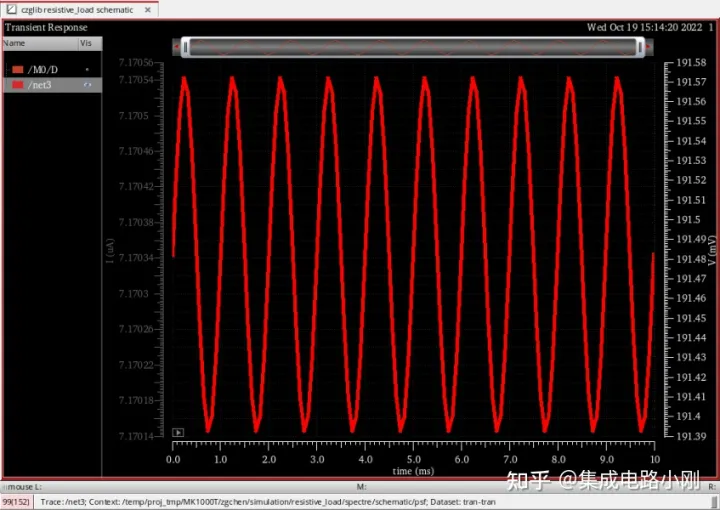

3)瞬态仿真

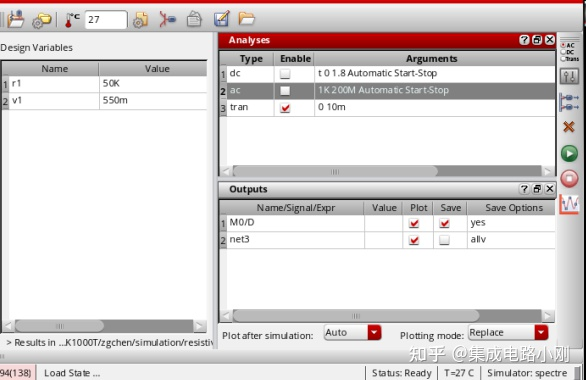

(参数设置)

(仿真结果)

从图中正弦的幅度可以看出,输入的小信号0.1mv被放大了5.6倍。

当RD=50K时,VDS即静态工作点VOUT输出在191mv附近。(仿真电路交流输入有问题)

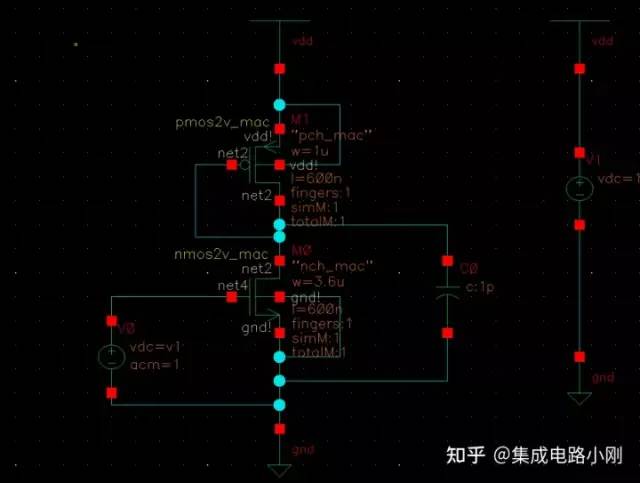

02 对二极管负载电路仿真

(总电路图)

(参数设置)

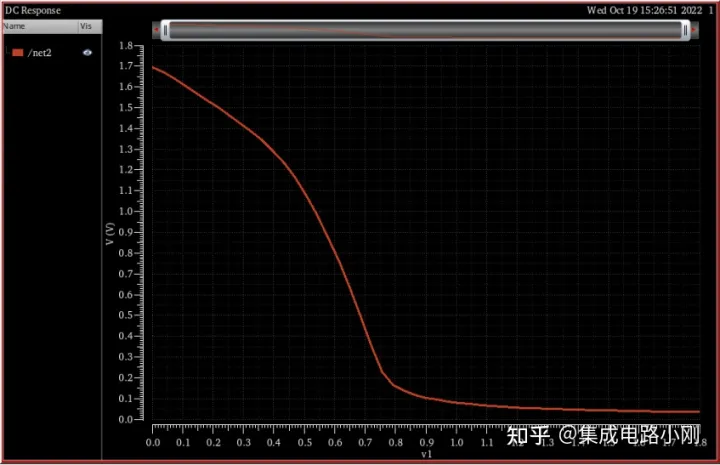

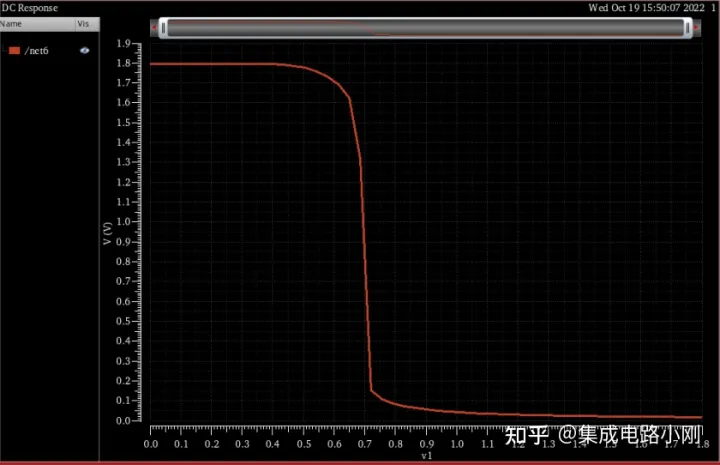

(仿真结果)

从图中可以发现以二极管为负载的共源放大器的输入输出曲线在起始部分,即v1的时候,并不像以电阻为负载时那样平直,请大家考虑出现这种现象的原因。<>

二极管接法的MOS管存在体效应,所以其在电压小于VTH时其存在增益

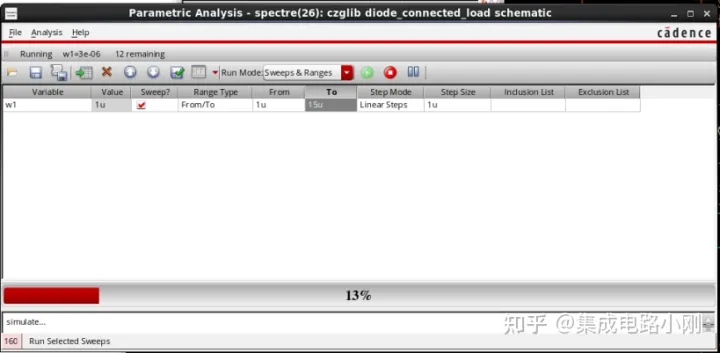

在schematic中将负载pmos管的宽w设为变量w1,其余参数不变,保存后在ADE环境下重新调入变量w1,并对它设置初始值1u。然后对w1进行参数化扫描,使w1的变化范围为1u→15u,仿真步数设为15。

(参数设置)

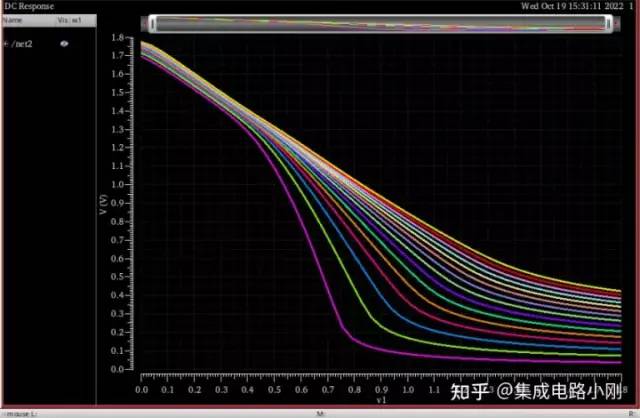

(仿真结果)

W越小其等效电阻越小,其余量越大

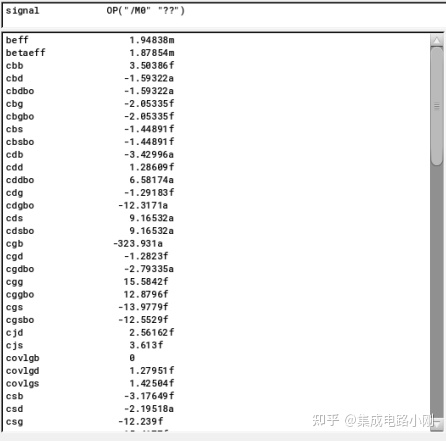

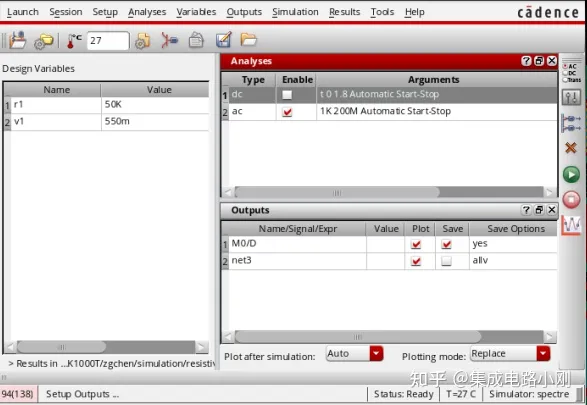

根据DC分析的结果,重新设置v1和w1的值,以使增益尽量提高。v1=0.6v,w1=1u。点击Analysis->choose,选中AC项,频率扫描范围为1k→200M。

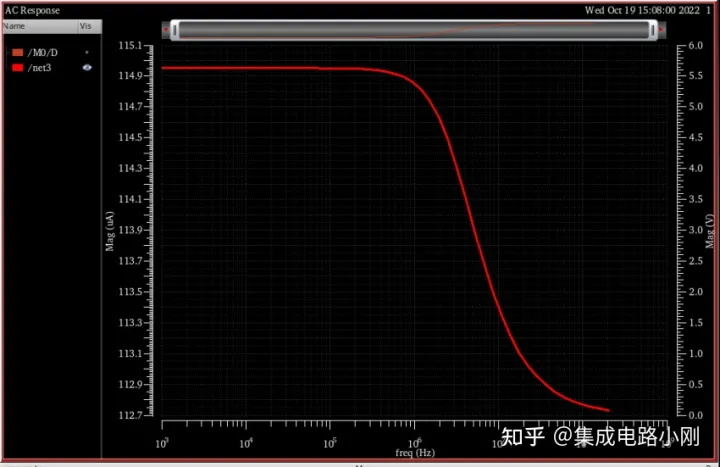

(仿真结果)

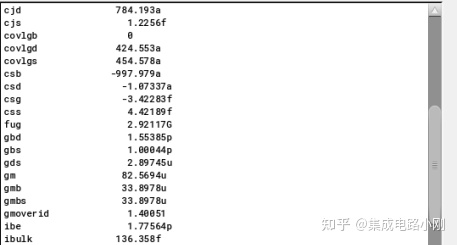

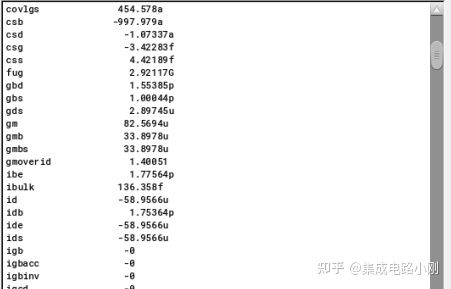

在Results Displaying Window中可以看到此时作为负载的pmos管的gm=86.57u。

作为输入器件的mos管的跨导gm=82.57u

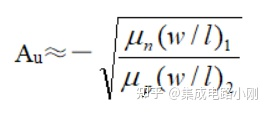

Au≈-gm1/gm2

可以通过改变两个mos管的宽长比来调节放大器的增益。事实上放大器的增益还受到输出摆幅的影响,在改变宽长比的同时,适当改变放大器的偏压才有可能达到理想的放大倍数。

03 对电流源做负载仿真

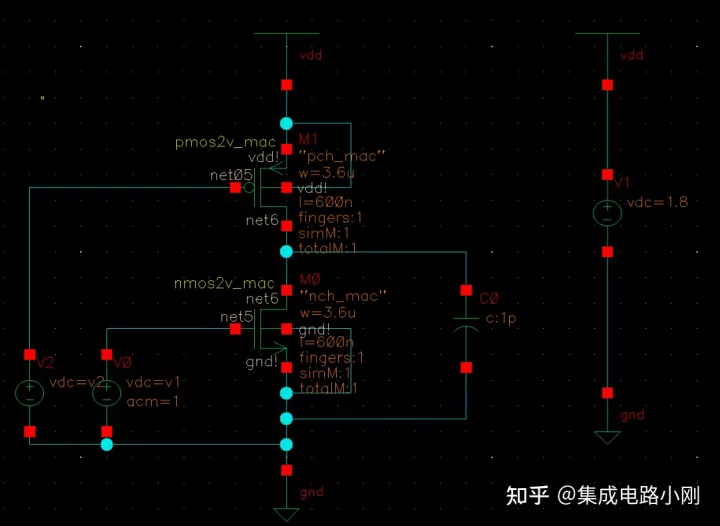

(电路图)

将M1的偏置电压v1设为0.9 v,工艺库下的阈值电压Vth≈0.4v,所以M1管的过驱动电压vod≈0.5v。若使M2管也有相同的过驱动电压,则可估算出M2管的偏置电压v2为0.9 v。

(仿真结果)

点击Analysis->choose,选中AC项。由于这种结构会引入大的寄生电容,因而会影响到高频特性,所以频率扫描范围改为0.01k→200M。

开始仿真。

(仿真结果)

仿真结果显示一电流源做负载对增益有很大的提高。

04 总结

| 输出阻抗 | 放大器增益 | 摆幅 | 其他 | |

|---|---|---|---|---|

| 纯电阻作负载 | 输出阻抗小;电阻阻值误差较大,且大阻值电阻占用面积大 | 增益较小;通过增大输出电阻来提高增益会使mos管很快进入线形区 | 输入输出摆幅小,和增益间存在矛盾 | 一般用作低增益高频放大器 |

| 二极管作负载 | 输出阻抗大,在制造中容易精确控制 | 增益较小,且相对精确稳定,是器件尺寸的弱相关函数 | 输入输出摆幅小,和增益间仍存在矛盾 | |

| 电流源作负载 | 输出阻抗很大 | 增益很大 | 摆幅较大;解决了摆幅与增益间的矛盾 | 引入了寄生电容,影响频率特性 |

编辑:黄飞

-

如何在Keil中观察程序的执行时间?2023-10-15 654

-

放大器稳定电压增益的含义是什么?2023-09-21 3352

-

怎么提高放大器电压增益?2023-09-17 5940

-

可变增益放大器的常见用途2023-07-06 2705

-

动态可编程增益放大器2023-04-12 929

-

程控增益放大器原理详解2022-11-04 7318

-

可变增益放大器电路图(十一款可变增益放大器电路设计原理图详解)2018-03-26 117699

-

增益可调放大器的设计2017-09-04 1090

-

程控增益放大器和自动调整增益放大器的设计2011-08-11 2747

-

时变增益放大器2009-09-02 2620

-

利用Cadence设计COMS低噪声放大器2009-07-06 3275

-

可变增益放大器2009-03-20 1154

全部0条评论

快来发表一下你的评论吧 !