运放参数的详细解释和分析

模拟技术

描述

1—输入偏置电流和输入失调电流

一般运放的datasheet中会列出众多的运放参数,有些易于理解,我们常关注,有些可能会被忽略了。在接下来的一些主题里,将对每一个参数进行详细的说明和分析。力求在原理和对应用的影响上把运放参数阐述清楚。由于本人的水平有限,写的博文中难免有些疏漏,希望大家批评指正。

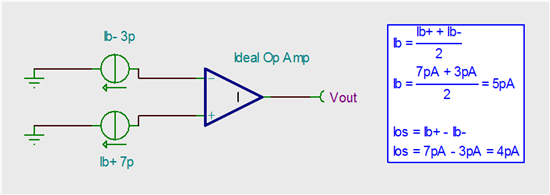

第一节要说明的是运放的输入偏置电流Ib和输入失调电流Ios .众说周知,理想运放是没有输入偏置电流Ib和输入失调电流Ios .的。但每一颗实际运放都会有输入偏置电流Ib和输入失调电流Ios .我们可以用下图中的模型来说明它们的定义。

输入偏置电流Ib是由于运放两个输入极都有漏电流(我们暂且称之为漏电流)的存在。我们可以理解为,理想运放的各个输入端都串联进了一个电流源,这两个电流源的电流值一般为不相同。也就是说,实际的运入,会有电流流入或流出运放的输入端的(与理想运放的虚断不太一样)。那么输入偏置电流就定义这两个电流的平均值,这个很好理解。输入失调电流呢,就定义为两个电流的差。

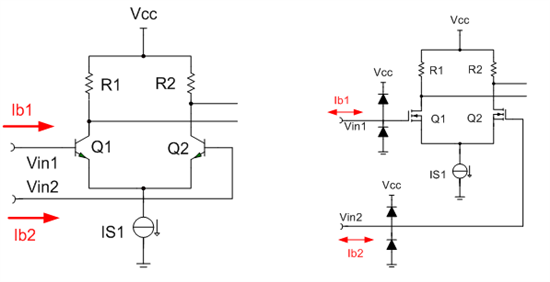

说完定义,下面我们要深究一下这个电流的来源。那我们就要看一下运入的输入级了,运放的输入级一般采用差分输入(电压反馈运放)。采用的管子,要么是三级管bipolar,要么是场效应管FET。如下图所示,对于bipolar,要使其工作在线性区,就要给基极提供偏置电压,或者说要有比较大的基极电流,也就是常说的,三极管是电流控制器件。那么其偏置 电流就来源于输入级的三极管的基极电流,由于工艺上很难做到两个管子的完全匹配,所以这两个管子Q1和Q2的基极电流总是有这么点差别,也就是输入的失调电流。Bipolar输入的运放这两个值还是很可观的,也就是说是比较大的,进行电路设计时,不得不考虑的。而对于FET输入的运放,由于其是电压控制电流器件,可以说它的栅极电流是很小很小的,一般会在fA级,但不幸的是,它的每个输入引脚都有一对ESD保护二极管。这两个二极管都是有漏电流的,这个漏电流一般会比FET的栅极电流大的多,这也成为了FET输入运放的偏置电流的来源。当然,这两对ESD保护二极管也不可能完全一致,因此也就有了不同的漏电流,漏电流之差也就构成了输入失调电流的主要成份。

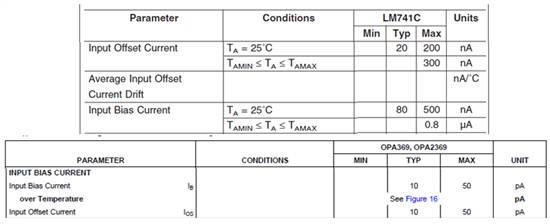

下面列表中上表是bipolar的LM741的输入偏置电流和输入失调电流,这个电流流到外面电阻,即使是K欧级的,也会产生几十uV的失调电压,再经放大,很容易就会使输出的电压误差到mV级。下表则是CMOSFET的OPA369的输入偏置电流和输入失调电流,这两个值要小的多了,比较好的COMS运放输入偏置电流和输入失调电流的典型值可以做到小于1pA的目标。

这里还要强调的是,ESD的反向漏电流是与其反相电压有关的。因此当Vin=(Vcc-Vss)/2 时,加在两个ESD保护二极管的电压相当,他们的反向电流可以认为是近似相等的,此时理想情况是无电流流入或流出的,实际情况是电流达到最小值。因此这时有最小的偏置电流,当运放输入端电压Vin不等于(Vcc-Vss)/2,势必造成一个二极管的反向电压高,另一个低,此时两个二极管的反向漏电流就不等了,这个差电流就会构成了输入偏置电流的主要成份。这个现场称为领节效应。因此要使FET输入偏置电流最小,就要把共模电压设置在(Vcc-Vss)/2处。

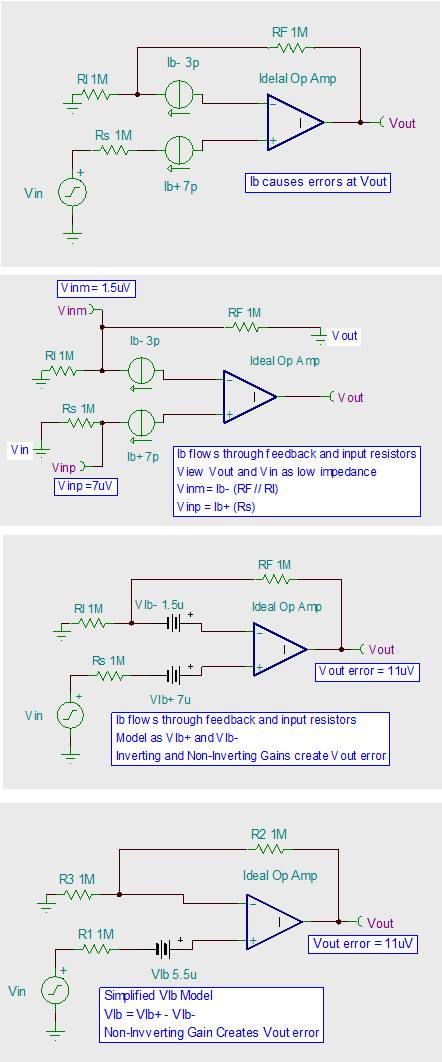

上面分析了定义和来源。下面就要说说这两个参数对电路的影响了,输入偏置电流会流过外面的电阻网络,从而转化成运放的失调电压,再经运放话后就到了运入的输出端,造成了运放的输入误差。这也就说明了,在反向放大电路中,为什么要在运放的同相输入端连一个电阻再接地的原因。并且这个电阻要等于反向输入端的电阻和反馈电阻并联后的值。这就是为了使两个输入端偏置电流流过电阻时,形成的电压值相等,从而使它们引入的失调电压为0。这样说,太抽象了,还是看下面一组图容易理解一些。

再有一点,对于微小电流检测的电路,一般为跨阻放大电路,如光电二极管的探测电路,一般有用光信号都比较微弱转化的光电源信号更微弱,常常为nA级甚于pA级。这个电路的本意是想让光电流向反馈电阻流动从而在放大电路输出端产生出电压。如果选用的运放的输入偏置电流过大,刚这个微弱的光电流会有一部分流入到运放的输入端,而达不到预设的I/V线性转化。

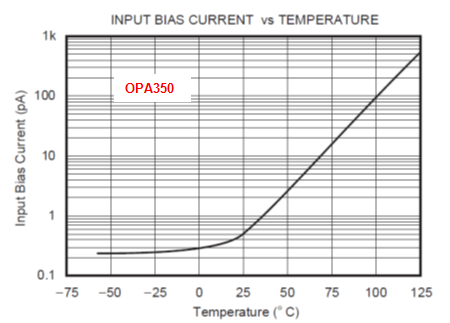

还需要注意的一点时,许多运放的输入失调电流会随着温度的变化而变化,如下图所示OPAl350的输入失调电流会在高于25度时快速的升高。在100度时的输入偏置电流是25度时的几百倍。如果设计的系统是在很宽的温度范围内工作,这一因素不得不考虑。

以上啰啰嗦嗦的讲了运放的输入偏置电流和失调电流,希望对大家有用。下一节中将详细剖析其它参数。

2—如何测量输入偏置电流Ib,失调电流Ios

上一节讲了运放输入偏置电流和输入失调电流。这一节给出输入偏置电流测量方式。总体来说主要有两种测试方法, 一种是让输入偏置电流流入一个大的电阻,从而形成一个失调电压,然后放大失调电压并进行测量,这样就可以反算出输入偏置;另一种方法是让输入偏置电流流入一个电容,用电容对这个电流进行积分,这样只要测和电容上的电压变化速率,就可以计算出运放的偏置电流。

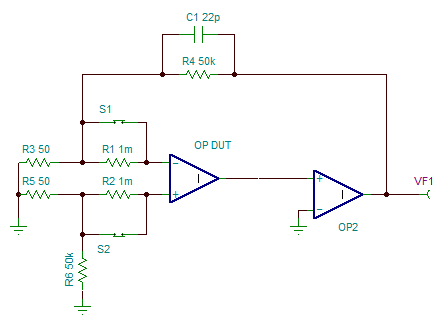

先介绍第一种方法,具体电路如下图所示,C1是超前补偿电容以防止电路的振荡,根据实际电路选择。OP2是测试辅助运放,需选低偏置电压和低偏置电流的运放。测试步骤和原理下面一步一步进行推算。

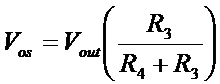

(1)首先测试运放的失调电压。关闭S1和S2,测试出OP2运放的输出电压记下Vout 。则输入失调电压为:

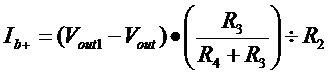

(2)打开S2,待测运放的Ib+流入R2,会形成一个附加的失调电压Vos1,测试出OP2运放的输出电压记下Vout1。则运放同向输入失调电压为:

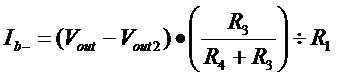

(2)关闭S2,打开S1,待测运放的Ib-流入R1,会形成一个附加的失调电压Vos2,测试出OP2运放的输出电压记下Vout2。则运放反向输入失调电压为:

(4)运放输入偏置电流为

Ib=[(Ib+)+(Ib-)]/2

运放输入失调电流为

Ios=(Ib+)-(Ib-)

这种测试方法有几个缺点,一个是使用了很大的电阻R1和R2,一般会是M欧级,这两个电阻引入了很大的电压噪声。受到电阻R1和R2的阻值的限制,难以测得FET输入运放的偏置电流。

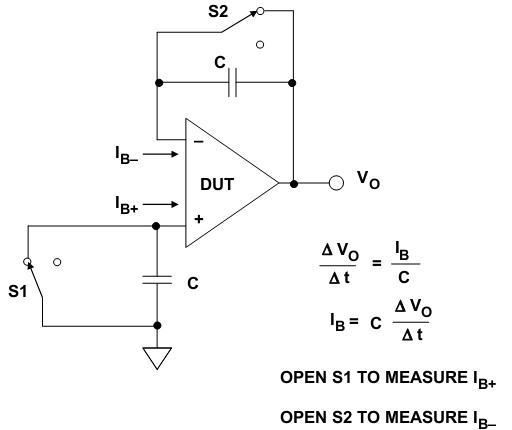

第二种方法测试方法,是让运放的输入偏置电流流入电容,具体测试如下图。从图中的公式很容易理解测试的原理,这个测试的关键,是选取漏电流极小的电容。

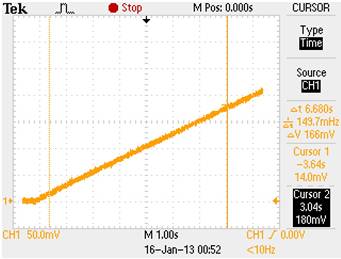

(1)打开S1,IB+流入电容C,用示波器观察Vo的变化,结果如下图,按上图的方法就可以计算出IB+。

ΔV /mVΔt /sC /nFIb /nA

No.1 IB+1666.689.540.237072

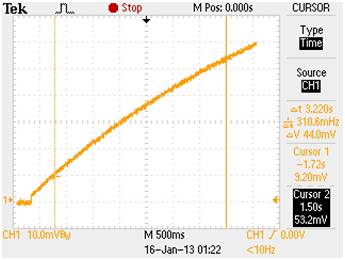

(2)关闭S1打开S2,IB-流入电容C,用示波器观察Vo的变化,结果如下图,可以计算出IB-。

(3)再根据定义就可以计算出运放的输入偏置电流和失调电流。

ΔV /mVΔt /sC /nFIb /nA

No.1 IB-443.229.540.13036

这种测试方法可以测得fA级的失调电流。测试时需要选用低漏电流的电容,推荐使用极低漏电流的特氟龙电容,聚丙烯(PP)电容或聚苯乙烯电容。

再分享一个经验,就是贴片电容在焊接过程中,由于引脚可能残留焊锡膏等杂质,会使FET运放的漏电流大大的增加。曾经测试一个偏置电流为小于10pA级的运放,由于没有对引脚 进行清洗,结果测得结果出现了很大的误差,或者叫差错,达了nA的水平了。

3—输入失调电压Vos及温漂

在运放的应用中,不可避免的会碰到运放的输入失调电压Vos问题,尤其对直流信号进行放大时,由于输入失调电压Vos的存在,放大电路的输出端总会叠加我们不期望的误差。举个简单,老套,而经典的例子,由于输入失调电压的存在,会让我们的电子秤在没经调校时,还没放东西,就会有重量显示。我们总不希望,买到的重量与实际重有差异吧,买苹果差点还没什么,要是买白金戒指时,差一克可是不少的money哦。下面介绍一下运放的失调电压,以及它的计算。最后再介绍一些低输入失调电压运放。不足之处,多多拍砖。

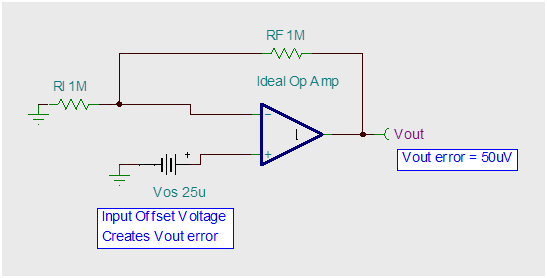

理想情况下,当运放两个输入端的输入电压相同时,运放的输出电压应为0V,但实际情况确是,即使两输入端的电压相同,放大电路也会有一个小的电压输出。如下图,这就是由运放的输入失调电压引起的。

当然严格的定义应为,为了使运放的输出电压等于0,必需在运放两个输入端加一个小的电压。这个需要加的小电压即为输入失调电压Vos。注意,是为了使出电压为0,而加的输入电压,而不是输入相同时,输出失调电压除以增益(微小区别)。

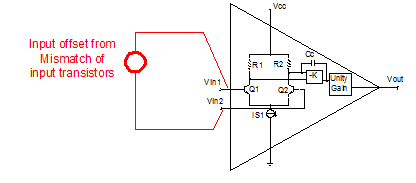

运放的输入失调电压来源于运放差分输入级两个管子的不匹配。如下图。受工艺水平的限制,这个不匹配是不可避免的。差分输入级的不匹配是个坏孩子,它还会引起很多其他的问题,以后介绍。

曾经请教过资深的运放设计工程师,据他讲,两个管子的匹配度在一定范围内是与管子的面积的平方根成正比,也就是说匹配度提高为原来的两倍。面积要增加四倍,当到达一个水平时,即使再增加面积也不会提高匹配度了。提高面积是要增加IC的成本的哦。所在有一个常被使用的办法,就是在运放生产出来后,进行测试,然后再Trim(可以理解为调校了)。这样就能使运放的精度大在提高。当然,测试和Trim都是需要成本的哦。所以精密运放的价格都比较贵。这段只当闲聊,呵呵。

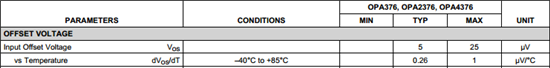

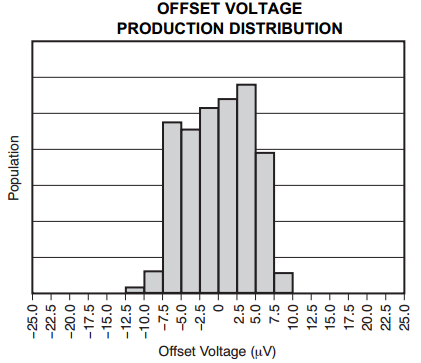

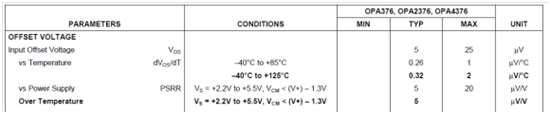

我们关注输入失调电压,是因为他会给放大电路带来误差。下面就要分析它带来的误差。在计算之前,我们再认识一个让我们不太爽的参数,失调电压的温漂,也就是说,上面提到的输入失调电压会随着温度的变化而变化。而我们的实际电路的应用环境温度总是变化的,这又给我们带来了棘手的问题。下表就是在OPA376 datasheet上截取下来的参数。它温漂最大值为1uV/℃(-40℃to 85℃)。一大批运放的Vos是符合正态分布的,因此datasheet一般还会给出offset分布的直方图。

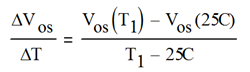

当温度变化时,输入失调电压温漂的定义为:

刚忘记了另一个重要的参数,就是运放输入失调电压的长期漂移,一般会给出类似uV/1000hours或uV/moth等。有些datasheet会给出这一参数。

下面举例计算一下OPA376,在85℃时的最大失调电压,主要是两部分,一部分是25度时的输入失调电压,另一部分是温度变化引起的失调电压漂移。

具体步聚如下图。从结果来看似1uV/℃温漂,在乘上温度变化时,就成为了误差的主导。因此,如果设计的电路在宽的温度范围下应用,需在特别关注温漂。

Vos(85℃)= 25uV+60uV=85uV.

如果放大电路的Gain改为100,则最大输出失调电压就为8.5mV。这是最差的情况。

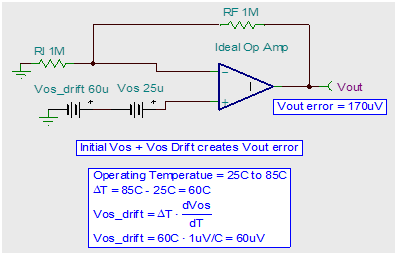

关于输入失调电压的测试在"运放参数的详细解释和分析-part2,如何测量输入偏置电流Ib,失调电流Ios"中有介绍,感兴趣的话,可以去看看。还有简单的测试方法,如下图:

Vos = Vout/1001

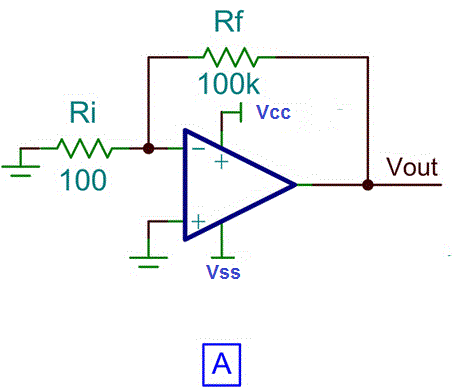

需要提醒的是,使用简易方法测试单电源运放的输入失调电压时,需要将输入端短路并提供一个低噪声的稳定电压偏置。如下图。

下面列一些低温漂运放,它们的最大漂移只有0.05uV/℃。输入失调电压Vio最大值只有5uV。

4—运放噪声快速计算

本文不是研究运放的噪声理论,TI的资深应用经理Art Kay已经写过一系列的文章来分析运放的噪声,相信大多数模拟电路工程师都读过。国内还有工程师把它翻译成中文。

今天主要从自上而下的角度分析一下运放电路的噪声组成,计算时几个主意要点和繁索的地方、最主要的是提供给大家一个方便的计算小工具,很好用,让噪声计算变的简单。

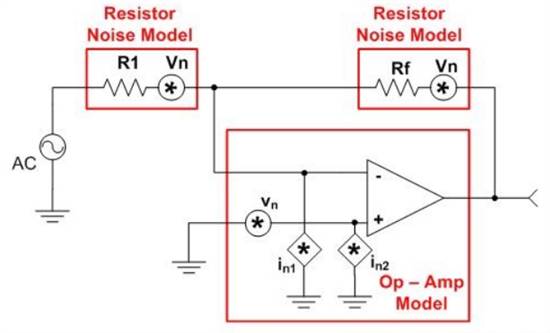

运放构成的反向放大电路中,噪声主要来源于三个方面

(1) 运放的输入噪声电压en(在datasheet中有数据和曲线)

(2) 运放的输入电流噪声in(在datasheet中同样可以找到数据和曲线)。这需要流过电阻后转化为电压噪声。

(3) 设置放大倍数的电阻R1和Rf的热噪声,也就是可以通过经典公式算出来的。Noise =√(4kTKRΔf)。这是不可避免的。很多情况下会成为主要噪声来源。

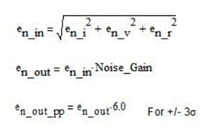

运放噪声的计算就是将这三个值一一求出来,由于这些噪声是不相关的。它们的矢量和即为运放的总输入噪声。再乘上噪声增益就可以得到输出端噪声,公式如下。看似简单实则很麻烦。

我们将计算得来和输入总噪声加到理想运放的正输入端,就得到了运放的噪声模型。注意,是正输入端哦,因此不管同向放大电路,还是反向放大电路对噪声的增益均为G=1+Rf/R1。我们可以简单理解为噪声是叠加到运放输入端的一个信号。如下图

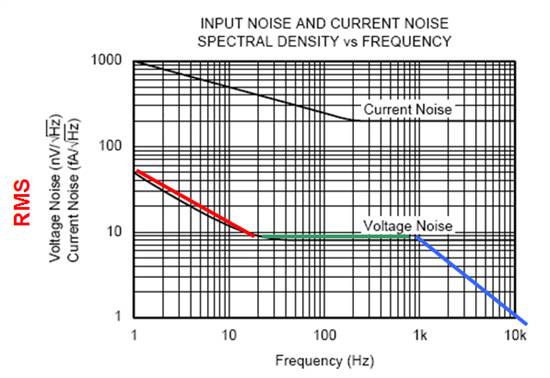

上面说了一个重要问题,运放的噪声增益。还要一个重要问题,运放的噪声带宽,datasheet中给出的运放噪声参数一般为谱密度值如1.1nV√Hz。也就是说,需要对它在噪声带宽中进行积分才可以得到噪声的RMS电压值。噪声带宽不同于信号的-3dB带宽。确切的说是Brickwall 滤波器的带宽。简单说,就是把实际的滤波器响应曲线,在保证包含面积不变时转化成理像低通滤波器时的带宽。好在我们可以查表得到,N阶滤波器的-3dB带宽与Brickwall 滤波器的带宽换算系数。如下表

Number of Poles in FilterKn

AC Noise Bandwidth Ratio

11.57

21.22

31.16

41.13

51.12

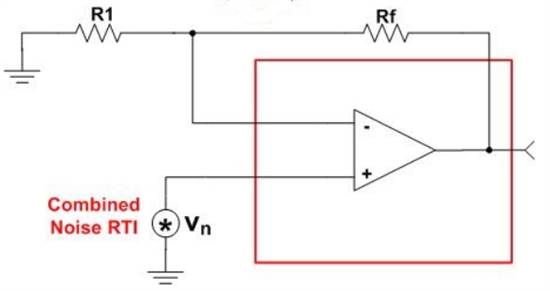

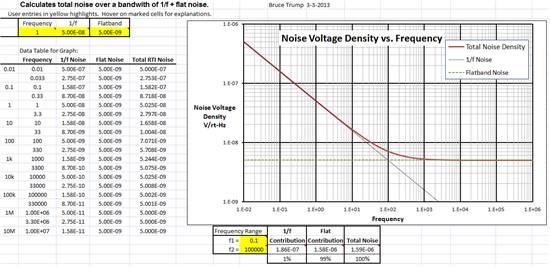

看上去好麻烦,不要急,还有更麻烦的事,就是运放的输入电压噪声和输入电流噪声,是与频率有关的,在极低频率时(0.1Hz-10Hz)主要是1/f噪声,以后主要是白噪声,如下图,

需要对其分段积分。

如下图是噪声电压的计算,只要输入1/f噪声在特定频率的值,和平坦噪声的值,就可以计算出不同频率下的噪声密度。输入频带的起止频率,就可以分析出这下频带内各个噪声的贡需率。

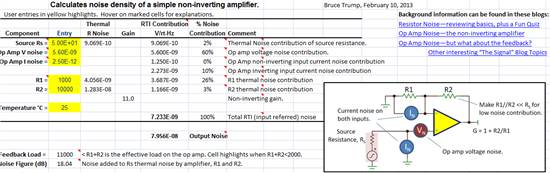

下图是计算同向放大电路的噪声密度的方法(以OPA627为例),只需输入信号源电阻,运放电压噪声,运放电流噪声,电阻值和温度,就可以计算出来输出电路的噪声密度,这大大提高了计算效率。计算结果同样给出了各个噪声源的贡需率,方便我们进行噪声优化设计。

5—电源抑制比DC-PSRR

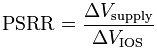

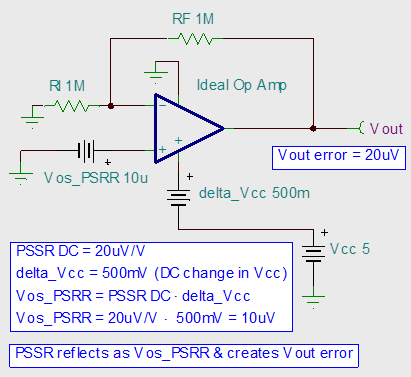

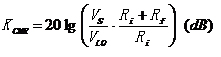

这一小节谈谈运放的电源抑制比。在理想运放中,运放的特性不会随电源电压的变化而变化。当然,分析理想运放时,我们使用的电源,也会被假设成理想电源。但实际情况并非如此,实际的运放,电源电压发生变化时,总会引起运放参数的变化。这就引出运放的一个重要参数,运放的电源抑制比PSRR。维基百科中给出了PSRR的详细定义,就是当运放的电源电压发生变化时,会引起运放的输入失调电压的变化,(又是失调电压),这两个变化的比就是运放的PSRR。如下式

通常用dB表示。PSRR = 20log(⊿Vcc/⊿Vios)。有些数据手册中,也会通过失调电压对电源变化的比来表示。单位一般用uV/V。如下图,是OPA365的datasheet中的表示,这个也不难理解。我们不用为找不到上式定义的比率dB值,而感动伤心。这两种表示方法,都可以让我们清楚的理解到运放对电源电压变化的抑制能力。

PSSR为有限值的原因,也是来源于运放差分输入管的不完全匹配。下面着重讨论它的影响。如下图是对OPA376运放的一个计算实例。当电源电压变化500mV时,就会引起输入失调电压10uV的变化,如果放大倍数为2,刚输出端变会产生20uV的变化。一些电路放大的倍数更大,则输出失调电压变更大。这足以使一个输送给16bitsADC的信号产生误差。(16位ADC的一个LSB对应的变化为15ppm of FSR)。

6—电源抑制比AC-PSRR

上面一节讨论的是直流DC电源抑制比。实际的应用电路中,运放的电源电压可能是不变的。

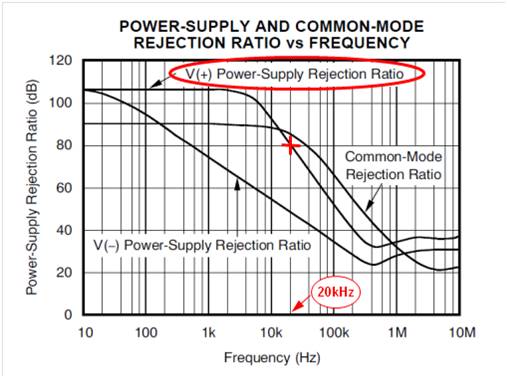

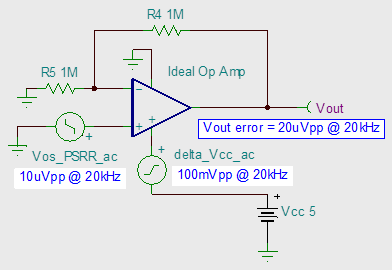

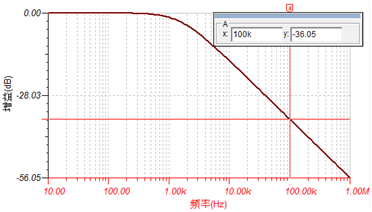

下面就来分析另一个关键的参数,运放交流电源抑制比AC-PSRR。这个参数相对在实际的应用电路中显得更有价值,却时常被我们忽略。运放的datasheet参数表格中往往给出的是直流PSRR。而AC-PSRR往往以图表的形式给出,我们常常忽略了图表中的信息。然而,被我们忽略的常常是关键。下图是OPA376的datasheet中的PSRR图表,从图表中我们可以看出两点信息:(1)PSRR是随电源交流频率的上升而下降的,(2)正负电源的AC-PSRR不同。

以上两点会在应用电路中引起令人不快的问题,下图是说明了一个在电源上出现的峰峰值为100mV,频率为20kHz的纹波,会使放大电路的输出端增加一个20uV,20kHz的噪声信号。

通常,运放的应用电路中使用线性电源对运放供电,对运放的电源进行滤波。但在一些手持式设备为了提高效率,降低功耗,不得不使用开关电源对运放供电,开关电源的频率往往超过100kHz,甚至到MHz的水平。在这个频率点上,运放的PSR能力下降的非常快。如OPA376在100kHz时,PSRR只有50dB了。与高于100dB的DC-PSRR相去甚远。另一个问题在单电源的手批设备中,开关电容的“buck-boost”常被用来将正电源转化为负电源。看到上图中运放对负向电源的AC-PSRR后,会让我们出点冷汗了。 运放的PSRR就要是指电源电压变化引起输入失调电压的变化。因此可以参照测量失调电压的方法测量PSRR。把电源电压变化一个⊿Vcc,然后测量计算⊿Vios,就可以计算出PSRR。

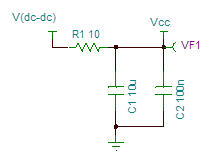

上面提到运放使用开关电源供电时,由于PSRR随频率的上升而下降。使得运放在输出端有很大的纹波噪声。下面提供一个简单的办法,只适合于低功耗的运放。在DC-DC输出的电源与运放的电原之间加一个小电阻(如下图),如果运放的功耗小于5mA。则这个10欧电阻产生的压降小于50mV。

下面看一下这个电路的效果如下图,在100kHz时频响为-36dB这相当于给运放增加了36dB的PSRR。这个功耗损失换取这个效果还是很值得的。

另一个有效的方法是,使串心电容给电源滤波,串心电容是一种三端电容,但与普通的三端电容相比,由于它直接安装在金属面板上,因此它的接地电感更小,几乎没有引线电感的影响,另外,它的输入输出端被金属板隔离,消除了高频耦合,这两个特点决定了穿心电容具有接近理想电容的滤波效果。关于串心电容,感兴趣的可以查阅相关资料。

7—共模抑制比CMRR

运放的共模拟制比,是常被大家关注的一个运放参数,尤其是在差分放大器和仪表放大器中。但这一小节只讨论运放的共模抑制比,以及CMRR带来给运放的误差。关于差分放大器和仪表放大器,以后另文讨论。

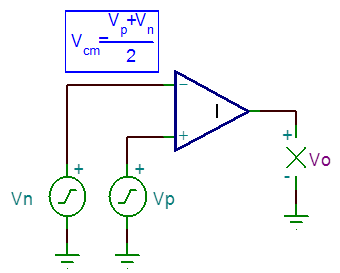

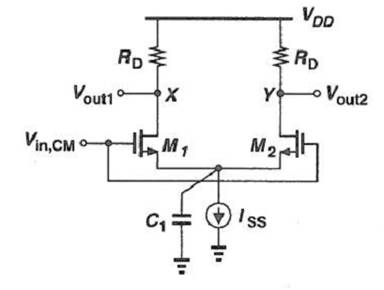

在开始讨论运放的共模抑制比,我们先了解一下运放的共模输入电压,运放的共模输入电压是指运放的两个输入引脚电压的平均值,注意是“平均值”,这一点很重要,如下图所示。对于双极性输入级的运放,运放的共模输入电压,一般达不到电源轨。而有些rail to rail输入运放的共模电压是可以达到电源轨的。

在理想运放中,运放的差模放大倍数为无穷大,共模放大倍数为0。理想总是美好的,现实总是残酷的。因此实际运放确不是这样的,实际运放的差模放大倍数也不会是无穷大,共模放大倍数也不会是零。我们就这样定义运放的共模抑制比(CMRR),差模增益与共模增益的比,如下式

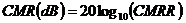

还有一个参数非常常见,就是CMR,它其实是CMRR的对数表示,如下式:

不过这两个参数经常被混用。我们只要了解他们都是在表示,运放对共模信号的抑制能力就可以了。

运放只所以会对共模信号能够进行放大,当然这是我们不期望的,但也是不可避免的。主要来源于下面几个原因:

(1) 运放差入输入级的不匹配。这又可分为以下的原因引起的不匹配:

1) 源极或漏极电阻的不匹配,

2) 信号源电阻

3) 栅极-漏极之间的结电容

4) 正向跨导的不匹配

5) 栅极漏电流

(2)拖尾电流源的输出阻抗

(3)拖尾电流源的寄生电容会随频率的变化而变化

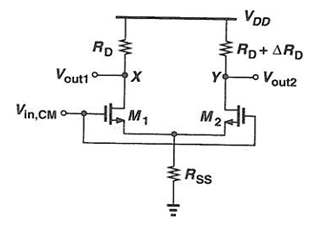

下面我们就挑几个上面的原因看一下它们的影响:

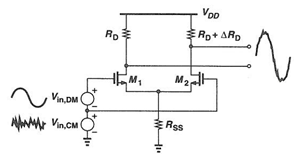

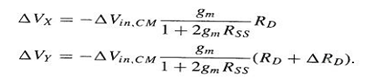

(1) 电阻的不匹配,如下图所示,由于电阻的不匹配,一个共模电压的变化ΔVin,会在X,Y点转化为一个差模电压。

计算如下,这个由失配阻ΔRd引入的差模信号,就会转化为差分级输出信号的噪声。

(2) 输入晶体管的不匹配,管子的不匹配,会引起两管子的电流的微小差别,并且两个的跨导是不一样的。

由于输入级管子的不匹配,会将共模信号转化为一个差模的误差,可以用下面的公式表示,它表示失配跨导引起的CMRR。

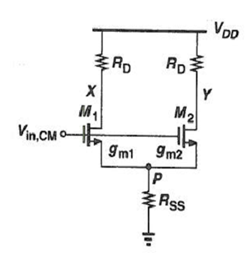

(3) 再介绍一个原因,就是拖尾恒流源的寄生电容会随频率变化而变化。这会引起这个恒流源电流的变化,差分输入端射极或源极电阻用恒流源代替的目的是保持电流恒定和高阻抗。但它的电流如果随频率发生变化,势必降低差分输入端的共模抑制能力。

8—共模抑制比CMRR的影响

上一小节简单介绍了,共模抑制比的定义,以及引起它的原因。下面就介绍一下,它的影响。本系列贴子的目的是说清楚运放参数的定义,分析引起这个问题的原因,介绍明白这个参数对电路的影响,最后尽力介绍一些经验方法来尽可能的减少和避免这些影响。

简单来说,CMRR是运放的一个直流精度参数,它的好坏,会引起运放的放大电路的输出误差的好坏。

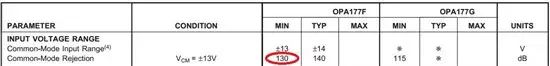

下表是OPA177的datasheet中标出的共模抑制比CMRR,注意表中标定的值是指,在输入共模电压范围内的直流共模抑制比。它的最小值为130dB,是非常高的值。

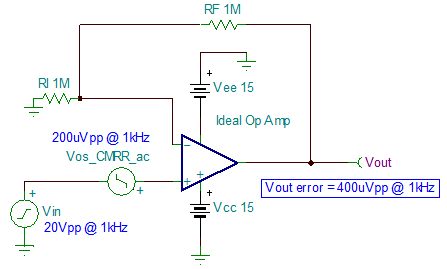

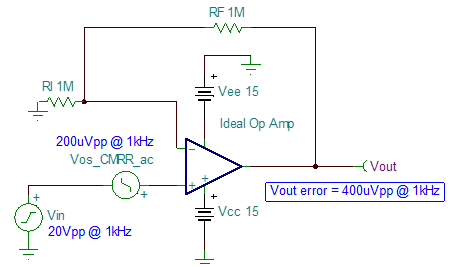

由于CMRR是有限值,当运放输入端有共模电压Vcm时,它会引入一个输入失调电压,我们称之为Vos_CMRR。如下图所示

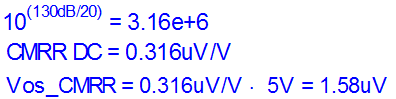

当共模电压为5V时,这个失调电压为1.58uV。计算过程如下,直流共模抑制比转化为比率为:

对于上图中的G=2的电路,则输出端误差为3.16uV。对于基准源为2.5V,双极性输入的24位ADC来说,为相当于引起了11个LSB的直流误差了,直接影响到最后四位的精度了。

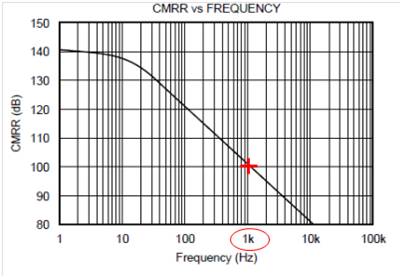

下面介绍另一个不好的影响,运放的CMRR是随频率的增加而降低。Datasheet中通常会给出一个曲线图来表示这一变化。如下图,这一点是一个非常令人不爽的特性。

我们可以计算一下这一特性的影响,如下图所示,当共模信号为一个20Vpp@1KHz的正弦信号时,它引入的输入失电压将是Vos_CMRR_AC=200uV@1kHz。对于Gain=2的放大电路,它的输入误差信号将为 400uV@1kHz。

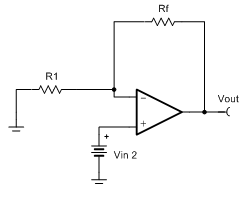

有一点需要引起注意,对于反向比例放大电路,如下图,它的同向端是接入到地的,由于“虚短”。此放运放的共模信号将为0,并且不随信号的变化而改变。因此共模信号引起的误差很小。

而对于同向比例放大电路,如下图,它的同向端是接是接的信号,由于“虚短”。此放运放的共模电压就是信号的电压。如果信号本身是一个频率很高的信号,幅值也很大。那么由这个信号引 入的Vos_CMRR_AC执必会非常大。此时应选用在信号频率上 CMRR依然很高的运放。经过上面的分析,即使这样,Vos_CMRR_AC的影响可能也会是非常严重的。

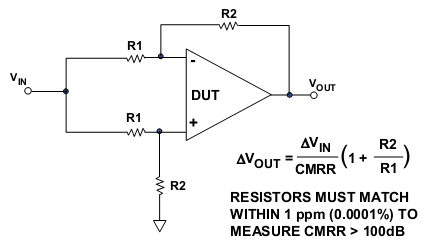

最后简单介绍一下运放的CMRR测试,通常人们会想到有下图的方法来测试CMRR,这种方法看似简单,但存在一个很大的问题,就是它需要的电阻匹配度非常高,为发测CMRR>100dB的运放,需要1ppm以下的电阻。这几乎不实用。

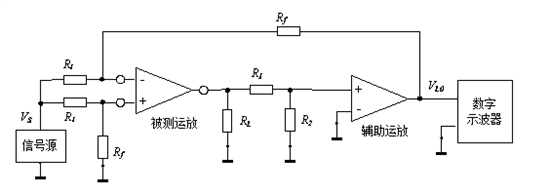

简单易行的方式是下图的方式。它对电阻的匹配度要求要低的多。

设信号源输出电压为VS,测得辅助运放输出电压为VL0,则有

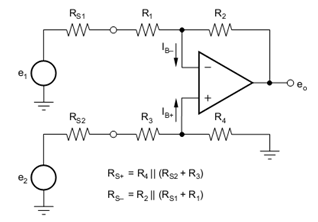

9—放大电路直流误差(DC error)

在本系列主题的part1-part8中详细分析了运放的主要直流参数。我们分析它们的原因就是,它们会给我们的电路引入直流误差。本贴的主要目的是把影响运放直流误差的原因都找出来,并且说明了它是怎样影响的。以便工程师在设计精密放大电路时多加注意。

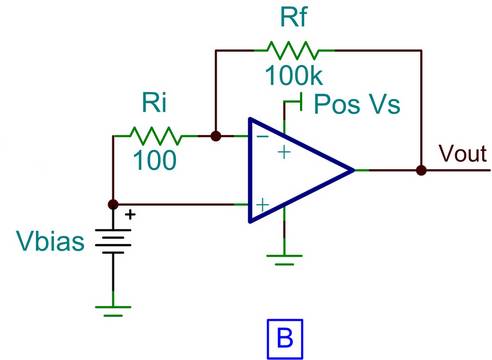

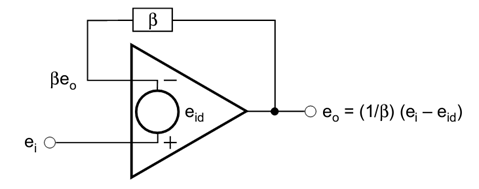

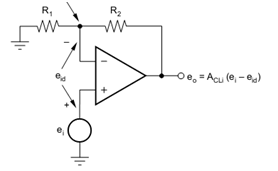

首先让我们看一下,同放放大电路的理论模型,如下图

这个电路在运放的应用电路中,再长见不过了。它的输出为eo. 等于闭环增益(1/β)乘以输入信号,这里的。输入信号我们要多加注意了,它是由电路的输入信号ei减于运放引入的误差eid构成的。式中β是反馈系数,对于像下图这样的典型同向放大电路,它的值就是R1/(R1+R2)。这在模电课本中都有详细叙述,不过多啰嗦。本文更要关注的是eid。

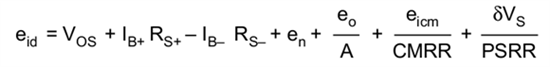

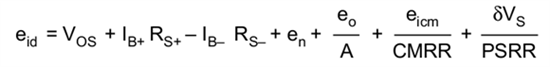

对于eid,我们的第一反应可能会是输入失调电压offset,再进一步的反应是输入偏置电流流过电阻网引起的误差电压。可事实,远不只这两个因素,它俩还有七大姑八大姨的都来凑热闹。那我们就展示出它的真面目:

上式等号右边的项够多吧。真没让我们失望,这么多参数,参于到制造直流误差的行列中。当然这些参数,也就是在part1-part8中提到的参数。

10— 放大电路直流误差(DC error)的影响因素

让我们再来认真看一下上一小节中提到的公式:

下面我们一项一项的来看看他们吧。

(1) Vos, 输入失调电压,大家都熟,不多废话。它更坏的一点是它不是一个老实待着的值,它会随着温度变化漂移呢。

(2) Ib+, 同向端输入偏置电流,它流过同向端等效阻抗,形成一个误差电压。

(3) Ib-, 反向端输入偏置电流,它流过反向端等效阻抗,形成一个误差电压。

有人可能注意了,输入端阻抗怎么计算呢。下面的图一看就明白了。简而言之吧,输入电阻(信号源电阻加输入端电阻)与反馈电阻的并联。千万别忘了信号源电阻哦,因为我们时常选用高阻抗的传感器做信号源。

(4) en, 等效输入噪声。这个值,我的理解可不只是datasheet中给定的en如1.1nV√Hz。它是集成了电压噪声,电流噪声和电阻噪声三都的贡献的。是所有噪声等效到输入端的值。具体请参照Art Kay的文章和本系列博文的part4。

(5) eo/A, 这个表达式,可能很多人从来没有关注过,有这一项的原因是,运放的开环增益A不为0。这也就是因为输入贴值的不同,而引起的等效输入误差的不同了,举个例子吧,如果输出值是5V。开环增益是100dB,不低了吧。它的折算到输入端的误差就有50uV啊。不是小数目了。

(6) eicm/CMRR, 这个不用多说,输入端的同模电压除以共模抑制比。又有一点不好的地方,运放的CMRR可是随共模信号频率的增加而下降的。好多运放的CMRR在共模信号到10KHz以上时,就比直流下降了几十个dB呢

(7) ΔVs/PSRR,电源电压的变引入的误差。同样的,交流PSRR在随频率的增高,而下降。

看了这些,可能还会以为,这点小误差是毛毛雨了,至多到mV级,甚至在uV级,不要忘了,它还要乘上一个增益Gain呢。假如输入误差是100uV。增益为100倍,则输出的误差信号,就是10mV。

Input_error x Gain = Output Error

如果还觉得没什么,那再讲一个经验值吧,一个满量程为5V的16位ADC的一个LSB约为75uV。只要75uV的误差就会引起ADC的一位的变化。假如放大电路的输出误差信号是1mV的话,这个信号给ADC,直接引起的误差就是13个LSB以上。

这个Output error,真是鱼龙混杂。有直流成份,这个可通过ADC采样后校正去除掉。有噪声信号,还有交流的成份。最不期望的,它还会随温度漂移呢。

我们在设计电路中,可以通过上面的分析,找出引起直流误差的主要因素,然后努力减小之。

审核编辑:汤梓红

-

运放参数的详细解释和分析-合集(1-25)2025-03-17 212

-

运放的几个参数分析2022-09-14 8744

-

运放参数的详细说明和分析2022-08-05 5593

-

运放参数的详细解释和分析合集2022-05-10 989

-

运放性能参数详解大全!!!2021-03-06 4708

-

运放的输入偏置电流和失调电流分析2021-01-06 2170

-

运放参数的详细解释和分析(1-25合集)2020-02-20 5774

-

运放参数的详细解释和分析:输入偏置电流和输入失调电流2018-10-31 10661

-

运放参数解释以及常用运放选型2017-11-27 91449

-

输入偏置电流和输入失调电流(运放参数的详细解释和分析)2016-11-12 7315

-

运放参数解释及常用运放选型2016-07-13 1592

-

【TI FAE分享】运放参数的详细解释和分析—输入偏置电流和输入失调电流2015-07-09 4413

-

运放参数的详细解释和分析_Wayne Xu2015-05-18 852

全部0条评论

快来发表一下你的评论吧 !