台积电公布3nm工艺真实数据 只比5nm高出5%

制造/封装

描述

台积电当前量产最先进的工艺是5nm及改进版的4nm,3nm工艺因为种种原因一直推迟,9月份就说量产了,又说年底量产,不过这个月就算量产,真正放量也要到明年了。

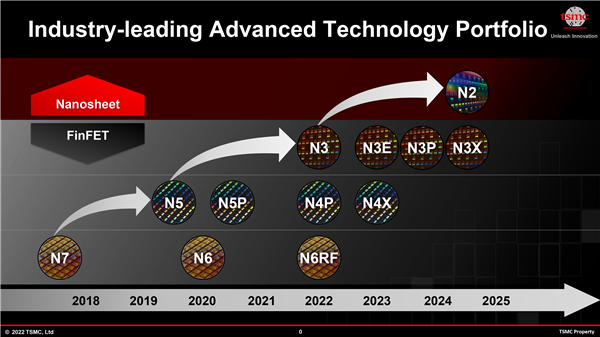

根据台积电之前的消息,3nm节点上至少有5代衍生版工艺,分别是N3、N3P、N3S、N3X及N3E,其中N3工艺是最早量产的,但是这版工艺遭到客户弃用,很大可能就放弃了,明年直接上N3E工艺。

对比N5工艺,N3功耗可降低约25-30%,性能可提升10-15%,晶体管密度提升约70%。

N3E在N3的基础上提升性能、降低功耗、扩大应用范围,对比N5同等性能和密度下功耗降低34%、同等功耗和密度下性能提升18%,或者可以将晶体管密度提升60%,密度上甚至更低了一些。

考虑到近年来摩尔定律一直在放缓,70%左右的密度提升看起来还不错,但这是台积电公布的最好水平,指的是纯逻辑芯片,SRAM缓存的密度就只有20%了,N3E还会更低。

然而20%的提升依然是理论上的美好,台积电之前在IEDM会议上公布了更真实的数据,3nm工艺的SRAM缓存在晶体管密度上只比5nm高出5%,指标大幅缩水。

尽管3nm工艺还有10-15%的性能或者25-30%的功耗改进,但是这些指标显然也是非常理想的情况,实际提升也会跟密度一样存在缩水。

但是3nm晶圆的代工价格上涨是实实在在的,传闻是2万美元一片,约合人民币14万元,比5nm工艺涨价至少25%以上。

而且14万元的价格还是基准价,如果厂商的订单量达不到台积电的要求,价格还会大涨,超过10万美元也很正常,也就是70万人民币了,这样的价格下芯片设计厂商的成本根本撑不住。

也难怪台积电在需求下降的时候依然想逆势涨价,但苹果强硬拒绝,反击台积电的理由就是苹果这几年的利润率一直没提升,台积电自己的利润率已经从50%提升到60%了。

编辑:黄飞

-

台积电5nm量产顺利,3nm工艺4月揭秘2020-01-22 7977

-

台积电最新公布5nm+/4nm/3nm工艺制程进度,推出超低功耗工艺N12e2020-08-25 11036

-

台积电5nm架构设计试产2019-04-24 4143

-

全球进入5nm时代2020-03-09 3639

-

台积电准备兴建新厂生产5、3nm制程2016-12-15 705

-

5nm和3nm工艺将是台积电未来几年能带来大量营收的工艺2020-10-23 2678

-

台积电3nm工艺将实现15%性能提升2020-12-21 2650

-

苹果已预定台积电3nm产能2020-12-23 2829

-

台积电3nm工艺进度超前 EUV工艺获突破:直奔1nm2021-02-19 3011

-

AMD已向台积电预订明后两年5nm及3nm产能2021-06-26 847

-

3nm工艺指的是什么 3nm工艺是极限了吗2022-07-07 31509

-

台积电3nm和5nm同期良率相当,3nm将大量生产2022-12-30 2096

-

消息称台积电3nm/5nm将涨价,终端产品或受影响2024-07-04 1644

-

台积电产能爆棚:3nm与5nm工艺供不应求2024-11-14 1698

-

消息称台积电3nm、5nm和CoWoS工艺涨价,即日起效!2025-01-03 1331

全部0条评论

快来发表一下你的评论吧 !