16位16MS/s SAR ADC采用55nm CMOS进行片上校准

描述

作者:Junhua Shen, Akira Shikata, Lalinda D. Fernando, Ned Guthrie, Baozhen Chen, Mark Maddox, Nikhil Mascarenhas, Ron Kapusta, and Michael Coln

一、引言

逐次逼近寄存器(SAR)ADC已获得大量研究 过去十年左右的兴趣[1]-[9]。相对简单的架构由于 无需运算放大器即可重用硬件 更节能,更易于在进程之间移植。此外, 高级CMOS工艺中的电源电压调节对SAR ADC的影响较小 因为比较器只需要很小的输出摆幅来区分决策 从噪音。这与流水线ADC或Σ-Δ型ADC中的运算放大器不同。 电源电压降低意味着运算放大器输出摆幅小得多 由于固定电路开销压降,导致ADC大大降低 信噪比 (SNR)。

SAR ADC擅长的性能空间之一是高分辨率 速度相对较低。他们发现许多应用,从医学成像, 仪器仪表、工业过程控制等与西格玛三角洲相比 ADC,也非常适合低速空间,SAR ADC区分 本身具有一次转换一个样本的能力,其中 别人。此外,与 增量式Σ-Δ型ADC,尤其是当过采样比较低时 允许使用OSR,SAR ADC不需要太多信号后处理。

通常,精密SAR ADC [3]、[4]通常定义为16位和 更大,样本低于几毫秒/秒。一些作品[1],[2]推动了速度 进一步。他们使用 2 位/试用和流水线 SAR 架构 [7]、[10] 来加速 提高操作效率,但代价是增加设计复杂性和高精度 放大器。此外,这些ADC通常具有较大的采样电容 超过 20 pF 以实现超过 90 dB 的 SNR,这可能需要更高的功率 ADC驱动器比ADC本身[11]、[12]。最后,它们采用片外线性度 校准 [1]-[4] 需要大量的测试时间并需要额外的成本。

随着片上系统 (SoC) 解决方案越来越受欢迎,努力 为了降低整体系统成本,并提高系统性能, 上述精密SAR ADC由于其大容量而无法满足需求 占地面积大,驾驶难度大,测试成本高。此外,他们中的大多数 采用 0.18 μm 等较旧的工艺,这对于 SoC 芯片来说并不理想,因为它们 重要的数字内容。本文介绍的工作描述了一种精密SAR ADC 在55纳米CMOS中解决这些问题,这在[13]中首次报道。是的 在精密 ADC 类别中速度快,可实现更多的 ADC 输出平均,其中 需要,这反过来又允许人们进行更嘈杂的个人转换,从而 采样电容大幅减小。例如,用户可能平均 该 ADC 输出 16 次,以达到 90dB SNR 目标。这项工作还具有一个 更小的占位面积以及片上校准使其非常适合 用于嵌入式应用。

本文的组织结构如下:在第二节中,建筑和街区级别 描述了设计。有助于实现此ADC的电路设计技术包括 第三节介绍,包括最佳LSB重复序列,一个储能电容 每位电容DAC、使用现有LSB电容进行校准和统计 残留物测量。实验结果见第四节 根据第五节的结论。

二、建筑与街区级设计

A. ADC 顶层

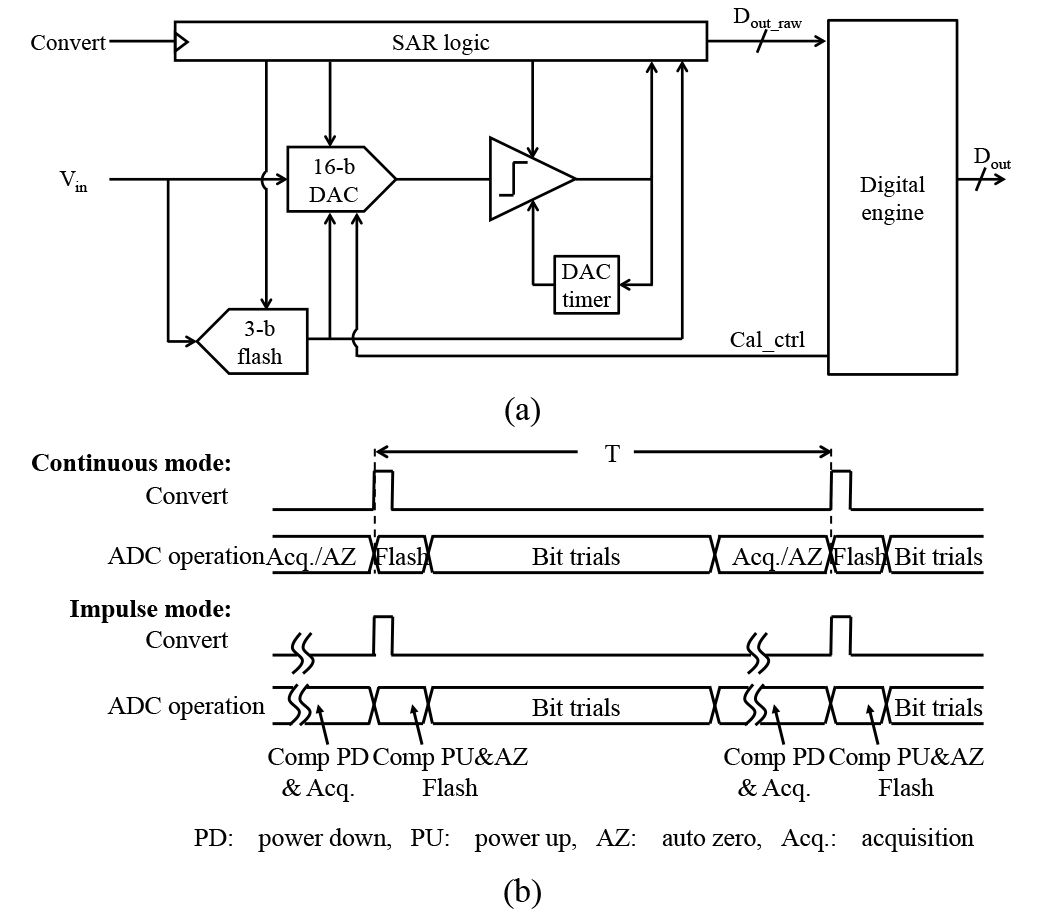

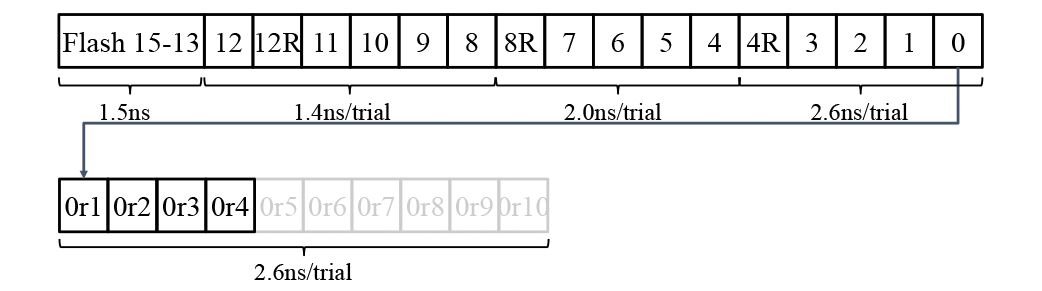

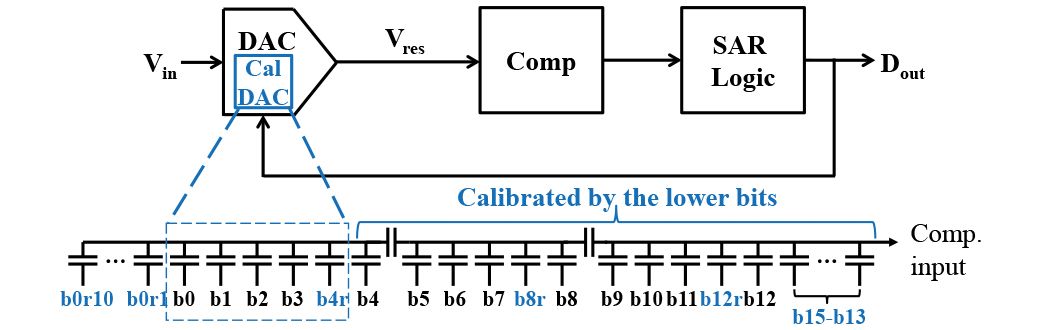

图1(a)显示了建议的ADC顶层框图。

图 1.(a) SAR ADC框图。(b) 转换时间。

它是一款完全自定时 16 位异步 SAR ADC [14]-[17],具有三个 MSB 由闪存子ADC解决。闪光灯加快转换速度并衰减 DAC输出显著缓解可靠性问题[17]-[19]。ADC 采样 网络,包括 16 位 DAC 和 3 位闪存块,但 闪存比较器,工作电压为3.3 V,以适应传统精度 应用方面,其余电路均在1.2 V电源下工作。数字化 引擎包括位重量校准和数据重建。ADC 工作 在两种模式下,如图1(b)所示。默认连续模式具有周期性 输入转换时钟。当转换信号出现时,闪光灯使MSB 决策和结果被馈送到DAC以开始位试验。在最后一点之后 试验结束,ADC进入采集阶段,此时自动归零也 在比较器上执行。下次转换时重复此过程 信号以已知的转换速率出现。另一种模式是脉冲模式, ADC 按需转换,之后进入非活动状态,同时 被动跟踪输入信号。在此模式下,转换信号消失后 激活时,比较器上电并执行自稳零。闪光灯 上电基准梯,并与比较器并联决定 自动归零。在闪存决策馈送到DAC后,它关闭。当所有 后续位试验结束,ADC关断并进入无源采集 相位,直到检测到下一个转换信号。此脉冲模式允许供电 当输入信号稀疏且应用程序稀疏时,随吞吐量进行扩展 不需要全速转换,例如许多环境或患者 监控传感器。虽然需要避免输入自举电路 在脉冲模式下,因为被动采集阶段可能会持续很长时间并且 自举电容器可能无法保持其电荷。要利用 55纳米深亚微米CMOS工艺,我们设计的ADC可以向上转换 达到 16 MS/s,这在精密 ADC 类别中非常快,但不是那么快 以牺牲SAR ADC效率。高速运行提供 用户可以选择进一步平均ADC输出数据以降低噪声。这反过来又 允许噪声更大的单个转换,因此采样要小得多 电容可显著减小面积。与传统精密ADC相比 运行速度较慢且依赖于精确的单个转换,该ADC可权衡噪声 速度保持相同的效率,但占地面积要小得多。

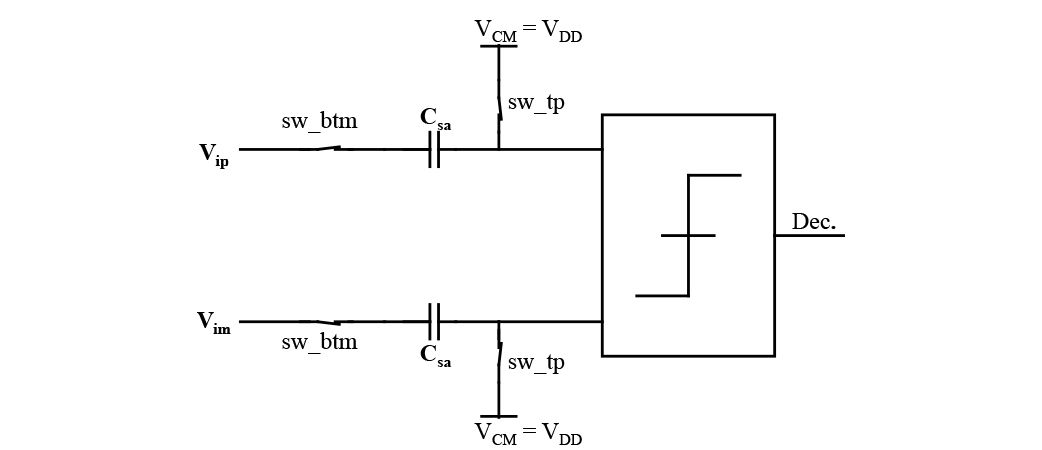

图 2.VDD 参考采样。

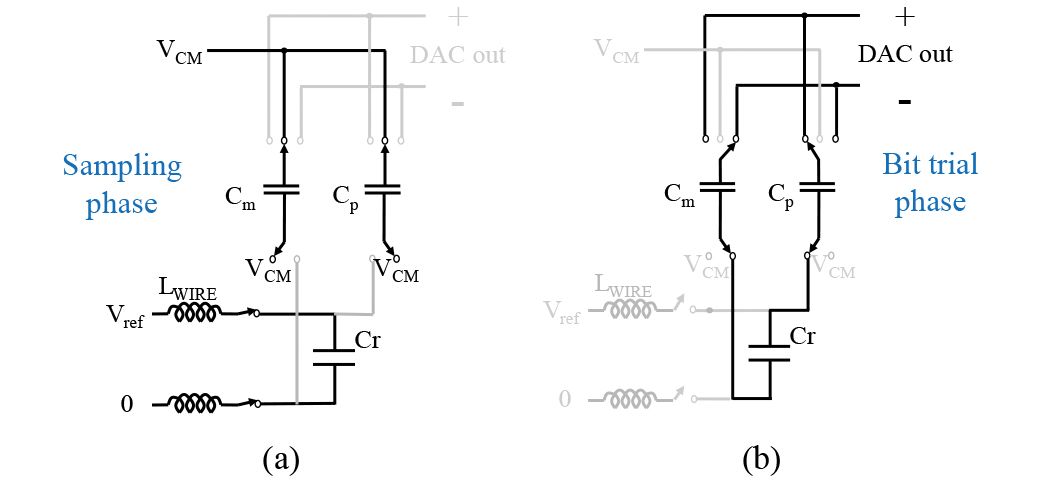

B. VDD 参考采样

前面提到的脉冲模式需要无源采集,因此 ADC在跟踪输入信号时不消耗任何有功功率,并且 等待下一个转换信号到来。VDD 参考采样技术 引入以实现这一点。图2显示了采集中的采样电路 比较器关断时的相位。为了不消耗任何活动 电源,我们不能使用有源电路来产生共模(CM) 电压 V厘米如图所示。解决此问题的传统方法是拆分 每个采样电容C南非分成两半,连接一半顶板 到 VDD,另一半到 GND。收购后,二者的顶板 两半短路在一起以实现VDD/2 CM电压。缺点 这种方法增加了布局布线的复杂性和由此产生的寄生效应。 此外,它还需要一个额外的时钟相位来使两个顶板短路。在 这种设计,我们利用了DAC输出或比较器的事实 输入摆幅仅为ADC V的1/8裁判得益于闪存子ADC的分辨率 假设 V裁判为3.3 V和一定数量的DAC 由于负载电容器引起的输出衰减,我们只有大约 ±150 mV 每个比较器输入端的最大摆幅。这样就可以使用 VDD 电源,通常调节良好,以取代 对DAC进行采样,从而避免了额外的CM发生器会消耗功率。 比较器输入端的瞬态电压高于150 mV,可能会导致顶板采集开关出现短暂泄漏。消除大部分这种潜力 漏电我们可以使用由核心控制的高阈值内核PMOS开关 电源,或使用由 IO 电源控制的 IO NMOS 交换机。后者是 在此设计中实现。稍高的摆动不会造成可靠性 与比较器的输入对有关,这将在比较器小节中介绍。

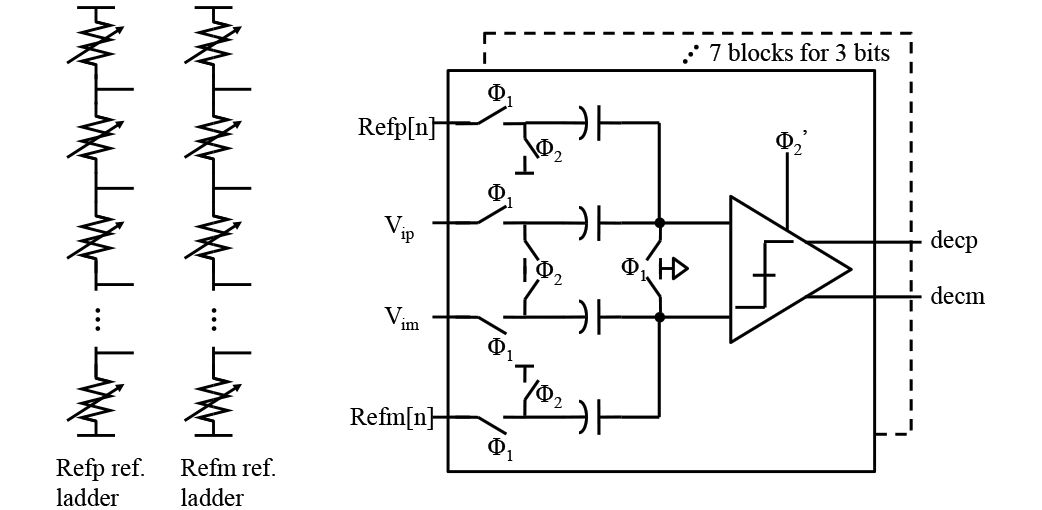

图 3.闪存子ADC框图。

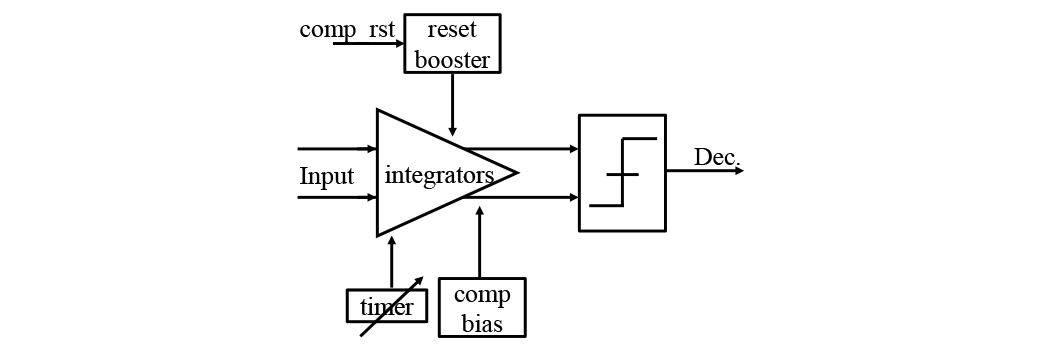

图 4.SAR比较器框图。

C. 闪存子模数转换器

闪存子ADC可解析三个MSB,主要作为在增加之间的权衡 复杂度和DAC输出衰减量。在此设计中,如 图3,电阻梯用于生成闪光基准和基准 电平抖动以匹配 SAR DAC 抖动,其相当于 B12重量。抖动用于改善ADC线性度[20]。七个闪光比较器对ADC输入(高达6.6V)进行采样PP,差异与 V裁判= 3.3 V)和基准电压源 采集阶段 Φ1 ,之后立即在 Φ24 ¾2' 是 Φ2 的略微延迟版本。比较完成后大致 1.5 ns,决策馈送到DAC、比较器和电阻梯 关闭以节省电源。由于SAR DAC具有内置冗余,因此 闪光比较器失调和噪声并不重要,只要得到的决定 DAC冗余涵盖错误。我们分配 1/4 的冗余 以容忍闪存决策错误。因此,设计了闪光比较器 速度和功率,以最大限度地提高其效率并最小化开销。

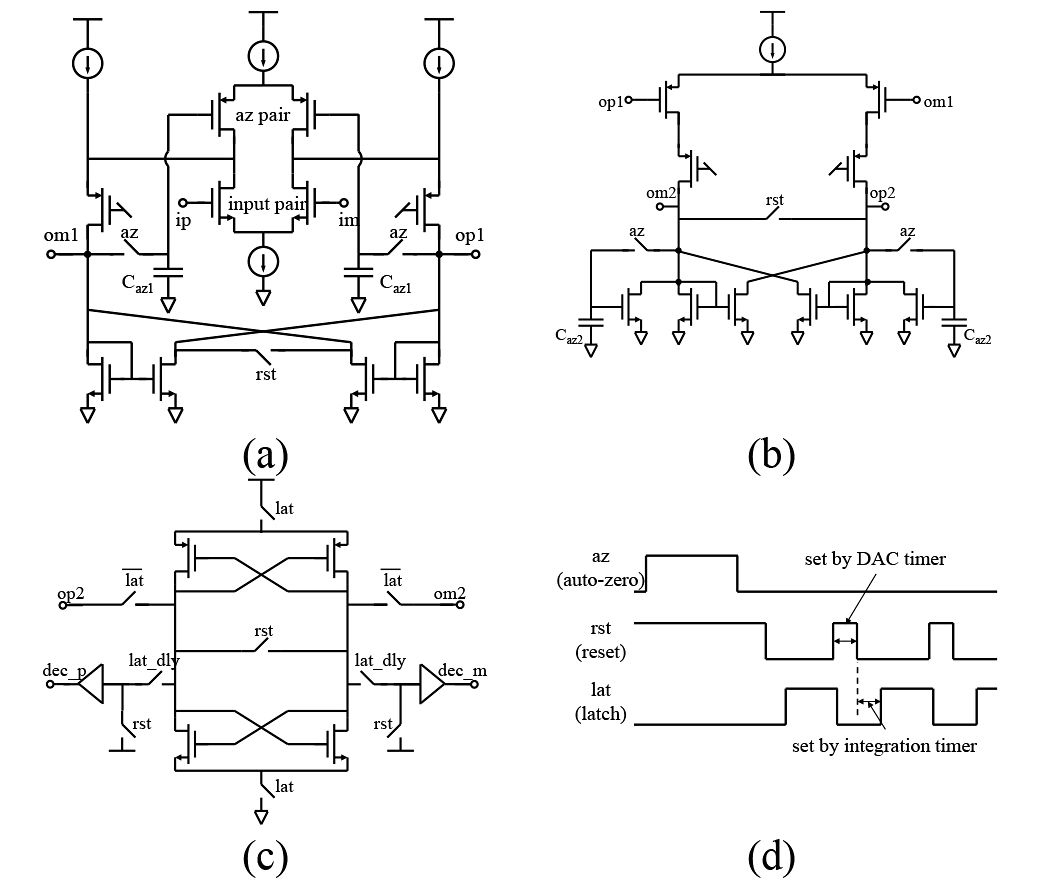

D. 搜索和救援比较器

比较器在功耗、噪声、速度和可重构性方面是一个关键模块。图4显示了比较器的框图。集成商 锁存器之前由可编程定时器控制以交易积分 速度与噪音。比较器复位信号comp_rst被升压,以确保 在两次比较之间,记忆效应可以忽略不计,即使 比较器输入有一个很大的阶跃变化。图 5 显示了两个积分器 载物台原理图和闩锁载物台。使用交叉耦合正反馈 对于两个积分器负载,以最大限度地提高直流增益并消除对 共模反馈电路。两个级均自动归零,以最大限度地减少精密应用中的失调和1/f噪声。自动归零阶段 图5(d)所示与ADC采集相位重叠,均为积分器 级将失调信息存储在自稳零电容C上亚利桑那州在此期间 相位,而积分器的输入差分短路。两个阶段是 用于(而不是一个)以实现更宽范围的积分增益与时间的关系。 第一个积分器级采用折叠式级联结构,使 使用VDD作为其输入CM。 仿真表明,输入对可以处理 至 VDD +400mV 瞬态输入,而不会对晶体管施加压力,作为源 输入对的节点主要跟踪比较器输入。

图 5.SAR比较器原理图和工作时序。(a) 第一集成人阶段;(b) 第二阶段整合者阶段;(c) 闩锁;(d) 行动时间。

比较器噪声是ADC转换噪声的主要来源。我们 设计了两个积分器级的稳态增益,使其足够 高,以便它们以积分模式而不是线性建立模式运行 实现更好的噪声性能 [21]。每个积分器的增益在 以下等式。

其中gm由输入对主导,C为负载寄生电容 (未绘制)在图 5(a) 和 5(b) 中的 op/om 节点处。折合到输入端的噪声功率 与输入对的GM和积分时间t成反比,如图所示 在(2)中。γ因素解释了晶体管的过度噪声,而不是 输入对。

请注意,自动归零操作会影响整体kT/C采样噪声, 这也在设计中得到了考虑。实现的比较器具有 估计噪声约为 180 μV有效值.

图 6.(a) 发援会结构;(b) 简化位电容操作。

图 7.具有优化试验组的位试验。

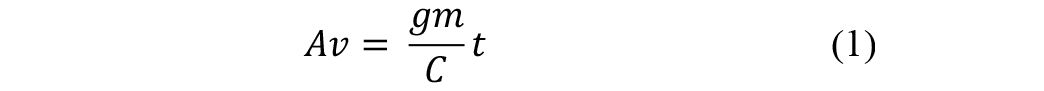

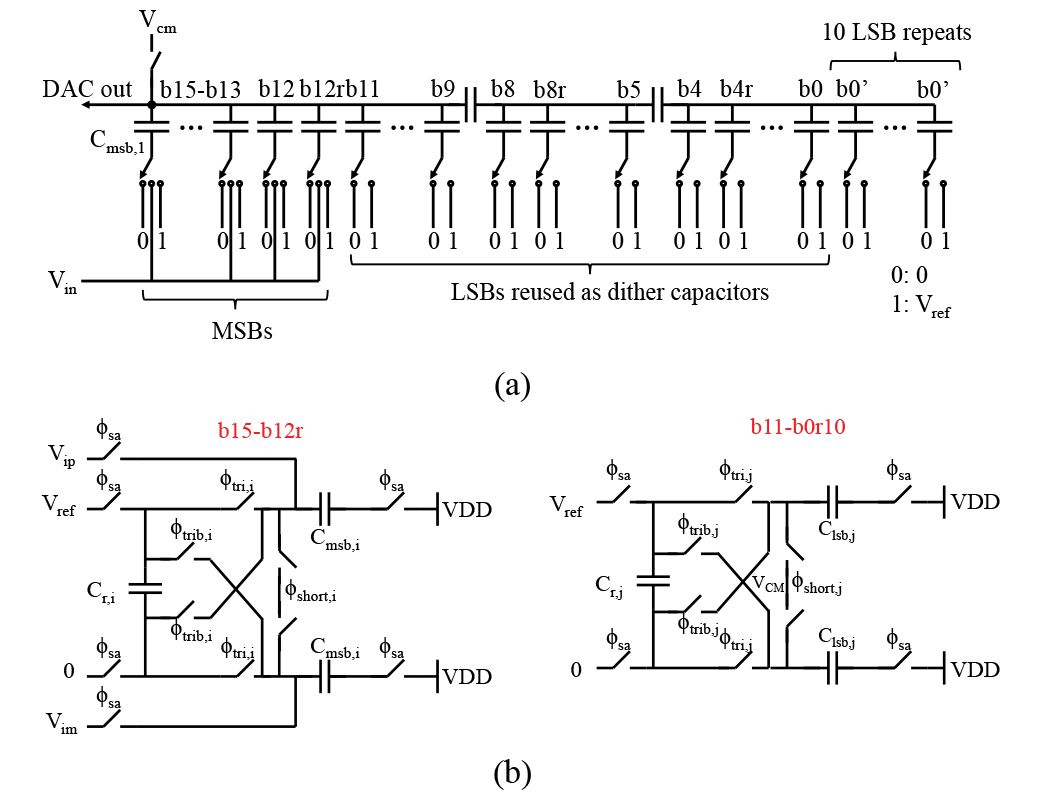

E. 发援会

图中显示了具有三个电容阵列段的电荷再分配DAC 在图6(a)中。三个段用于减少每个段中的电容分布 段并启用 8-fF 单元电容器。DAC采样电容 距离 b15-b12 和 b12r 仅 1pF,大大简化了输入驱动器和 参考缓冲区要求。三个冗余电容器(b12r、b8r、b4r)是 包括允许闪存子ADC及更早版本的决策误差[22]、[23] 位试用。在轨道阶段,电容b11-b0不对输入进行采样, 而是对随机抖动值进行采样以提高线性度。高达 10 LSB 包括重复以改善噪声性能,在 中详细介绍 第三节-A.图6(b)说明了采样和非采样的操作 电容器。采用每位电容一个储电容DAC电池结构 以加快操作速度并实现与信号无关的位权重误差。是的 在第三-B节中进行了深入的解释。

对于SAR ADC,较早的位试验不太重要,因为比较器 输入通常远大于转换噪声电平。[24] 和 [25] 采取 通过将比较器前置放大器负载电容更改为 降低早期试验的功耗,同时不牺牲整体功耗 噪声性能。在此设计中,我们可以进一步优化位试验,使用 示例设置如图 7 所示。鉴于 b8r 采用的冗余和 B4R,我们将位试验分为图中所示的几组,并设置两者 更小的位电容建立时间和比较器积分时间较短 组。由此产生的建立误差和较高的比较器噪声被冗余位所容忍。

图 8.LSB在存在噪声时重复。

三、电路设计技术

A. 最佳 LSB 重复序列

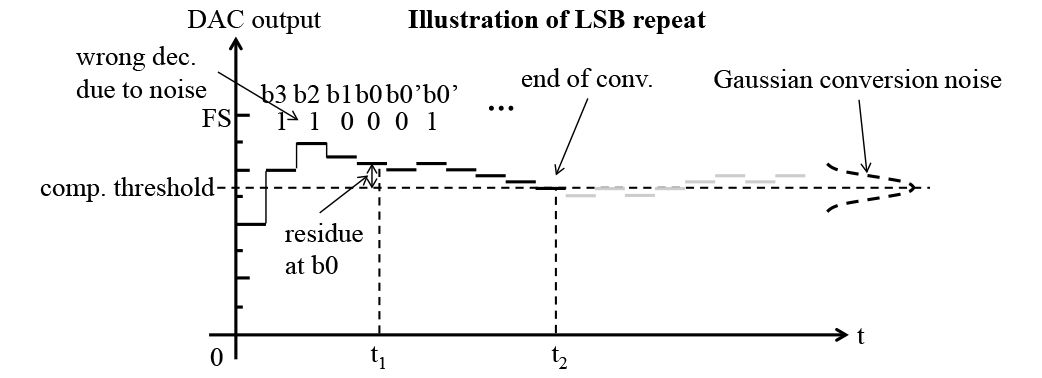

ADC噪声来自采集阶段和转换阶段, 大约为 130 和 250 μV有效值,分别在此设计中。收购 相位噪声主要是kT/C采样噪声,是噪声之间的权衡 电平和面积,以及与驱动电容相关的功率。 噪声一旦被采样,通常无法消除。在这里,我们介绍一个 专注于降低转换阶段有效噪声的技术 只。转换噪声主要影响SAR比较器决策 源自比较器、基准和串联开关R上和 比较器输入端的布线电阻。从(2)或[26],我们知道它 假设电流效率,需要 4× 的功率才能将比较器噪声降低 2× gm/I 保持不变。在[9]、[27]和[28]中,比较者决定多数投票 用于关键位试验,其中比较器的输入非常小,以减少 转换噪声。该技术需要一个检测电路来识别关键 钻头试验,往往对工艺、电压和温度 (PVT) 敏感 变化。在 [29] 中,提出了一种自适应平均技术,其中 b0 是 重复8次。它将前几个 LSB 重复位试验视为冗余试验 纠正较早的DAC建立误差,并对其余重复决策求平均值 在LSB重复期间检测到01或10跃迁后。有效性 由于存在转换噪声,这种检测受到限制。

在这项工作中,提出了一种优化的LSB重复技术来降低噪声。这 B0 决策最多可以重复 10 次,具体取决于转化率和 噪音要求。与[29]不同的是,我们报告重建ADC LSB重复位被认为等效于其他位的输出产生 更好的噪声性能,即最终ADC输出是所有 试用位,包括重复位。图8示出了建议的LSB重复序列 使用 4 位示例的技术。在存在转换噪声的情况下,b2 使 错误的决策,DAC输出包含大于1 LSB的残余误差 在常规 B0 试验之后。随着后续LSB重复,残余误差将 被下拉,因为平均转换噪声为零。经过多次LSB之后 重复上述操作时,DAC输出将开始围绕比较器门限移动。

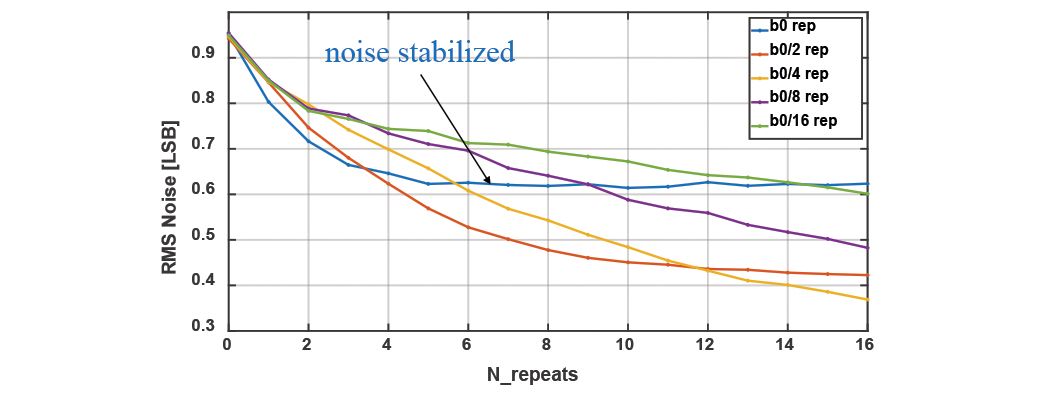

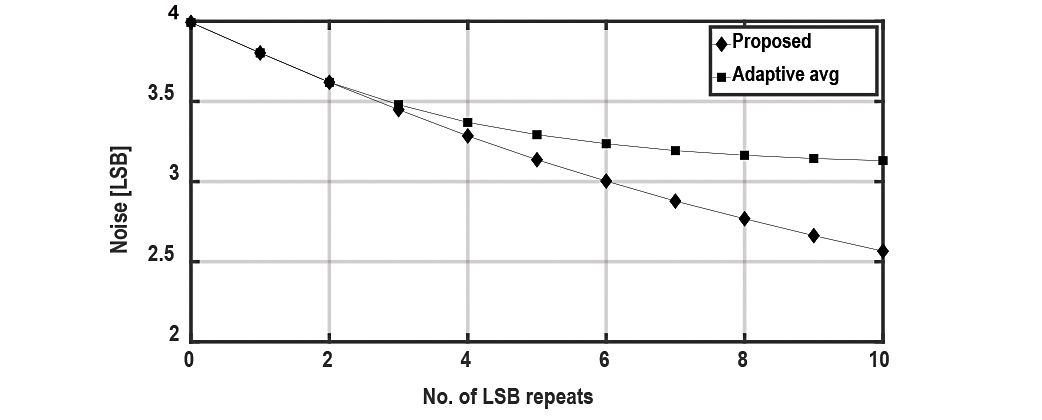

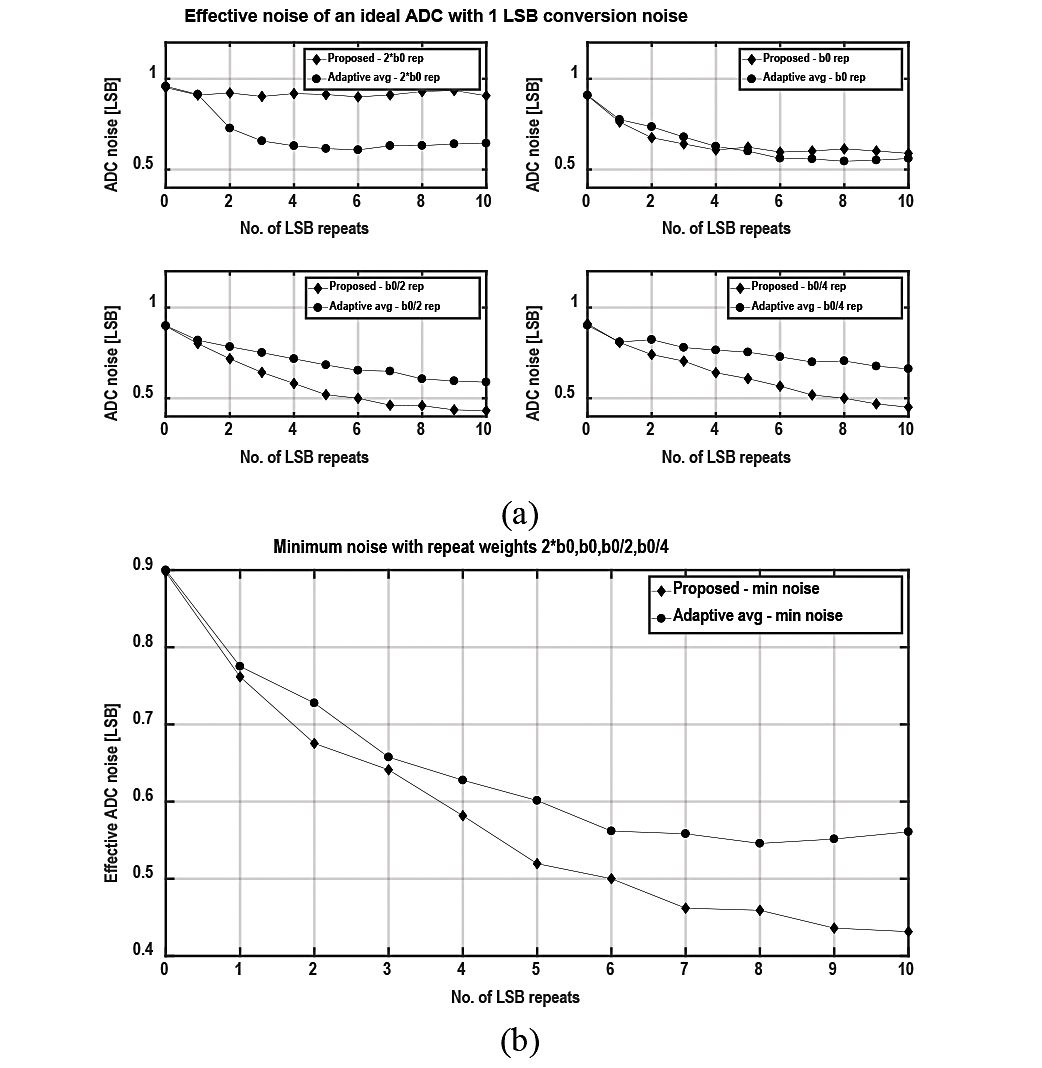

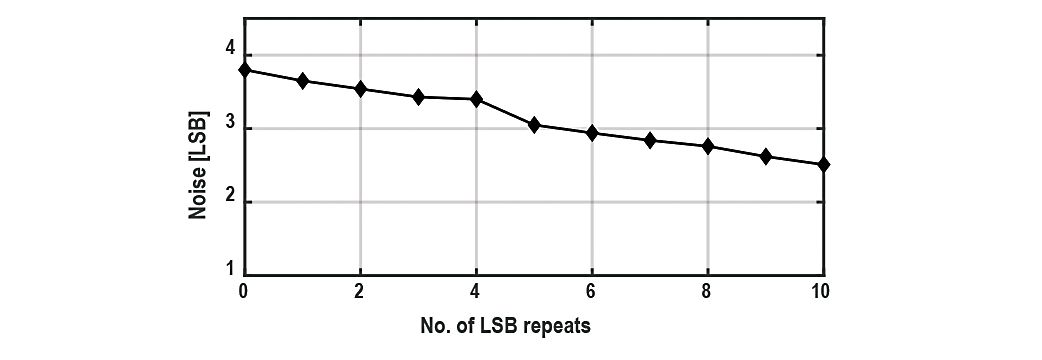

图 9.仿真ADC噪声与不同权重的重复次数的关系

图例.10. 品质因数(FoM)增益与重复次数的关系

此外,LSB重复不会改善转换噪声,并且最佳 LSB重复次数可以确定,给定转换噪声电平和 重复位权重。图9显示了有效ADC噪声与有效噪声的仿真结果 重复次数,在五种不同的重复位权重设置下。该模数转换器是理想的选择 除了一个LSB标称转换噪声。我们观察到,根据 可用的转换时间,因此允许的LSB重复次数,有 存在最佳重复位权重,以获得最小的有效ADC噪声。为 例如,如果我们有时间进行四次LSB重复,则选择重复位权重B0/2 将产生比 B0 重量重复更好的结果。此外,如前所述,对于 给定重复位权重,有效ADC噪声将在多次 重复。在图9中,重复位权重的噪声稳定在大约5次重复 b0.重复位权重越小,有效重复所需的重复次数就越多 ADC转换噪声稳定。如前所述,此设计使用 b0 重复 因为它被发现是给定设计噪声的最有效的重复位权重 水平和速度。

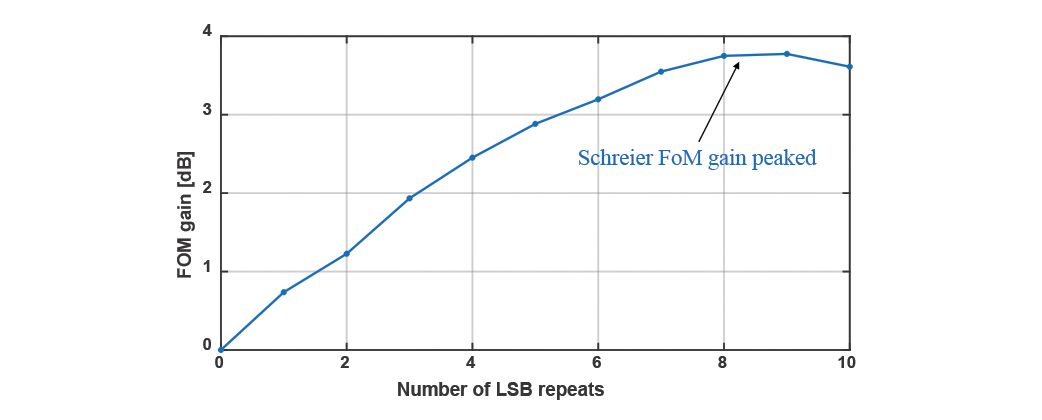

所提出的LSB重复技术基本上是用速度换取噪声,但 降噪远远超过效率方面的速度损失 或品质因数 (FoM)。图 10 显示了计算出的 FoM 改进 设计与可用重复次数,不考虑 采集噪声。图11还比较了该技术与该技术的测量结果 [29] 中的自适应平均算法。所提出的方法改善了噪声 进一步高达20%。在更一般的情况下,仿真结果如图 12 所示 以比较两种 LSB 重复算法。在此仿真中,理想的ADC 具有1 LSB的转换噪声。图12(a)显示了有效ADC噪声与 LSB 重复次数,在 2×b0、b0、b0/2 和 2 处具有 4 个不同的重复位权重 分别为 B0/4。然后,图 12(b) 汇总图 12(a) 的结果并挑选 这四种不同重复位权重中噪声最低。例如 两种技术均提供五个LSB重复序列,噪声最小 自适应平均为 0.6 LSB,具有 b0 权重重复和最小噪声 从建议是0.52 LSB,b0 / 2重量重复。图12(b)表明 所提出的最优LSB重复重复再次更有效,最高可达20%左右。

图11. 建议的最佳LSB重复和自适应平均的实测噪声[28],ADC转换噪声配置为主导采样噪声。

图 12.(a)使用最佳LSB重复和自适应平均[29]具有不同重复位权重的理想ADC的仿真噪声,以及(b)使用最佳LSB重复和自适应平均[29]可实现的最小噪声。

此外,由于没有对建议的最佳LSB重复应用平均,因此 可以处理重复后的DAC输出残余,以进一步降低噪声 和量化误差。这将在第三-D节中讨论。

B.每个位电容DAC一个储能电容

每次位试验期间的DAC建立或基准建立通常是 精密SAR ADC速度,特别是当基准电压源在片外提供时 通过芯片键合线 [30]。另一种方法是使用片上高速 基准电压缓冲器是以功耗过大为代价的。在 [15] 中 和 [17],片上储能电容器用作“参考”,以显着 提高DAC建立速度。图13说明了如何使用储能电容器 显著提高DAC建立速度。

图 13.储能电容作为参考,以加快位建立速度[17]。(a) 取样阶段。(b) 第二位试验阶段。

图 14.每个位电容一个储能电容。(a) 第一位试用图。(b) 第二位试验图。

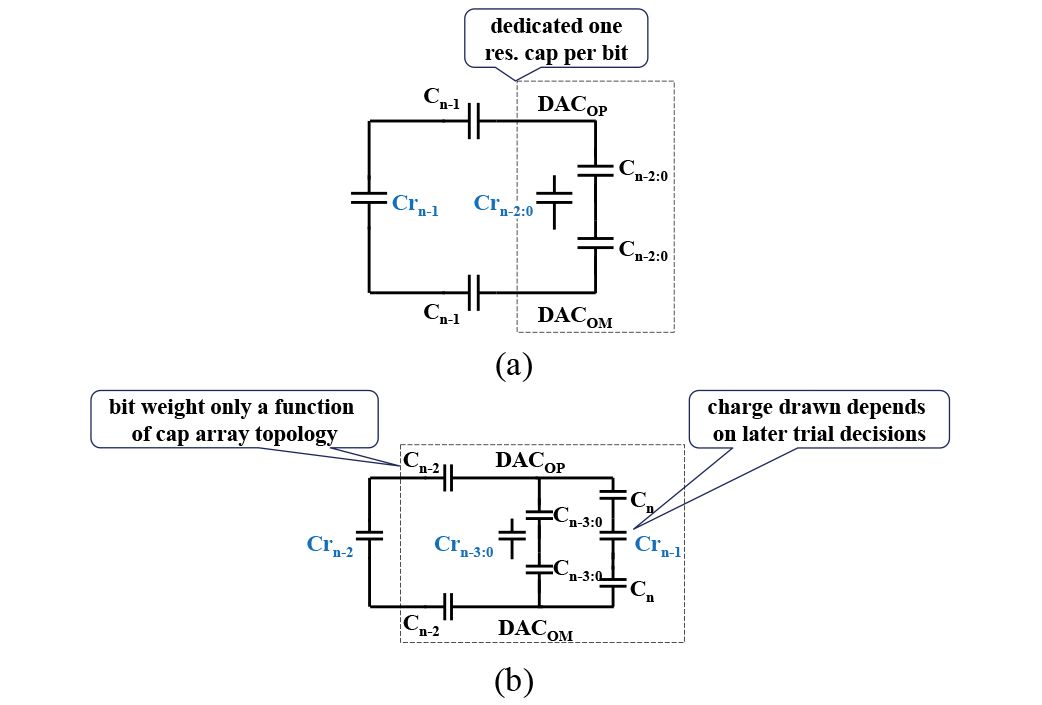

在采样阶段,储能电容Cr充电至: 参考水平。在位试验阶段,位电容 Cp 和 Cm 吸收 来自Cr的基准电压源电荷,而不是通过 键合线。这使得DAC建立速度更快,因为建立速度 仅受开关 Ron 和位电容的限制。然而,在两者[15] [17],储能电容器需要足够大,以便 由于电荷共享而导致的基准电压源误差降至最低。为了避免这种情况,在[17]中, DAC电容与采样电容分开,以确保电荷消耗 从储液电容器是信号无关的。这导致更大的面积,并且, 更重要的是,会降低噪声性能。在[13]和[3]中报告,我们 提出每比特电容器一个储能电容技术。这与 [15] 其中多个储能电容器切换到一个采样电容器; 以及[17],其中一个储能电容器与多个位电容器共用。在 这种设计中,一些位电容(B15-B12、B12R)也用作采样 电容器。与[15]和[17]中的电容器不同,每个比特电容器都是驱动的 在独特的预充电储能电容器进行位试验期间的基准电压源 [见图6(b)],其尺寸为相应位电容器的10×。这将是 稍后显示,该DAC结构产生与输入信号无关的位 砝码,可实现更直接的校准。因此,相对较小 使用储能电容器,减少面积并简化预充电,同时 保持全速优势。

图 15.采样电容器的操作。(a) 采集阶段的MSB电容器。(b) 转换阶段的MSB电容器。

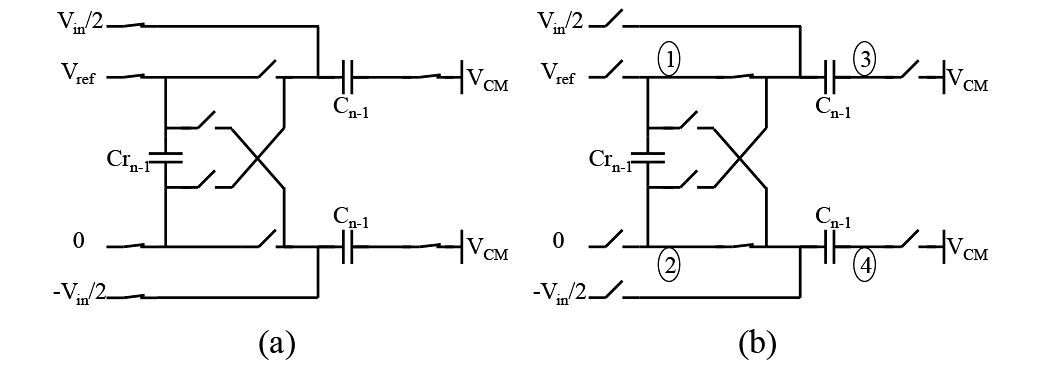

图14在概念层面说明了这种DAC结构如何实现信号 独立的位权重。图14(a)显示了简化的电容阵列 第一个比特试验,其中 CN-1是MSB电容器和Cr。N-1是对应的 储液电容器,CN-2:0是DAC中的其余位电容。若 位电容CN-1要么差分短路至 V厘米(一个选项 采样位电容)或复位至共模V厘米(对于非采样位 电容器)就在位试验之前,当预充电的储能电容器 铬N-1连接到位电容CN-1,它将产生一个DAC输出步长 代数转换器OP-数字转换器唵与输入信号或位决策无关。输出步骤 尺寸只是电容器比率的函数,作为Cr上的初始值N-1和 C 的左侧N-1与信号无关。图14(b)进一步说明了 第二位试验,其中储液电容CrN-1从第一个位试用现在是 部分负载电容器。这并没有改变DACOP-DACOM的事实。 对于第二位试验仍然是确定性的,只是步长由于 不同的负载电容值。与信号无关的DAC输出步长 在每个位试验中,基本上表示相应的位权重,因此这个 储电容每比特电容DAC结构导致信号无关 电荷共享中的位权重错误。一个有趣的观察是, 即使位权重与信号无关,从每个位权重中汲取的电荷 图14(b)所示的储能电容取决于决策或信号。

上述概念解释假设位电容短路至 位试用前的共模。在更一般的情况下,采样位 电容器的底板在位试验之前可能没有短路(如果有) 是一个单独的子范围 ADC,用于决定前几个 MSB。在这种情况下, 采样电容器的底板的初始值可能为 V在相反 固定 V厘米就在位判定应用于位电容之前。 我们将在数学上证明这仍然会导致信号独立位 权重。图15(a)显示了采集阶段的MSB电容,图15(b) 显示了 MSB 在位试用期间的情况。未显示DAC输出负载电容 在数字中。为简单起见,我们首先假设只有 MSB 获取 来自储能电容器的基准电压源,这可能会导致基准电压下降,原因如下: 费用分摊。所有低位都有理想的基准电压源。应用费用 在采集阶段结束之前节点 1 和节点 2 上的守恒规则 在转换阶段结束时(节点 3 和 4 收敛到 V厘米如 好吧),我们可以得出以下结论:

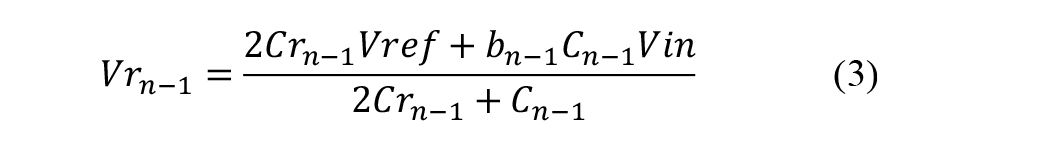

其中 VrN-1是储能电容上的参考压降Cr。N-1之后 电荷共享,V裁判是理想的基准电压,BN-1是位判定+1 或 -1。我们看到 VrN-1与输入电压 V 成正比在.MSB 权重在 因此,转换结束与 Vr 成正比N-1因此 V在:

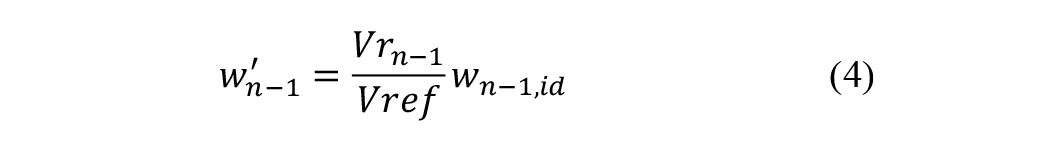

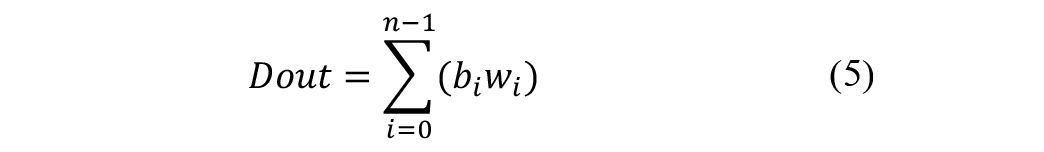

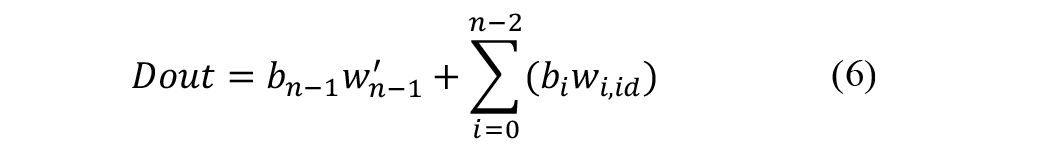

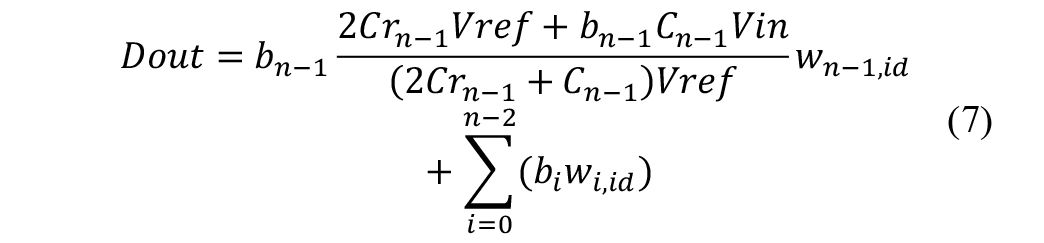

其中 wn-1,ID是仅由MSB电容值定义的理想重量。这 聚合 ADC 输出 D外定义如下:

其中 b我是位决策 ±1, W我是对应的半位权重。然后我们有 D外如下所示,因为我们假设除 MSB 之外的所有位权重都是理想的:

将 (3) 和 (4) 插入 (6),我们得到:

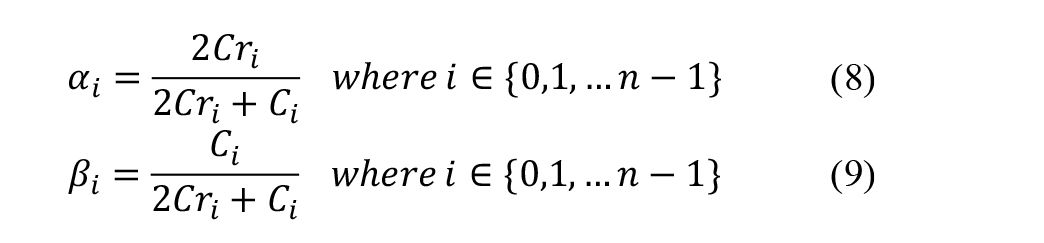

我们可以进一步定义α我和β我如:

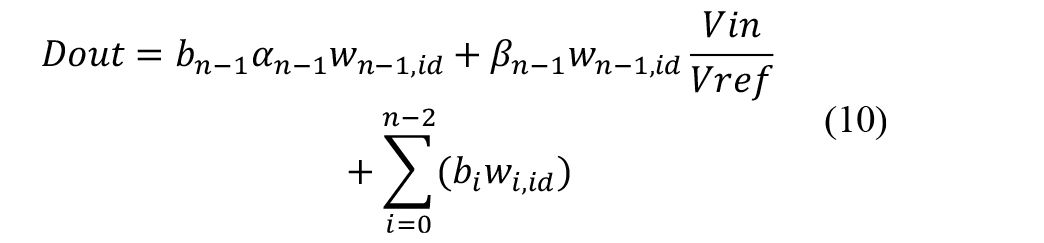

所以我们有:

根据定义:

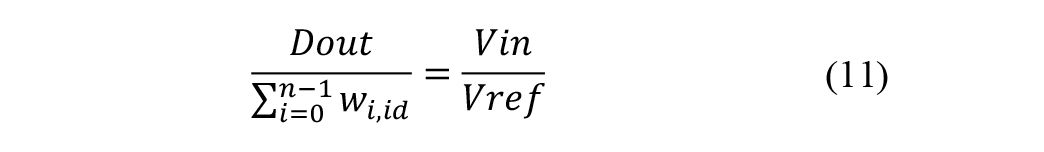

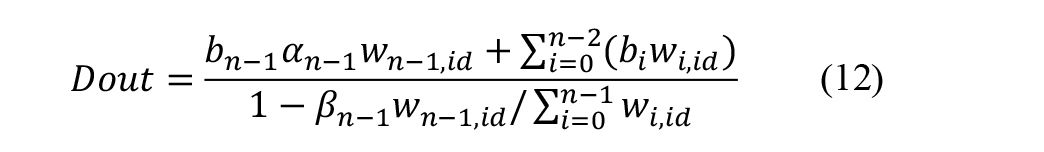

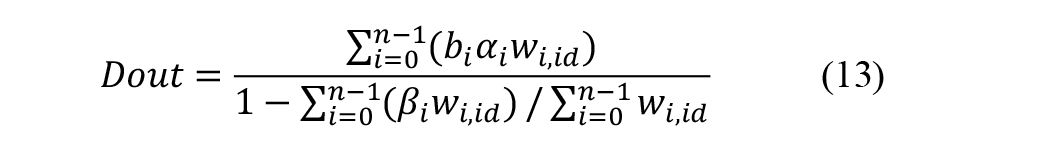

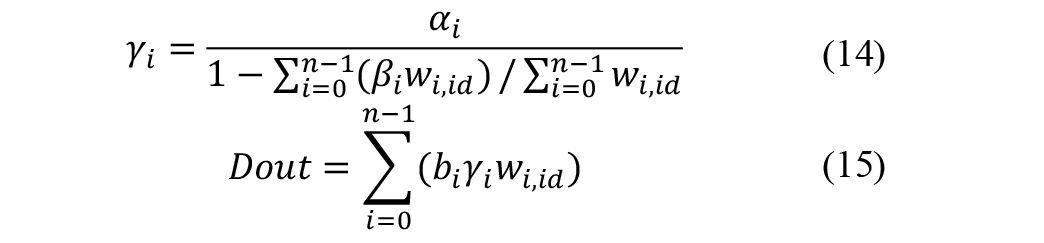

求解(10)和(11),我们得出:

我们看到 D外即使 MSB 有信号,也有效地与信号无关 相关基准电压下降如(3)所示。和有效MSB位重量 不依赖于 V在,不像 wN-1'在(4)中。从上面的推导中概括出来, 现在让我们假设每个位电容都有其对应的储能电容 SAR DAC,我们将得出以下一般公式:

实际上,每个储能电容器的电荷共享有助于 遵循常量和 D外也可以改写为:

由电容值定义的理想位粗按常数从 储能电容电荷共享。和有效半位重量(wi,id是 定义为半位权重)如下所示:

有趣的是,位权重w我不再对应于 DAC 位试验时的输出步长。例如,MSB 的 DAC 输出步长 位试用与 V 成线性比例在由于位电容具有V在作为其首字母 价值。(10) 和 (11) 表示 V在相关DAC输出阶跃将更进一步 由较低位解析,导致有效位权重为 (12) 和 (13) 与信号无关。这种技术的一个警告是,因为引用是 在位试验期间不由有源电路驱动,输入信号相关 DAC中的非线性寄生电容将影响 储能电容和相应的位电容。这在实践中 将此技术的应用限制在 18 位 ADC 及以下,假设我们是 不使用非常大的储能电容器以节省面积。另一方面,任何 DAC电容阵列中的固定寄生电容不会影响信号 位权重的独立性,因为它们仅修改电荷共享比率 在储能电容器和相应的位电容器之间,产生 略有不同,但仍是信号独立的位权重。

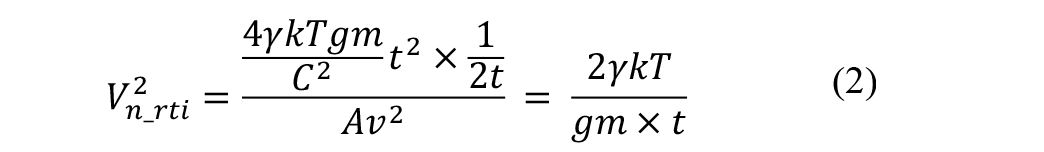

C. 使用LSB电容器进行校准

为了校正由于失配、寄生效应和储电容电荷均分误差引起的位重误差,需要执行校准以帮助实现16位电平 线性。在 文献。在 [31] 和 [32] 中,基于均衡的数字引擎用于查找 ADC 位权重。对于相同的输入,它们需要不同的ADC决策路径 使其工作。在[33]中,流水线SAR ADC使用后台校准 位权重在第一阶段。在 [34] 中,引入了一个额外的 DAC 测量主SAR DAC中的位权重误差。最近,校准 引入了使用额外试验的方法[35],尽管它仅适用于模拟 位重量补偿。

图 16.使用现有 LSB 电容器阵列进行 SAR ADC 校准。

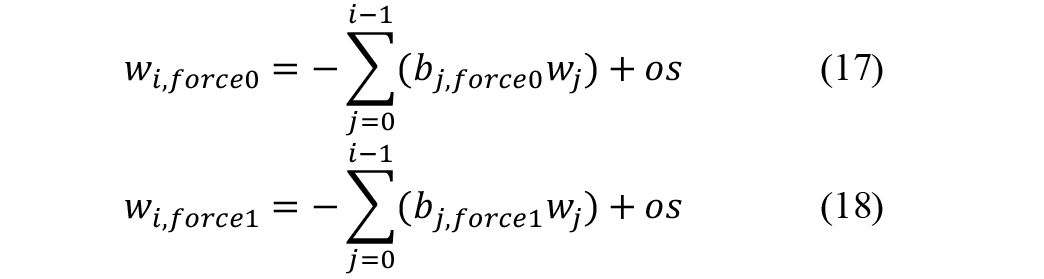

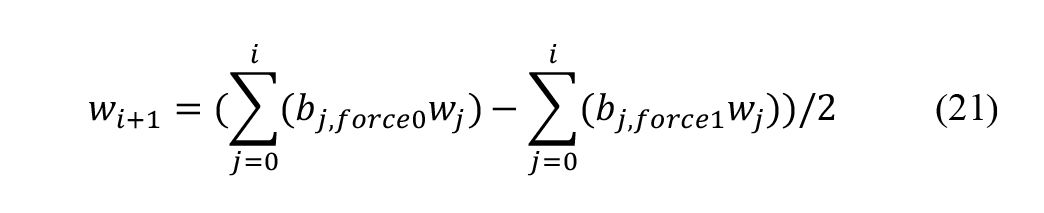

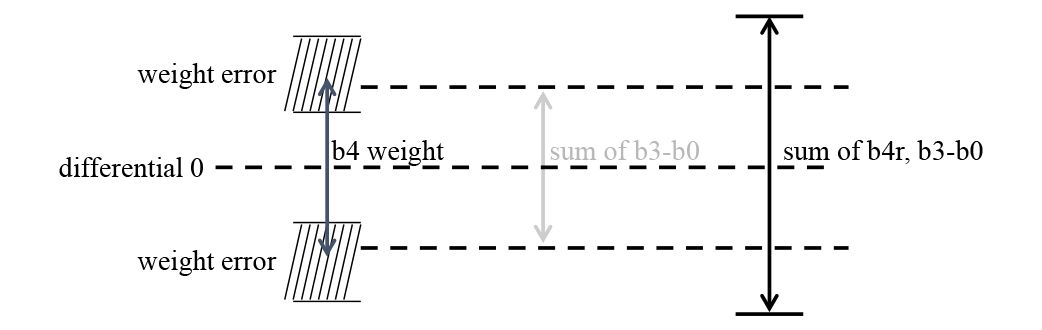

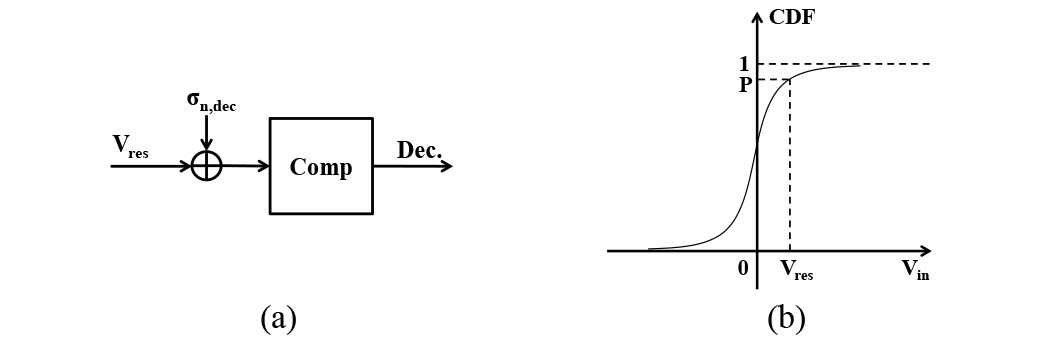

此处提出的开销最小的片上前台校准与此类似 在概念上为 [17] 和 [36]。但是,我们可以校准较低的位 这对于精密ADC也至关重要。ADC 测量位权重 校准期间补偿数字域中的误差 操作。而不是使用后台或引入额外的基准DAC 测量位权重,ADC中的一些LSB(本设计中的B4R-B0)为 用于校准更有效的位(B4及以上),如图16所示。B4 是 首先使用现有的SAR ADC反馈环路使用b4r-b0进行测量,而 ADC输入接地,b4以上的所有位均未经过导振。具体来说,我们 强制 b4 为 0 并获取与 b4 对应的 ADC 输出代码 力 0 处的权重,加上 ADC 偏移,然后我们强制 B4 到 1 以获得另一个 一组输出代码,广义公式如下所示:

为了消除偏移量,我们减去两者得到:

校准 b4 后,使用 b4-b0 测量 b5,依此类推,如广义 在以下等式中:

对每个位权重进行多次测量,以平均影响 的噪音。由于冗余(例如 b4r)可用,因此可以进行此校准 以增加测量位重量误差的可用范围,如图 17 所示, 否则,如果位权重较大,LSB 将无法测量位权重 比标称重量。此外,如[36]所述和图18所示,ADC 偏移会占用 LSB 测量范围。为了实现16位电平线性度, 像B4这样的低位也需要校准。系统中的偏移可能更大 比这些较低位的校准范围。为了解决这个问题,我们介绍 校准期间使用固定抖动进行偏移消除。图6(a)说明 我们将B11-B0重新用作抖动电容器。在前台校准期间,我们 测量ADC失调,并通过应用适当的失调量来消除它 使用抖动电容器。因此,ADC在位权重期间似乎无偏移 校准,使我们能够校准比 [17] 中小得多的钻头重量 以及 [36],这对于实现精密 ADC 性能至关重要。

图 17.带冗余的电容器测量。

图 18.通过施加固定抖动量进行失调补偿的电容器测量。

D. 统计残留物测量

图 19.SAR转化残基的统计残基测量(SRM)。(a) 框图。(b) 累积分布函数(CDF),根据决策概率P推导出残余值。

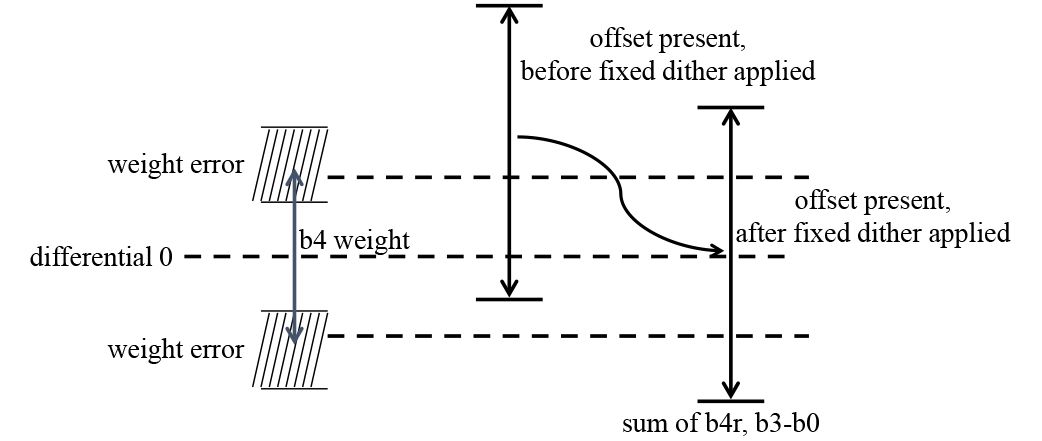

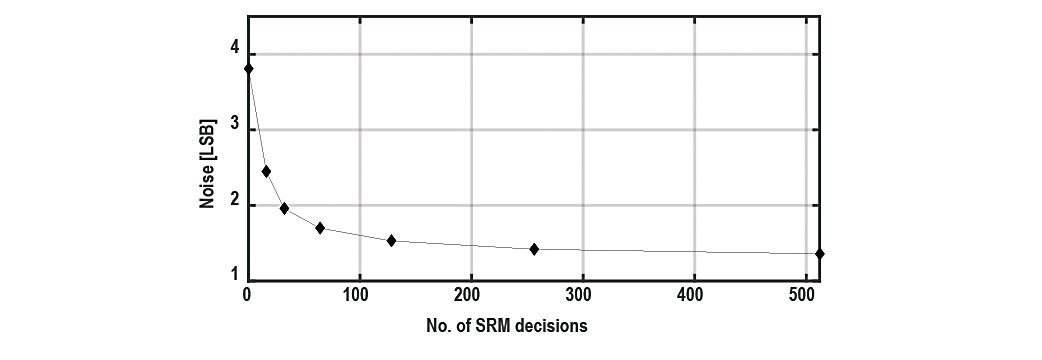

如前所述,在LSB重复之后,DAC输出或比较器输入 仍然包含一个小的残余误差V分辨率.有限 V分辨率是由于转换 噪声以及量化误差。如[37]-[39]所述,我们可能会采取 噪声比较器测量V值的优势分辨率从而改善 总体 ADC 精度。图 19 说明了 V 如何分辨率测量工作。假设 比较器具有高斯噪声,其累积分布函数 (CDF) 定义为:

Where we denote:

我们可以推导出 V分辨率如:

在常规试验或LSB重复结束时,比较器得出一个数字 的顺序决策,其输入保持不变。基于概率 在决策1中,小比较器输入可以用(25)进行估计 了解比较器噪声水平。数字中的小型查找表 (LUT) 引擎可用于近似解此非线性 (25) 和 ADC数字输出得到相应补偿。与[38]和 [39],我们工作中比较器决策的数量可以在硅中变化 以证明有效性并检查测量数据的权衡。

仅当ADC运行速度低于16 MS/s时,才会启用此技术,因此 在所有位试验之后,我们在转换阶段还有时间,允许 让比较器在之后触发多次以估计其输入 电压,即DAC输出残余电压。

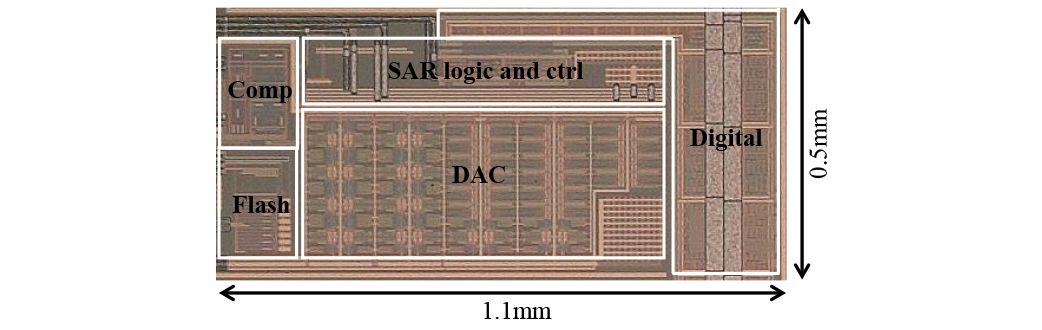

图 20.芯片显微照片。

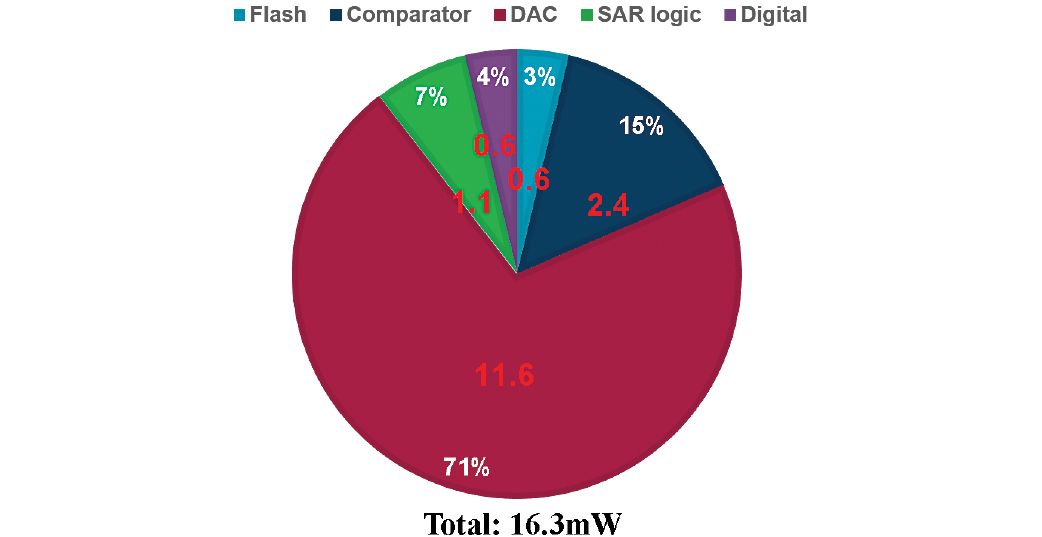

图 21.模数转换器电源故障。

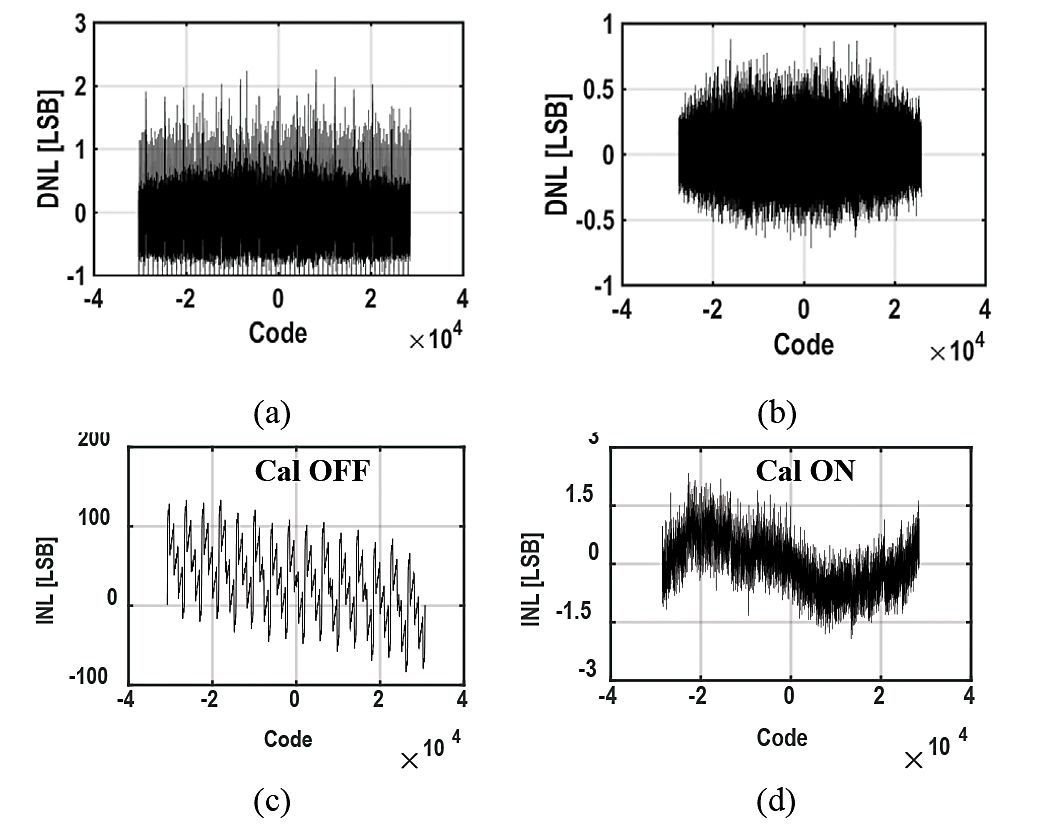

图 22.典型直流线性度图。(a) 校准前的DNL。(b) 校准后的DNL。(c) 校准前的INL。(d) 校准后的INL。

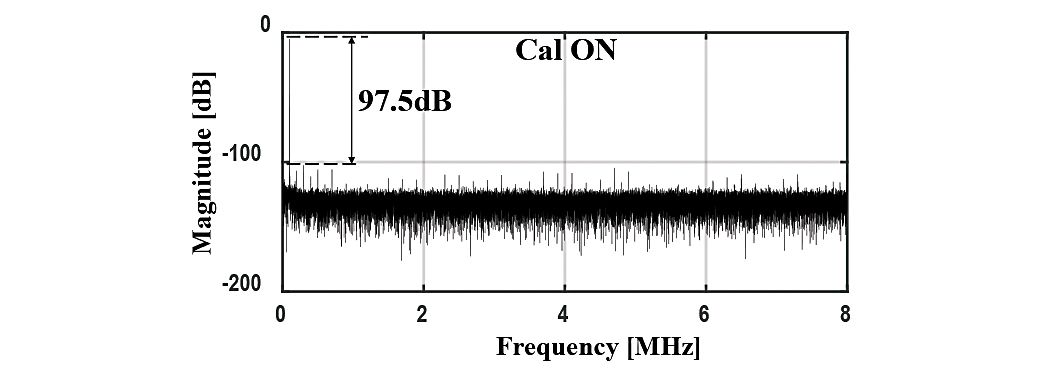

图 23.使用 100 kHz 输入校准后的典型交流频谱。

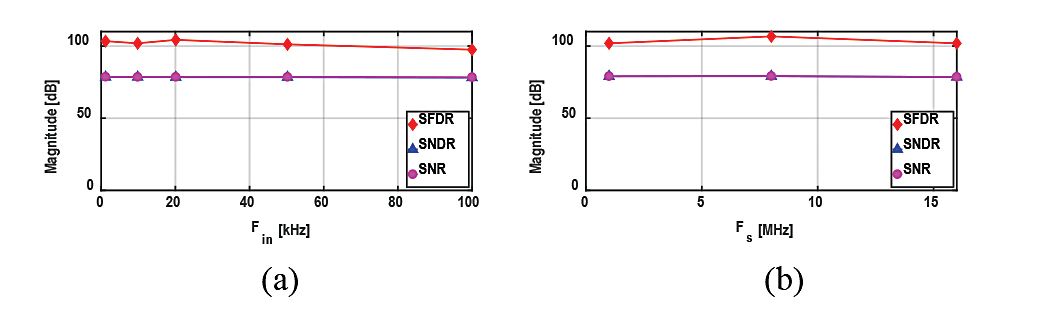

图 24.交流性能。(a) SFDR/SNDR/SNR 与 Fs = 16 MS/s. (b) SFDR/SNDR/SNR 与 Fs 的 Fs = 100 kHz。

图 25.随LSB重复次数测量的ADC噪声。

图 26.测量的ADC噪声与SRM决策的数量。

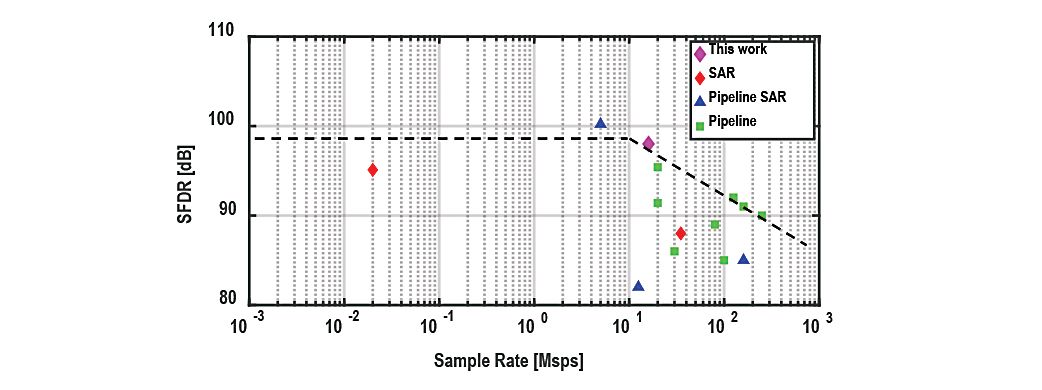

图 27.SFDR与ISSCC和VLSI的奈奎斯特ADC在过去10年的比较,SFDR>85 dB或SNDR>80 dB。

| 这项工作 | 赫瑞尔 [1] | 班农 [2] | 马多克斯 [3] | 克莱默 [12] | 三木 [29] | |

| 类型 | 特区 | 管道搜救 | 管道搜救 | 特区 | 特区 | 特区 |

| 分辨率 [位} | 16 | 18 | 18 | 16 | 14 | 13 |

| 速度 [毫秒/秒] | 16 | 12.5 | 5 | 1 | 35 | 50 |

| 功率 [毫瓦] | 16.3 | 105 | 30.5 | 6.95 | 54.5 | 4.2 |

| SFDR/SNDR [dB] | 98/78 | 82/80 | 100/99 | 100/81 | 99/75 | 85/71 |

| INL [LSB] | -1.9/2.3 | -2.5/2.5 | -2/2 | -0.8/0.8 | -0.9/0.7 | -1.3/2 |

| 辛 [pF] | 1.14 | 25 | 那 | 25.6 | 0.2 | 2 |

| VDD [V] | 3.3/1.2 | 5/2.5 | 5/1.8 | 1.2 | 2.5/1.2 | 1.2 |

| 面积 [毫米2] | 0.55 | 4.5 | 5.74 | 4.1 | 0.24 | 0.097 |

| 校准 | 片上 | 片外 | 片外 | 片外 | 片外 | 片上 |

| FoM_S [分贝] | 165 | 157.7 | 177.7 | 159.6 | 159.5 | 166.8 |

| 过程 | 55纳米 | 250纳米 | 180纳米 | 55纳米 | 40纳米 | 90纳米 |

四、实验结果

该芯片采用55纳米CMOS工艺制造。模具显微照片如 图 20,尺寸为 1.1 毫米 x 0.5 毫米。数字引擎,其中还包括 由于逻辑密集,校准很小。ADC 输入接口工作在 3.3 V,而所有其他电路使用1.2 V。默认情况下,最佳 LSB 重复处于打开状态 SRM 关闭以 16 Msps 的速度运行。 图 21 显示了电源击穿 其中,DAC功耗为11.6 mW,其中还包括估计的2.8 mW 电平转换器。采样电容大幅降低至1.14 pF (包括闪光采样电容)用于精密ADC,特别注意 通过亚fF级寄生效应进行耦合,以保持16位线性度 性能。图22显示了校准时的直流线性度性能 关断续续。在校准之前,我们看到INL误差高达大约250 LSBpp 主要是由于储能电容器的电荷分配误差。后 校准时,INL 为 -1.9/2.3 LSB。它受到采样失真的限制,因为 避免了输入自举,以支持脉冲模式下的无源采样。 图23显示了输入信号为100 kHz的频谱,交流性能为: 在图 24 中总结,其中 SFDR/SNDR/SNR 与 F在和 Fs分别显示。对于大多数精密应用,输入信号带宽低于100 kHz, 保持超过 97.5 dB 的 SFDR。信噪比超过 78 dB 和等效 ADC噪声约为3 LSB,符合我们的设计目标。在图25中,测得的ADC 噪声与LSB重复次数的关系证明其有效性。 以较低频率工作时,统计残留测量 (SRM) 可以启用以进一步提高准确性。图26显示了ADC噪声与 SRM 决策的数量。我们观察到ADC噪声确实接近 随着 SRM 决策数量的增加,对噪声水平进行采样。请注意,对于两者 噪声图,转换噪声配置为较高以主导采样 噪音,以更好地观察效果。图 27 中的曲线比较了线性度 该ADC与ISSCC和VLSI最近的奈奎斯特ADC在 过去10年的SFDR>85 dB或SNDR>80 dB[40]。与最近的比较 表1给出了公开的中速和高分辨率SAR ADC。[1] 和 [2] 使用流水线 SAR 架构,面积大约大 10×,面积大 20× 更大的输入电容。此外,所有其他精密ADC(16位+)都依赖于 片外校准,因此大大增加了测试成本。

五、结语

在 55 nm CMOS 中实现 16 MS/s 操作的精密 16 位 SAR ADC 是 本文介绍。它支持连续模式和脉冲模式 操作。通过小电容器实现快速转换和小面积 阵列和信号无关,每个位电容DAC一个储能电容 结构。片上校准开销最小,校准幅度更低 位有助于确保ADC达到16位精度。最佳 LSB 重复和 统计残留物测量进一步提高了ADC的精度和效率。 与传统的精密SAR ADC相比,该ADC的面积小10×20× 更小的采样电容和片上校准使其非常适合 适用于精密 SoC 应用。据我们所知,这项工作也是第一次快速 深亚微米CMOS节点中的精密SAR ADC。

审核编辑:郭婷

-

线性科技LTC2376 - 16:高性能16位SAR ADC的卓越之选2026-03-31 169

-

深入剖析LTC2373 - 16:高性能16位SAR ADC的卓越之选2026-03-30 445

-

LTC2374-16:高性能16位SAR ADC的深度剖析与应用指南2026-03-27 222

-

Analog Devices Inc. AD4630-16/AD4632-16双通道16位SAR ADC数据手册2025-06-25 1258

-

16位16MS/s SAR ADC采用55nm CMOS进行片上校准2023-02-02 3369

-

HPM6750 MCU片内16位ADC精度测试2022-11-22 4997

-

灿芯半导体正式推出高精度16位逐次逼近型ADC2022-06-09 2732

-

双16位5Msps SAR ADC2021-04-30 1034

-

LTC2393-16-16位1Msps SAR ADC2021-04-24 902

-

基于自校准、自检架构的低功耗16位SAR ADC2020-09-23 3137

-

高速16位SAR型ADC LTC2393-162010-09-11 5640

-

Linear推出16位SAR ADC LTC2393-162010-01-19 1373

-

Linear推出16 位 SAR ADC LTC2393-12010-01-16 1268

全部0条评论

快来发表一下你的评论吧 !