PCB布线规则和技巧图解(下)

PCB布线规则和技巧图解(下)

描述

书接上文:

五、拐角设计

在PCB布线时,走线拐弯是不可避免的,当走线出现直角拐角时,在拐角处会产生额外的寄生电容和寄生电感。走线拐弯的拐角应避免设计成锐角和直角形式,以免产生不必要的辐射,同时锐角和直角形式的工艺性能也不好。要求所有线与线的夹角应大于等于135°。在走线确实需要直角拐角的情况下,可以采取两种改进方法:一种是将90”拐角变成两个45拐角:另一种是采用圆角。圆角方式是最好的,45拐角可以用到10GHz频率上对于45°拐角走线拐角长度最好满足L>3W。

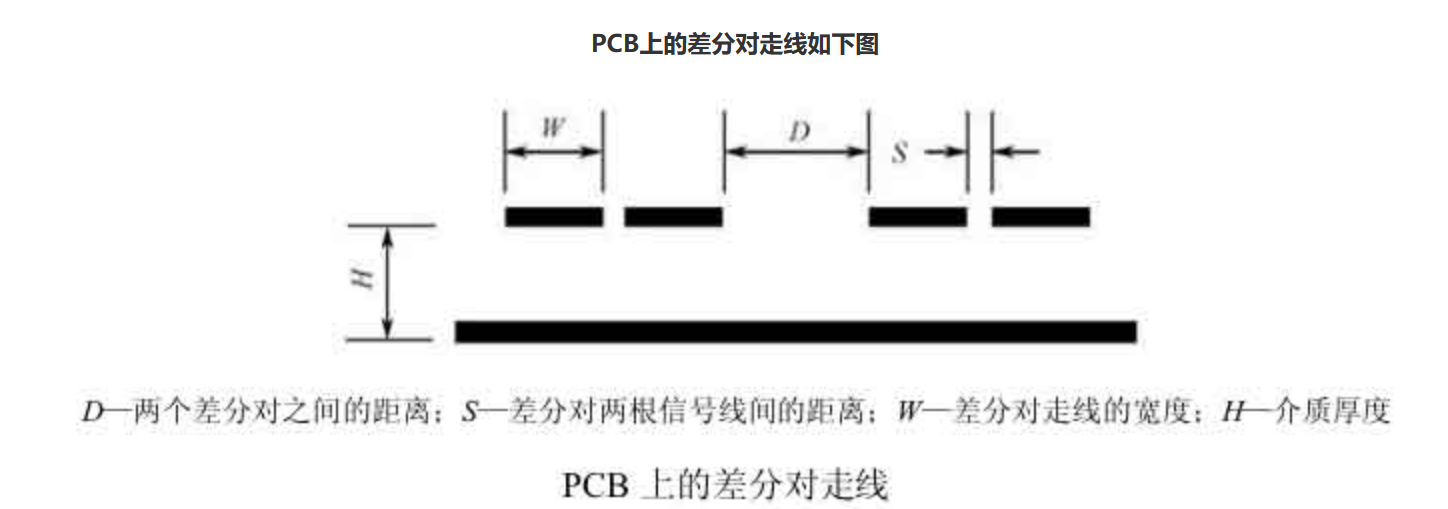

六.差分对走线

为了避免不理想返回路径的影响,可以采用差分对走线。为了获得较好的信号完整性,可以选用差分对走线来实现高速信号传输。前面介绍的LVDS电平的传输采用的就是差分传输线的方式

1.差分信号传输优点:

a.输出驱动总的di/dt会大幅降低,从而减小了轨道塌陷和潜在的电磁干扰

b.与单端放大器相比,接收器中的差分放大器有更高的增益。

c.差分信号在一对紧耦合差分对中传输时,在返回路径中对付串扰和突变的鲁棒性更好.

d.因为每个信号都有自己的返回路径,所以差分信号通过接插件或封装时,不易受到开关噪声的干扰。

2.差分信号的缺点

a.如果不对差分信号进行恰当的平衡或滤波,或者存在任何共模信号,就可能会产生EMI问题。

b.与单端信号相比,传输差分信号需要双倍的信号线。

3.设计差分对走线时,要遵循以下原则。

a.保持差分对的两信号走线之间的距离S在整个走线上为常数

b.确保D > 2S,以最小化两个差分对信号之间的串扰。

c.使差分对的两信号走线之间的距离S满足S=3H,以便使元件的反射阻抗最小化。

d.将两差分信号线的长度保持相等,以消除信号的相位差。

e. 避免在差分对上使用多个过孔,因为过孔会产生阻抗不匹配和电感。

七.控制PCB导线的阻抗和走线终端匹配

在高速数字电路PCB和射频电路PCB中,对PCB导线的阻抗是有要求的,需要控制PCB导线的阻抗。在PCB布线时,同一网络的线宽应保持一致。由于线宽的变化会造成线路特性阻抗的不均匀,对高速数字电路传输的信号会产生反射,故在设计中应该尽量避免出现这种情况。在某些条件下,如接插件引出线、BGA封装的引出线等类的结构时,如果无法避免线宽的变化,应该尽量控制和减少中间不一致高:分的有效长度。

在高速数字电路中,当PCB布线的延迟时间大于信号上升时间(或下降时间)的1/4时,该布线即可以看成传输线。为了保证信号的输入和输出抗与传输线的阻抗正确匹配,可以采用多种形式的终端匹配方法,所选择的匹配方法与网络的连接方式和布线的拓扑结构有关

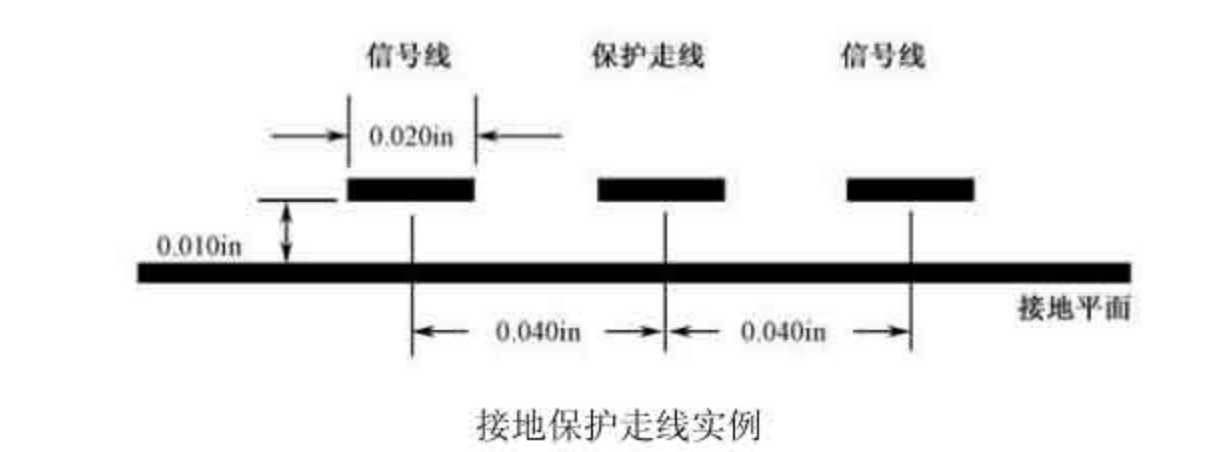

八.设计接地保护走线

在模拟电路的PCB设计中,保护走线被广泛地使用,例如,在一个没有完整的地平面的两层板中,如果在一个敏感的音频输入电路的

在数字电路中,可以采用一个完整的接地平面取代接地保护走线,接地保护走线在很多地方比完整的接地平面更有优势

根据经验,在两条微带线之间插入两端接地的第三条线,两条微带之间的耦合则会减半。如果第三条线通过很多通孔连接到接地平面。则它们的合将进一步减小。如果有不止一个地平面层,则要在每条保护走线的两端接地,而不要在中间接地。

注意:在数字电路中,如果两条走线之间的距离(间距)足够并允许引入一条保护走线,那么两条走线相互之间的合通常已经很低也就没有必要设置一条接地保护走线了。

审核编辑:汤梓红

-

高速pcb布线规则有哪些2024-06-10 2111

-

如何优化 PCB 布线规则?2024-02-19 2109

-

「实用干货」7条实用的PCB布线规则,可收藏2023-02-01 1818

-

7条实用的PCB布线规则2022-09-30 2209

-

PCB的布局布线规则2021-11-11 10038

-

PCB手动布线规则2016-08-16 1696

-

高频在PCB中的布线规则2016-07-26 956

-

DDR布局布线规则与实例2015-11-13 1099

-

PCB布局布线规则2013-08-06 5490

-

PCB布线规则2012-06-06 9083

-

PCB布线规则详解解说2009-11-24 2040

-

pcb布线规则2007-12-10 25123

全部0条评论

快来发表一下你的评论吧 !