SVA Assertion有什么优势?

描述

简单来说,assertion就是一个对于设计规格的check。

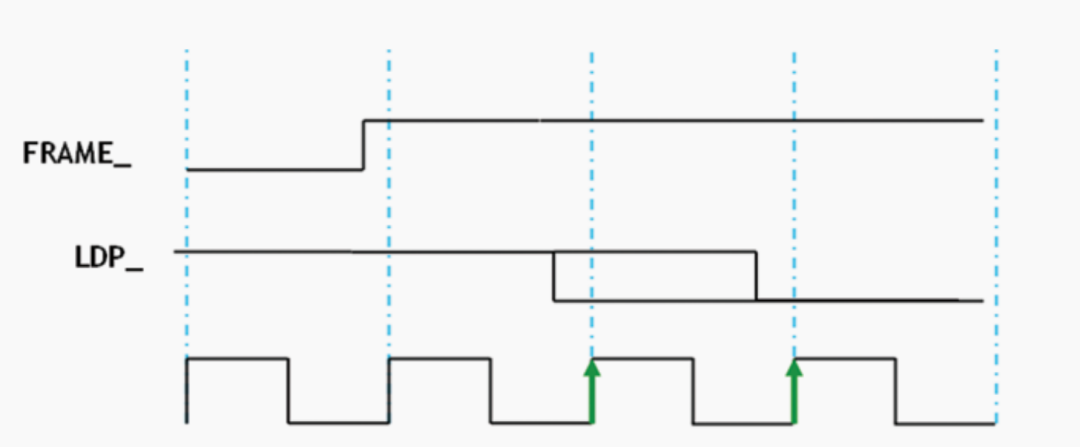

如果我们设计正确工作时需要满足FRAME_上升沿后的1~2拍会出现LDP_的下降沿,如下图所示

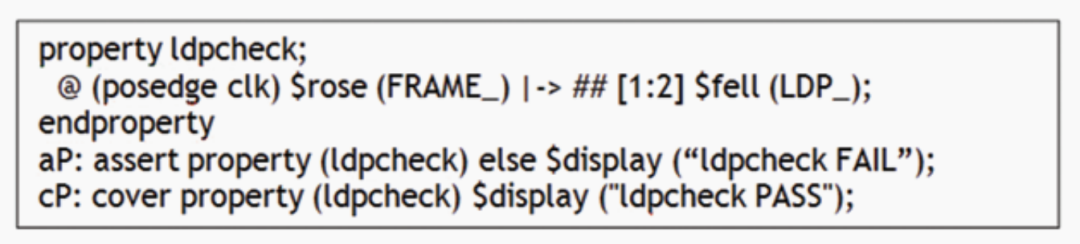

那么SVA语法就可以写成:

非常简洁高效。

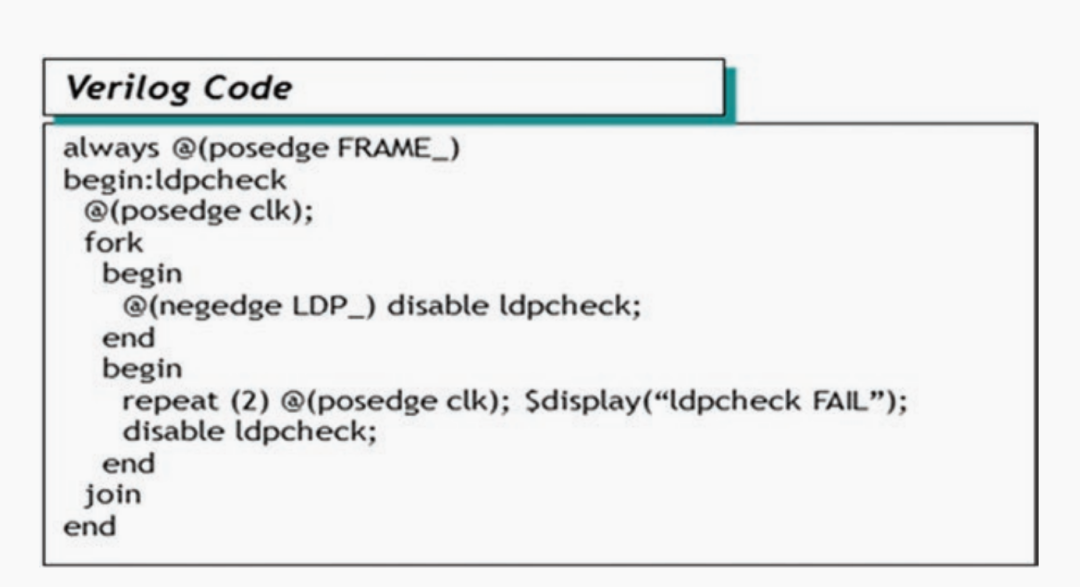

如果只使用Verilog呢?该怎么进行这种规格的检查呢?

在上面的例子中,每次监测到FRAME_就会启动2个进程(fork-join)。

如果无法在两个时钟周期内监测到LDP_的下降沿,那么就会打印FAIL。

语法的最高境界就是自然语言,从这个角度看SVA这种描述性语言比Verilog这类程序性语言要高效多了。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

断言(Assertion)使用2025-12-12 114

-

SVA断言的用法教程2025-05-15 3727

-

写assertion很痛苦?了解一下SVA Checker Library2023-08-12 2070

-

聊聊形式验证中的SVA2023-06-14 3831

-

使用SVA的几个好处2023-03-21 1524

-

介绍使用SVA的几个优势2023-01-13 1697

-

介绍一些SVA基本的概念和常用的语法2022-10-27 3912

-

Creating Assertion-Based IP2009-07-23 512

-

SystemVerilog Assertion Handbo2009-07-22 1063

-

SVA系列(通用)彩电电路图(1)2009-05-25 1831

-

SVA上广电D2972-73系列彩电电路图2009-05-23 1820

-

SVA上广电D2560彩电电路图2009-05-15 1688

-

SVA上广电D2155F彩电电路图2009-05-13 2379

全部0条评论

快来发表一下你的评论吧 !