详细解读四代EPYC处理器技术

处理器/DSP

描述

近年来,在服务器和数据中心等企业级市场,AMD凭借持续更新的“Zen”架构,其EPYC(霄龙)系列处理器的市场占有率上升势头非常迅猛。2022年11月,AMD推出全新第四代EPYC处理器。新处理器将单插槽处理器核心数量提升到最多96核,并且采用了最新的“Zen 4”架构,带来大量全新特性。接下来,本文就对第四代EPYC处理器进行详细解读。

第四代EPYC处理器:EPYC 9004系列登场

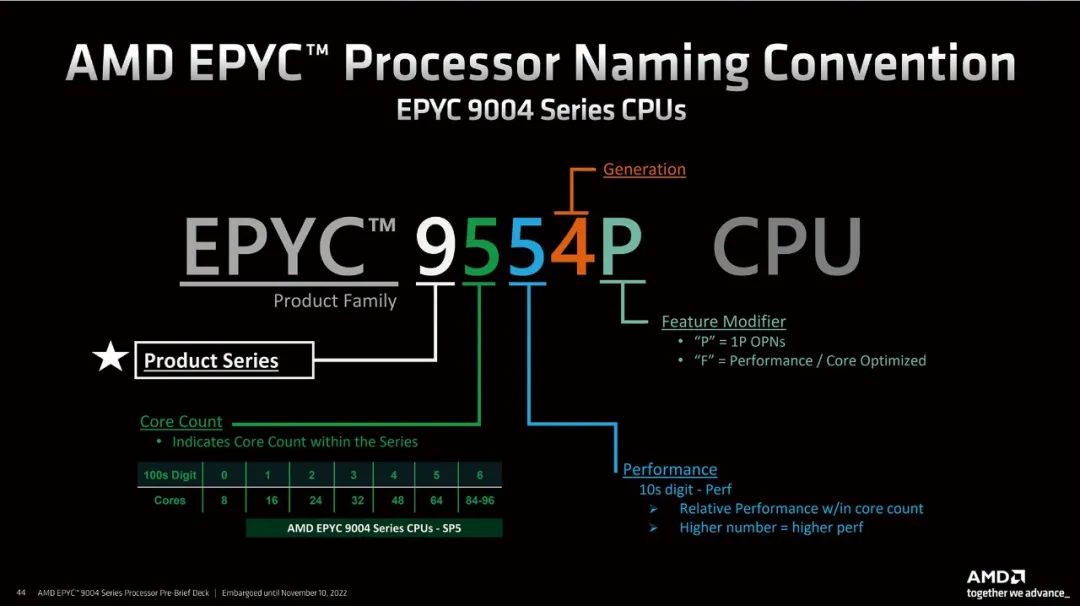

在解析AMD第四代EPYC处理器的架构之前,我们先来梳理一下它的型号定义,因为在这方面它与上代产品存在显著差异。

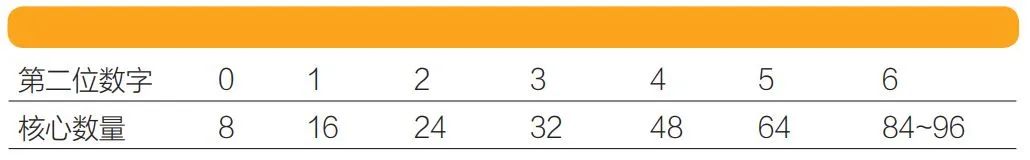

此前,AMD采用EPYC 7000系列作为原始命名。最后一位数代表不同代次,比如EPYC 7001、EPYC 7002和EPYC 7003就分别代表三代不同的产品,其中又包含大量细分型号。在第四代EPYC处理器上,AMD改用了EPYC 9004作为产品基础代号,这可能是考虑到本代产品具备极为显著的性能提升。同时,在大多数人的概念中,“9”相比“7”显得定位更高、性能更强。第二位数字代表处理器核心数量,其基本对应关系如下表:

第三位数字代表性能情况,数字越大则性能越强,目前由2~7的不同数字组成。如果AMD愿意,未来还可能进一步扩展到9。最后一位数字则固定为“4”,代表第四代EPYC处理器。

▲AMD详细解读了EPYC 9004产品命名情况

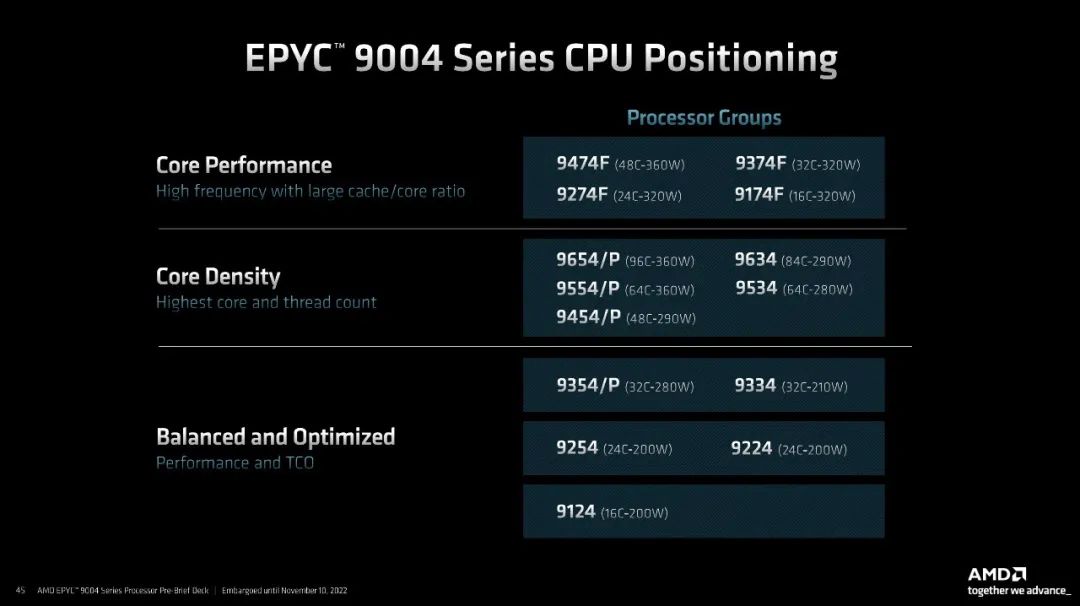

▲AMD将EPYC 9004产品分为了三类:追求核心密度的产品、追求平衡和优化的性能的产品以及追求核心性能的产品。

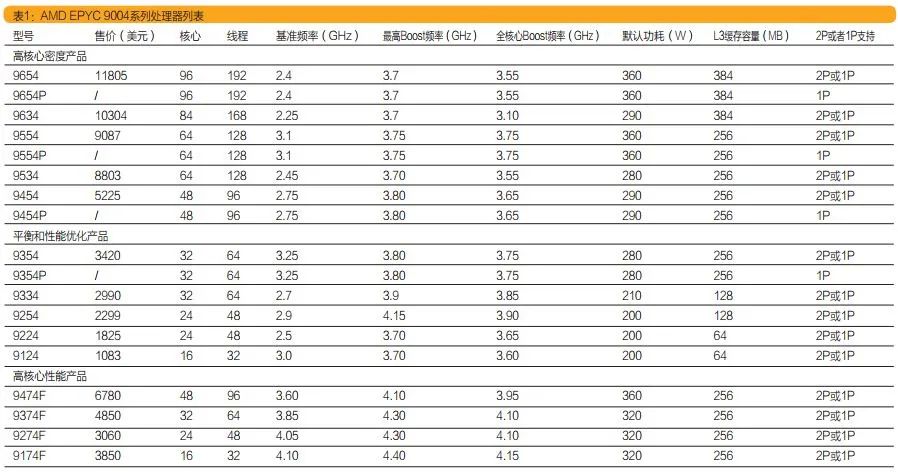

AMD本次发布了18款EPYC 9004系列处理器,分为3个大类,分别是追求核心密度的产品、追求平衡和优化的性能的产品以及追求核心性能的产品,具体规格见下表。

▲EPYC 9004、EPYC 7003、英特尔第12代酷睿、锐龙7000以及英特尔第11代酷睿处理器(从左到右)的外观对比,可以看到EPYC 9004大了不少。

计算和扩展的领先地位:EPYC 9004技术架构一览

毫不夸张地说,EPYC 9004是目前市面上最先进的企业级产品之一。它在CPU架构、Chiplet应用以及互联方式上,几乎都是当前技术条件下所能达到的极致。这一次,AMD在超大规模的企业级产品研发上进入了一个新的层次,短时间内,能超越它的只有AMD自己的下一代产品。

设计目标:拥有扩展和计算性能的优势地位

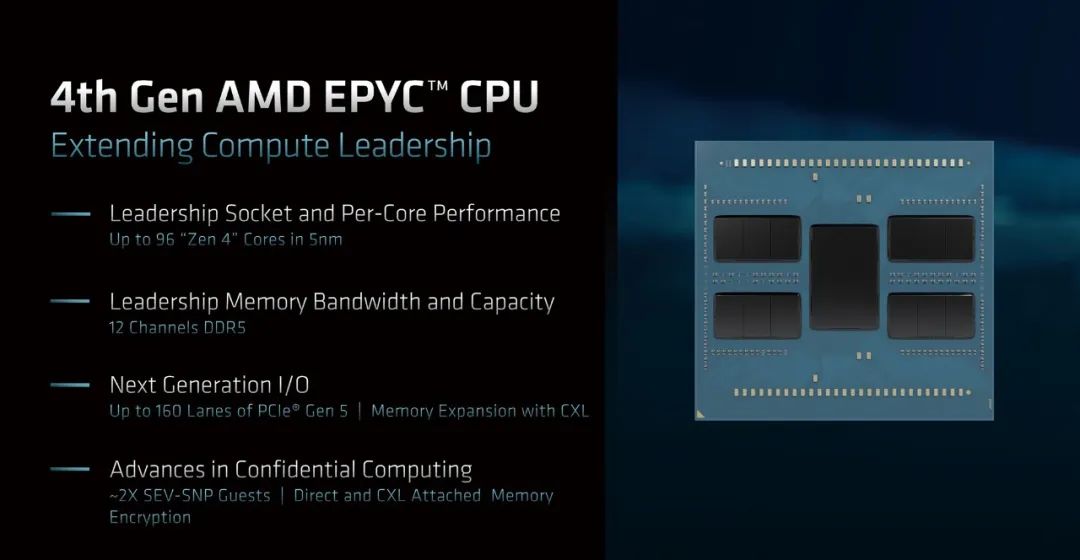

▲AMD EPYC 9004的设计理念

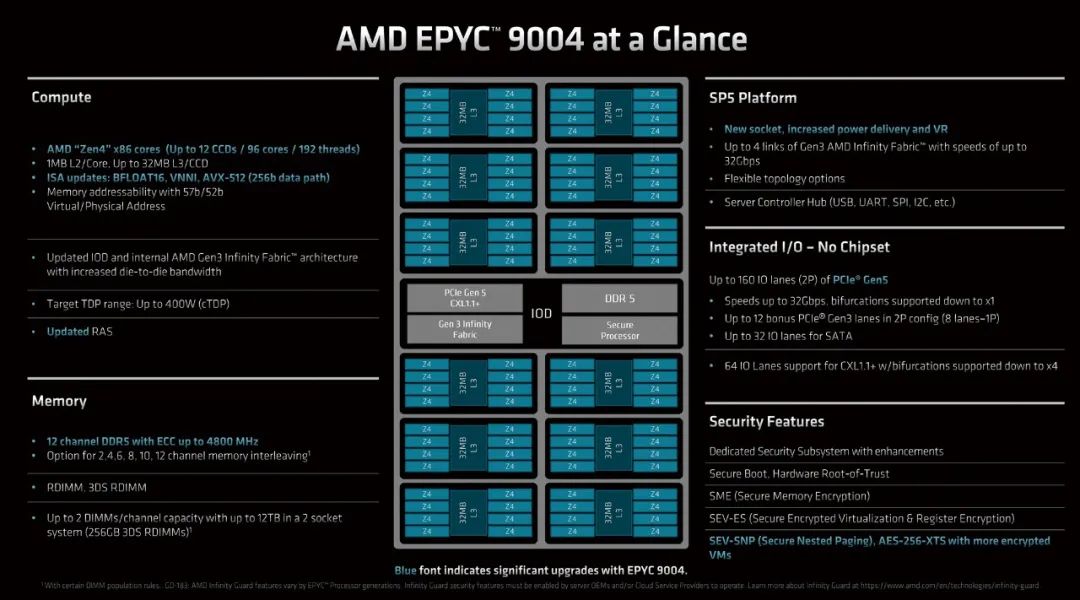

按照惯例,我们先来看看EPYC 9004的设计理念和实现情况。AMD EPYC 9004的设计理念就是继续保持计算性能和扩展能力的优势地位。AMD分四个方面进行了阐述:首先是拥有最先进的单核心性能和单插槽性能,这依靠最新的Zen 4架构和5nm工艺实现;其次是配备超大的内存带宽和容量,这依靠12通道的DDR5内存来实现;第三是采用全新的下一代IO接口,这包括最大160通道的PCIe 5.0控制器以及可以利用CXL协议扩展的内存寻址功能等;第四则是加密计算方面的新进展,主要通过CXL以及2倍的SEV-SNP功能来实现。

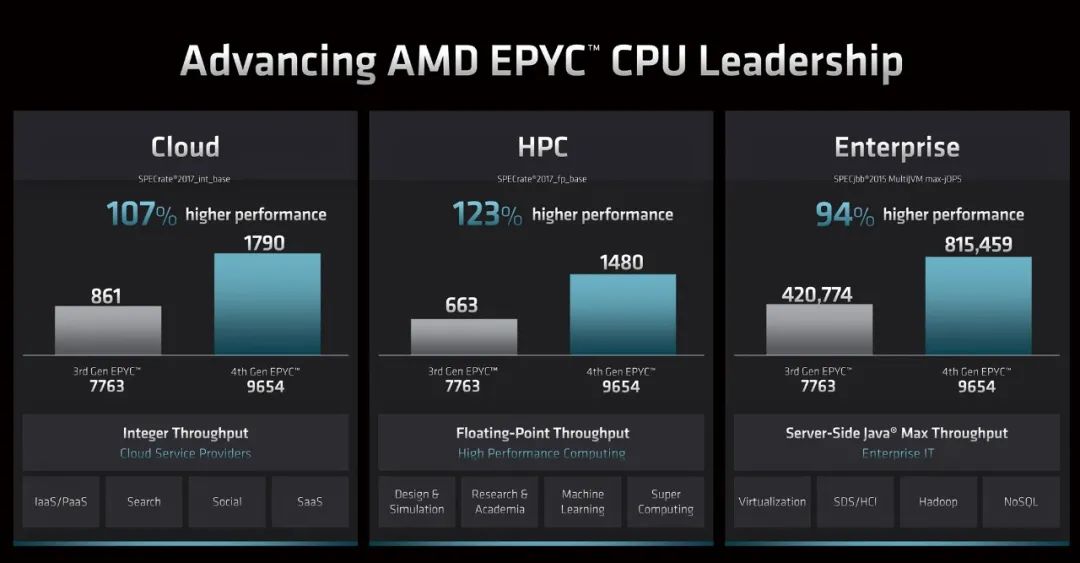

▲EPYC 9004和上代产品的性能比较情况

根据AMD官方数据显示,和EPYC 7003系列的顶级型号EPYC 7763相比,EPYC 9004系列中的顶级型号EPYC 9654能够在云端、HPC和企业级性能方面分别领先107%、123%以及94%。AMD宣称第四代EPYC处理器是全世界最好的数据中心处理器,拥有最快的数据中心性能、领先的能源效率、优秀的TCO表现、安全的加密计算能力以及丰富的生态系统。

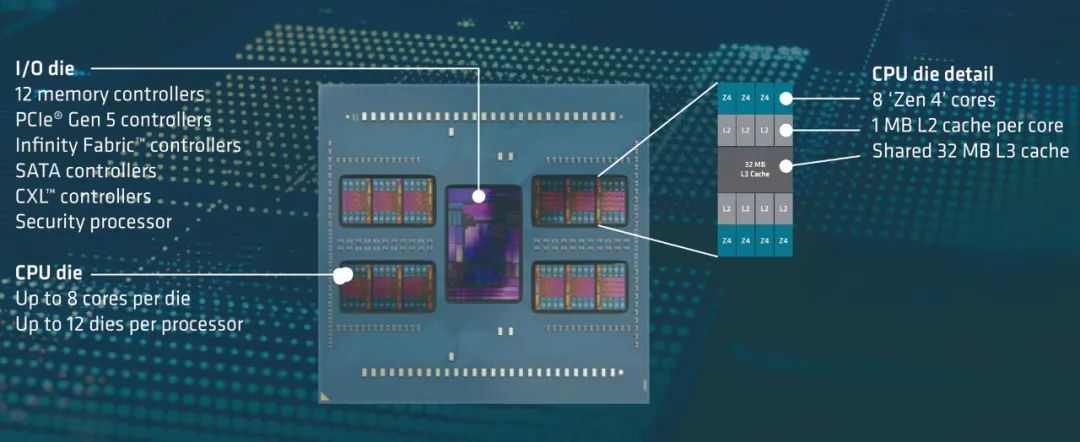

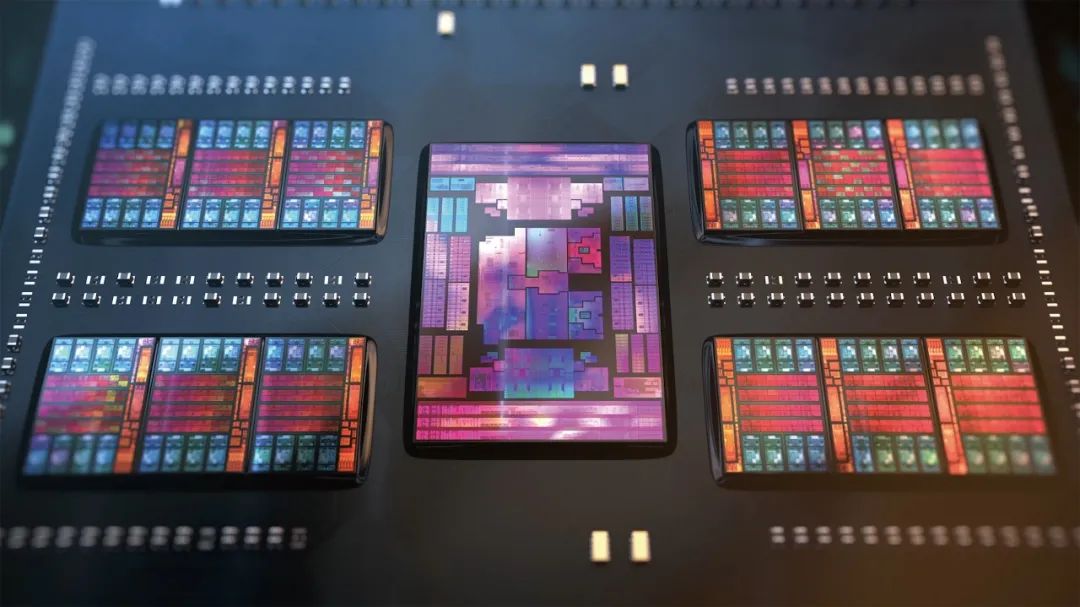

▲AMD EPYC 9004的宏观布局

为了达到这些设计要求,EPYC 9004在结构上依旧采用了Chiplet设计,布局在中间的是全新设计的IO芯片,周围的CCD单元数量增加到12个。每个CCD中依旧包含了8个CPU核心和相应的缓存,以及32MB L3缓存。EPYC 9004核心数量大增的原因是CCD数量从上代产品的最多8个增加到了最多12个,这使得它最多能提供96核心192线程。

Zen 4架构:IPC提升14%

AMD在企业级产品和消费级产品上采用了同样的核心微架构:EPYC 9004和桌面锐龙7000系列都是最新的Zen 4架构。有关Zen 4架构,本刊在之前锐龙7000首发文章中曾有过介绍,本文再简单回顾一下。

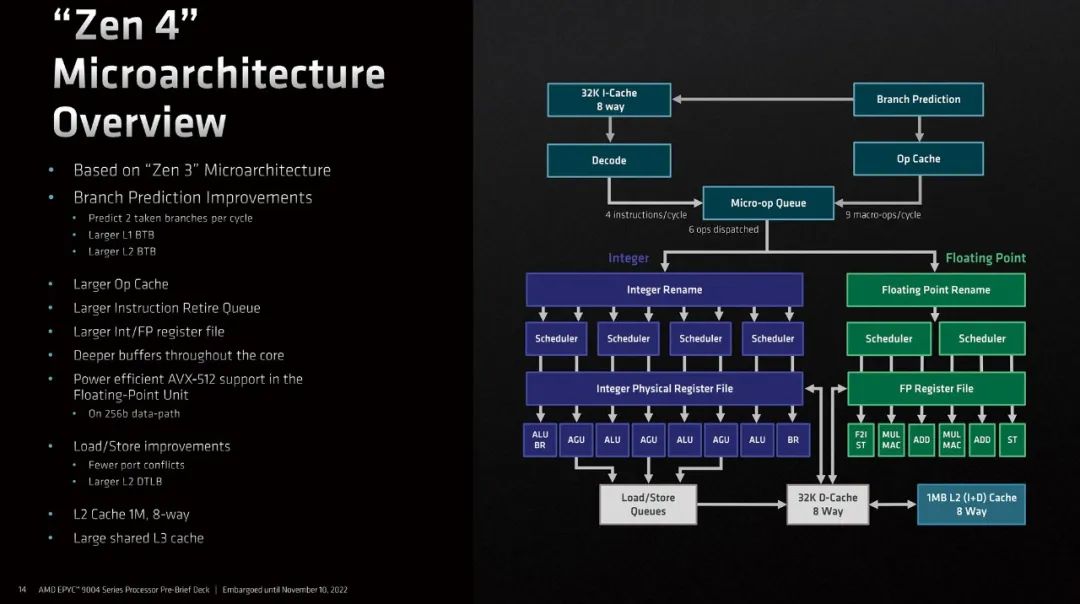

▲Zen 4微架构及改进一览

AMD Zen 4架构是基于Zen 3架构改进而来,在架构设计上,AMD希望实现更高的性能、更低的延迟和更好的能效比。其中性能的提升来自频率和IPC的提升;更低的延迟主要是提升了缓存的性能并且降低了整个架构的平均延迟;能效比方面则通过新设计、新工艺以及将移动端的一些技术移植在桌面端,降低了整个CPU的动态功耗。

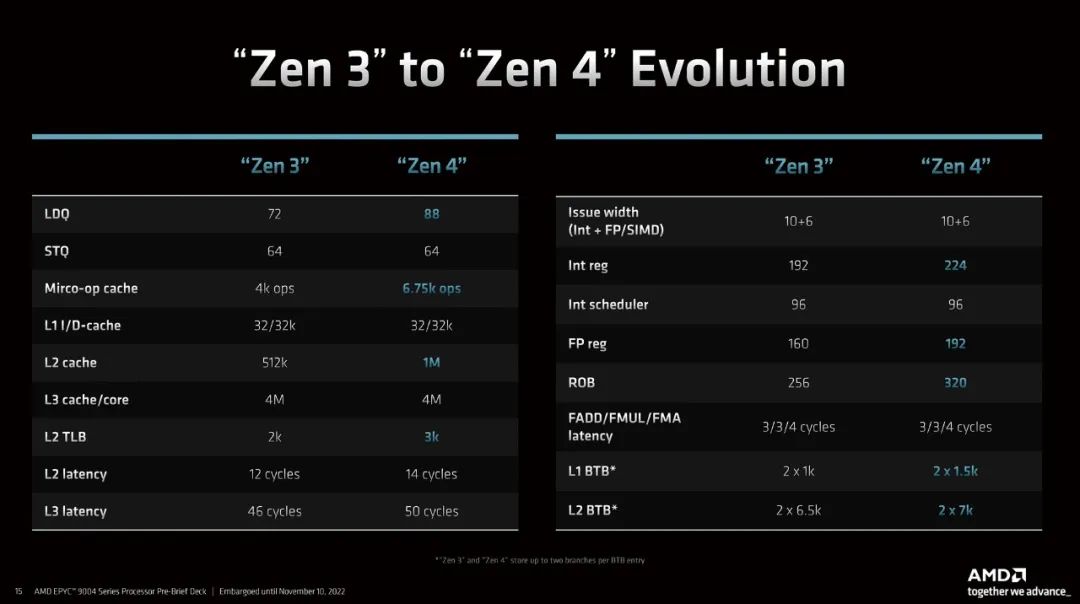

▲Zen 4架构相比Zen 3架构的重要提升

具体来看,Zen 4架构在分支预测、Op缓存、指令排序相关窗口、整数或浮点寄存器、每核心更深的缓冲区、后端读取和加载等方面进行了优化。特别的变化是另外加入对AVX-512指令集的支持,以及重新调整的每核心1MB、8-way L2缓存。

前端方面,分支预测部分有大幅加强。AMD使用了一个更强有力的分支预测单元,每周期可以执行2次分支预测。此外,L1分支目标缓冲区的容量提升了50%,达到1.5K条目,L2分支目标缓冲区则达到7K。Zen 4还拥有更大的Op缓存、更大的指令回写队列,它们在很大程度上提升了处理器的前端性能。

执行单元部分,Zen 4没有提升执行单元的数量,而是持续增大重排缓冲区。它增加了浮点/整数寄存器的体积,整数从192增加至224,浮点从160增加至192,核心缓冲区达到320条目。执行单元方面依旧是每周期10个INT和6个FP。

后端的读取和加载部分,Zen 4拥有更大的读取排序单元,更少的缓存端口冲突以及增大50%的L2 DTLB。另外依旧拥有每周期3个内存操作,最多每周期3个读取和2个写入。

缓存方面,最明显的改变是每个核心的L2缓存翻倍到1MB,这样可以降低CPU核心的未命中率并提升命中率,同时也降低了从L3和内存读取数据的几率。但是由于L2缓存增大,延迟也相应提升,L2和L3的延迟分别增加到最多14个周期和最多50个周期。

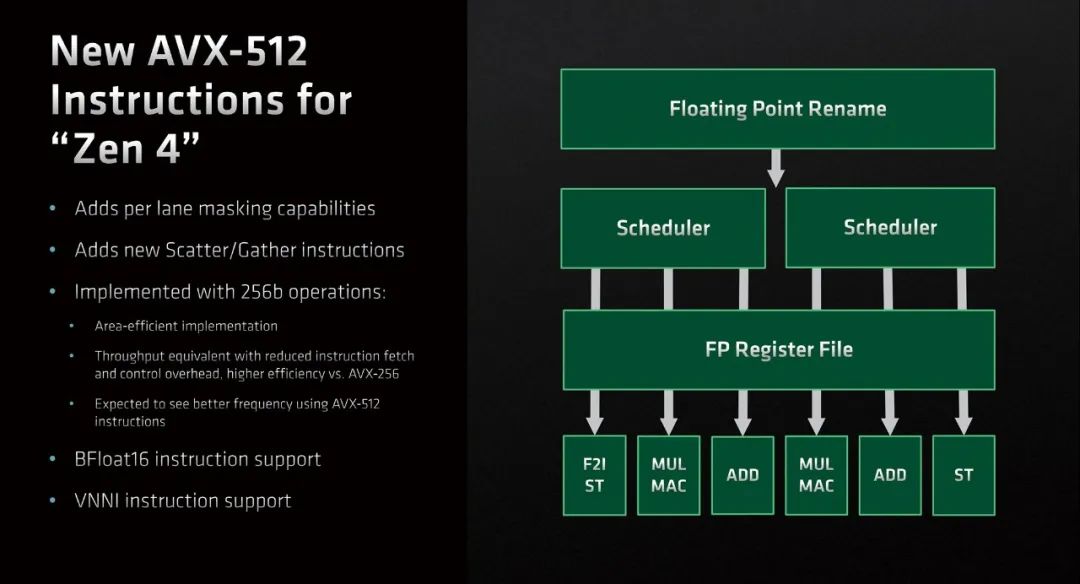

▲AMD在Zen 4上设计了全新的AVX-512引擎,和英特尔的路线有巨大差异。

在指令集方面,Zen 4实现了对AVX-512指令集的支持。Zen 4采用了2个AVX 256来合并执行1个AVX-512,而英特尔采用了独立的AVX512 SIMD核心。AMD的设计可以节省晶体管资源,并且不需要降低频率来运行AVX-512。但是当同时执行AVX2和AVX-512的时候,则必须完成一个后再执行另一个。AVX-512比之前Zen架构多核心执行FP32的工作效能提升了30%。此外,Zen 4也实现了对BF16数据格式的支持,这是AI计算中新兴的一种重要数据格式。

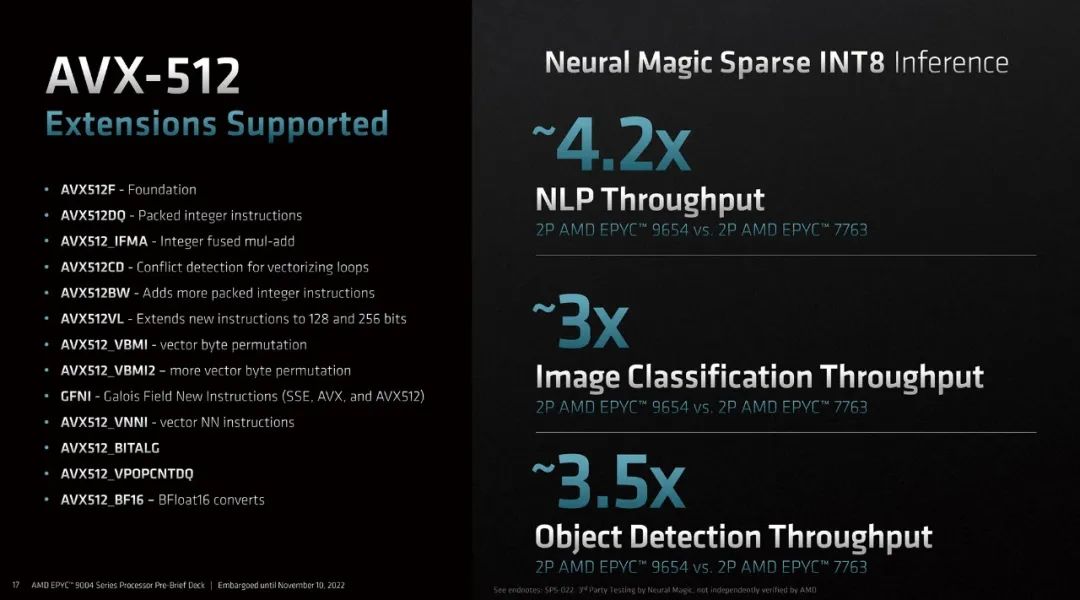

▲在启用AVX-512后,相关性能得到了巨大提升。

根据AMD官方数据显示,在支持AVX-512后,使用2路EPYC 9654(192核心)对比2路EPYC 7763(128核心),在NLP、图像识别以及物体检测的吞吐量测试中,前者的领先幅度分别达到4.2倍、3倍和3.5倍。

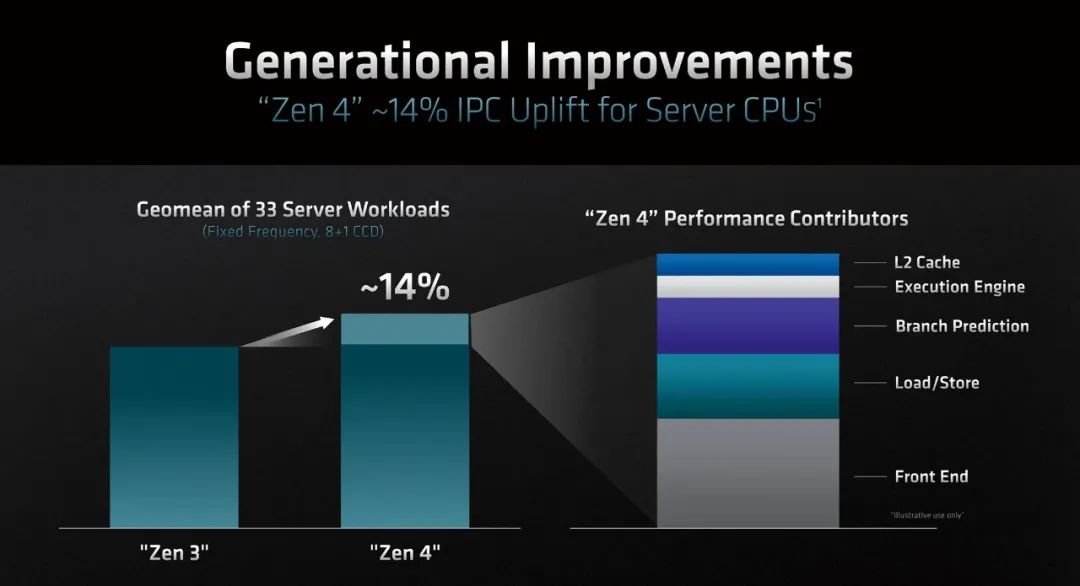

AMD还给出了Zen 4相比Zen 3的性能改进情况。总的来看,Zen 4有大约14%的IPC提升。其中贡献最大的是前端的改进,其次是存储和加载部分,再次是分支预测部分,执行部分和L2部分的改进带来的性能增幅则相对较小。在发布锐龙7000系列的时候,AMD给出的IPC提升数据是13%,所以这里提到的14%应该是根据服务器所面向的不同负载重新测试而来。

▲AMD Zen 4架构在服务器端取得了14%的IPC提升

最后再来看看安全方面的内容。Zen 4架构目前支持安全加密的虚拟化,包括SEV-ES、SEV-SNP,内存加密支持AES-256-XTS,支持最多1006个加密的客户机以及多主机秘钥SMKE。此外,它还支持虚拟化X2APIC、免SMT攻击和额外的SPEC_CTL功能等。

12通道DDR5内存

每核心带宽至少比上代产品提升50%

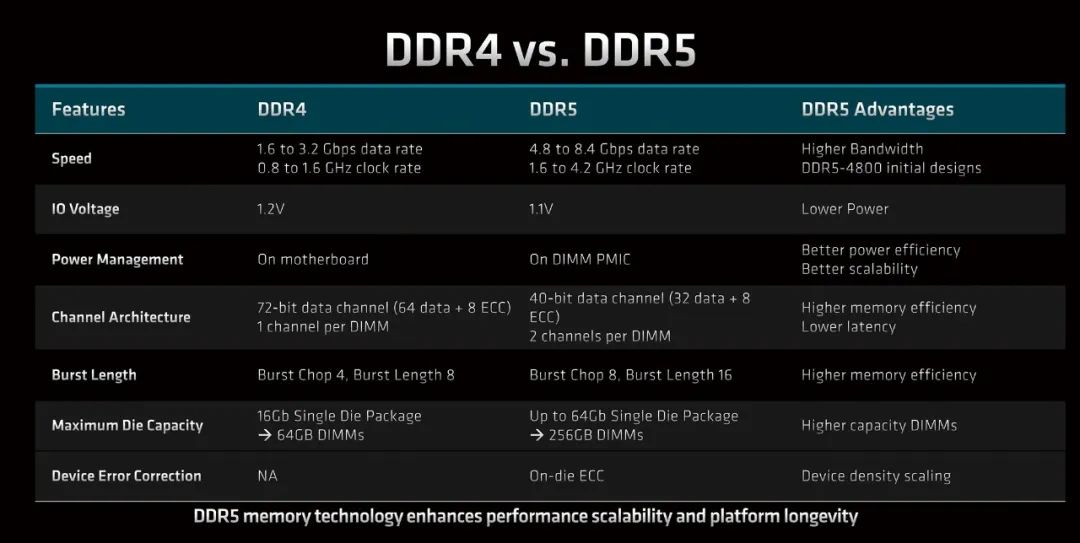

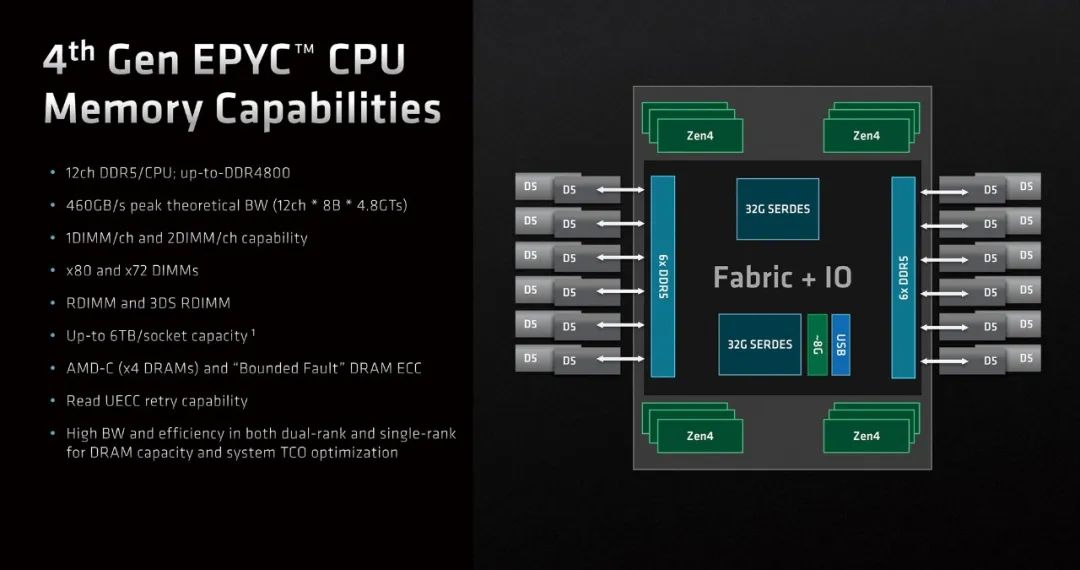

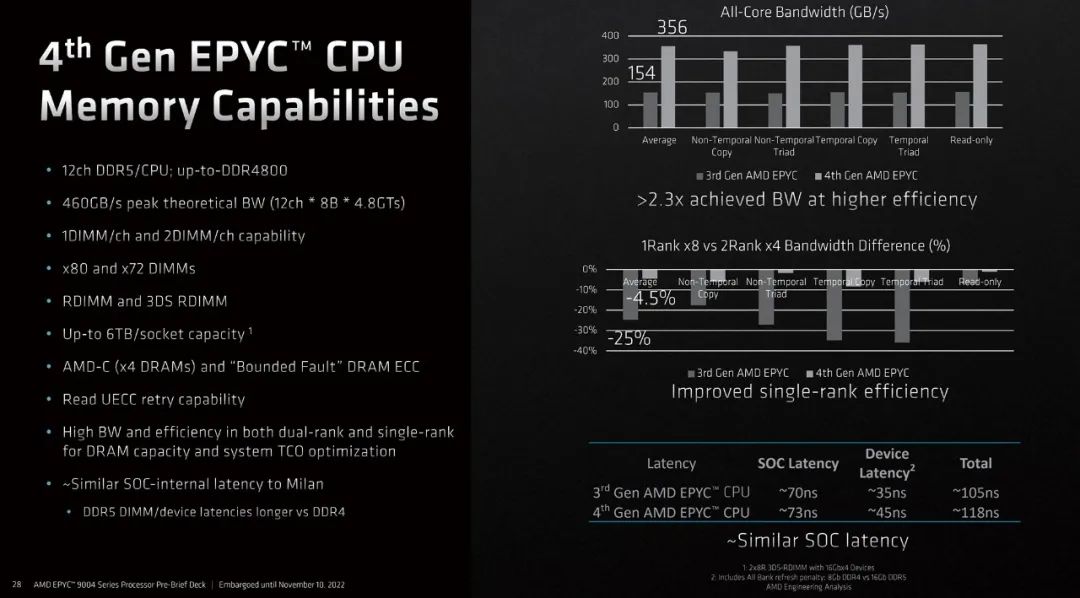

所有EPYC 9004系列处理器都支持12通道DDR5内存,相比上代支持的8通道DDR4内存有巨大进步。从内存带宽来看,DDR5的使用在很大程度上缓解了超多核心处理器内存带宽不足的情况。

▲AMD在EPYC 9004上全面启用DDR5内存

举例来说,上代EPYC 7763拥有64个核心128线程,支持8通道DDR4内存,内存总带宽为204.8GB/s,平均每核心3.2GB/s。新一代的EPYC 9654拥有96核心192线程,支持12通道DDR5内存,内存总带宽为460.8GB/s,平均每核心4.8GB/s。EPYC 9654在处理器核心数量更多的情况下,每核心内存带宽提升了50%。如果是48核心或者32核心产品,每核心内存带宽的提升会更大,这为内存带宽敏感型应用带来了极为不错的性能提升空间。

▲EPYC 9004的内存架构和特性一览

从AMD官方给出的实际测试数据来看,EPYC 7003系列的实际内存带宽大约为154GB/s,EPYC 9004则高达356GB/s,是前代产品的大约2.3倍。延迟方面,由于EPYC 9004支持的DDR5内存容量更大、通道数量更多,因此延迟有所上升。EPYC 9004的SoC延迟大约在73ns左右,设备延迟大约是45ns左右,因此总延迟在118ns左右,而EPYC 7003的对应数据分别是70ns、35ns和105ns。从整体上来看,EPYC 9004的延迟略高,但是考虑到它拥有更大的带宽,这一点是完全可以接受的。

▲EPYC 9004的内存性能情况

在内存容量方面,所有EPYC 9004系列处理器都支持高达6TB容量。不过目前AMD只给出了1DPC(DIMM Per Channel),也就是12个内存通道、12条内存插槽下的配置情况,内存最高支持12通道的DDR5 4800。至于2DPC配置,AMD宣称会在2023年第一季度再公布详细信息。不过考虑到EPYC 9004不小的面积,12通道DDR5内存插槽所占的体积以及接近400W的CPU供电所需要的PCB面积,未来出现24通道、48插槽的2DPC主板的可能性较低,并且6TB内存对大多数应用场景来说已经足够了。

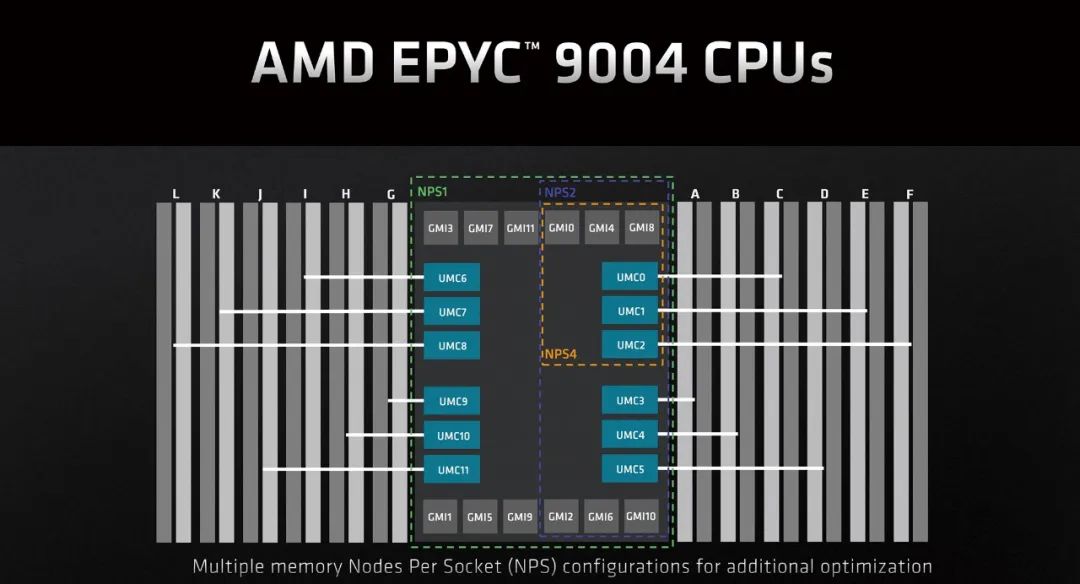

▲EPYC 9004设计有内存分区管理

最后再来看看内存分区。由于EPYC 9004系列处理器的规模很大,因此AMD也提供了NUMA域的管理和设置,使得用户可以在某些情况下对内存和核心进行调配。它包括了NPS1、NPS2和NPS4三种分区方式:NPS1就是整个处理器;NPS2是将处理器分为2个部分,每个部分有6个内存通道和6个GMI3接口;NPS4则是将处理器分为4个部分。

IO芯片和总线连接系统:采用最新的GMI3连接

AMD在EPYC 9004上继续采用大获成功的Chiplet方案。整个处理器除了CCD之外,还有一个IO芯片。EPYC 9004的CCD由台积电5nm工艺制造,这也是首个使用5nm工艺的企业级CPU产品。IO芯片也采用了台积电6nm工艺制造。

▲EPYC 9004架构简图和特性一览

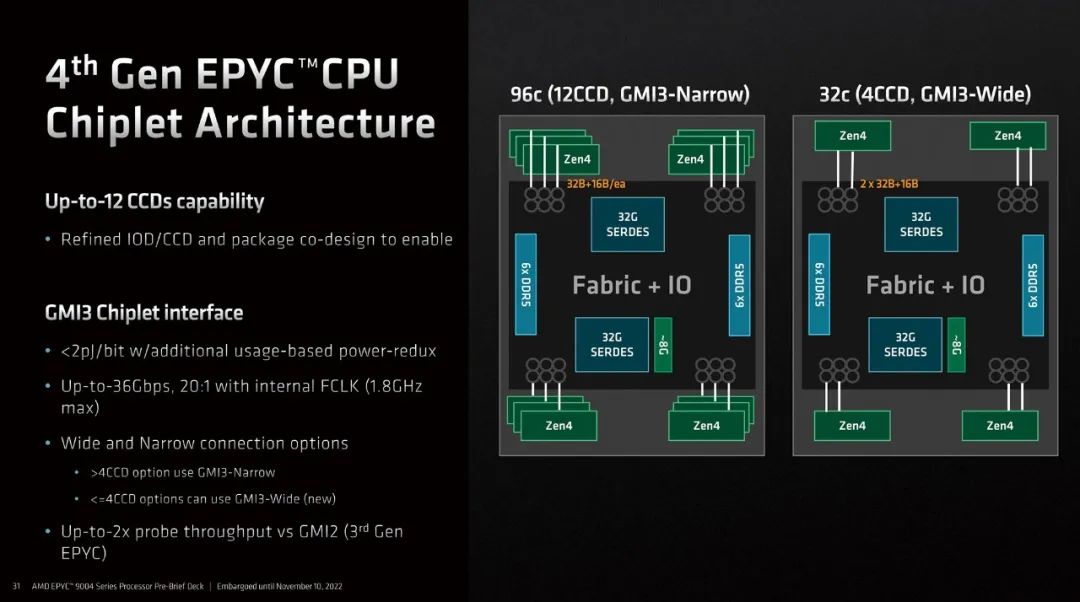

因为EPYC系列一直采用Chiplet方案,因此在CCD和IO芯片之间需要通信协议予以连接。上一代EPYC处理器采用的是GMI2总线,其IO芯片内部有8个GMI2总线端口,因此总共能支持8个CCD单元连接,每个CCD拥有2个GMI总线接口,可以根据需要进行配置。

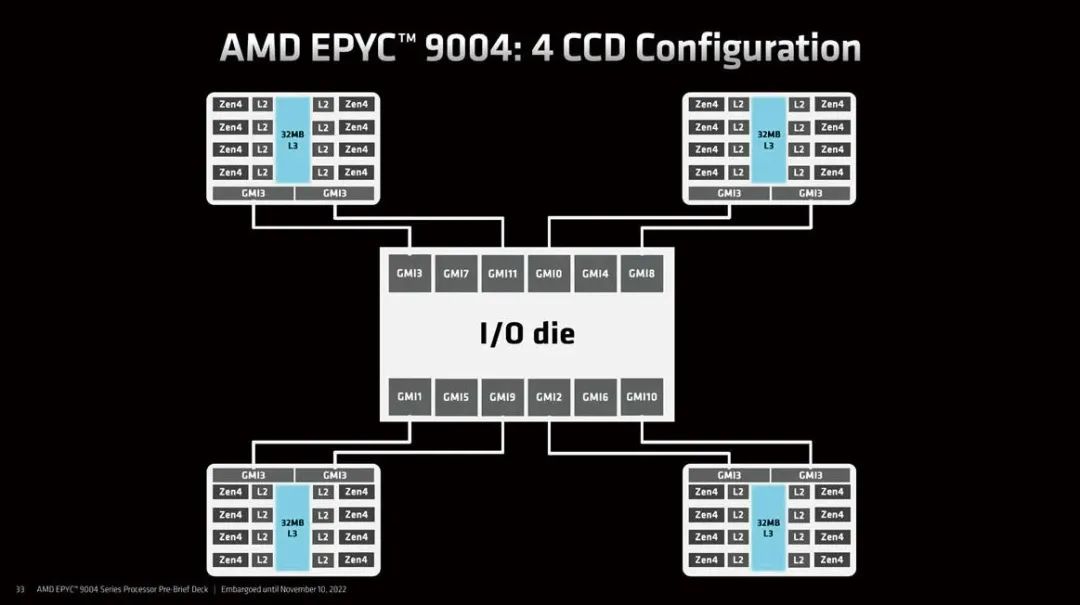

▲EPYC 9004的Chiplet连接图一览

EPYC 9004升级为GMI3总线。其中Zen 4架构的8个CCD和12个CCD采用的是每个CCD与1个GMI3总线互联,4个CCD架构中每个CCD通过2个GMI3总线进行互联,从而实现更高的互联带宽。对于核心数量较少的型号,这样的设计能够为CCD数量较少时,带来更大的互联带宽。IO芯片的GMI3总线端口数量升级到12个,因此可以最多连接12个CCD。

带宽和功耗方面,每个GMI3总线每周期可以实现32Bit的数据读取和16Bit的数据写入,能耗为2pj/bit。带宽方面最高可达36Gbps,和FCLK的频率比值是20∶1,最高可达1.8GHz。AMD宣称,GMI3的吞吐能力最高可达GMI2的2倍。

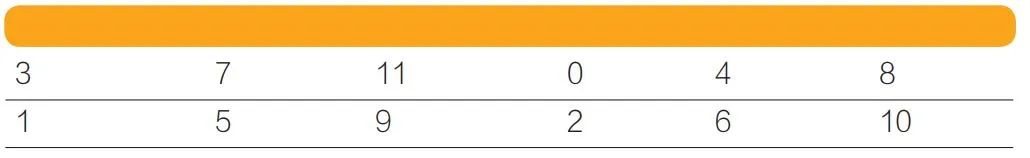

值得一提的是,IO芯片上的GMI3端口排序是经过设计的。它的端口序号排列如下:

显然,GMI3的端口并不是按照常规的从小到大或者从大到小排列的。AMD这样做的原因,是考虑到CCD和IO芯片的距离和延迟。以96核的EPYC 9654为例,每个CCD有8个处理器核心,12个CCD分布在IO芯片两侧,每侧各6个CCD。考虑到几何和空间形状,将优先使用IO芯片周围的某几个端口。比如有8个CCD,将使用GMI0~GMI7这几个端口,位于中间和最远端的GMI8、GMI9、GMI10和GMI11反而会空余。AMD还提到,靠近IO芯片的CCD位置将被优先使用,这意味着如果是8个CCD,那么最远4个位置上的CCD要么彻底被屏蔽,要么干脆就是占位用的晶体块。

AMD还特别对连接模式进行了说明。GMI3有两种连接模式,一种被称为窄连接模式,主要用在大于4个CCD也就是32核心以上的处理器上;另一种被称为宽连接模式,它是新加入的,主要用在小于等于4个CCD,也就是32核心以下的产品。

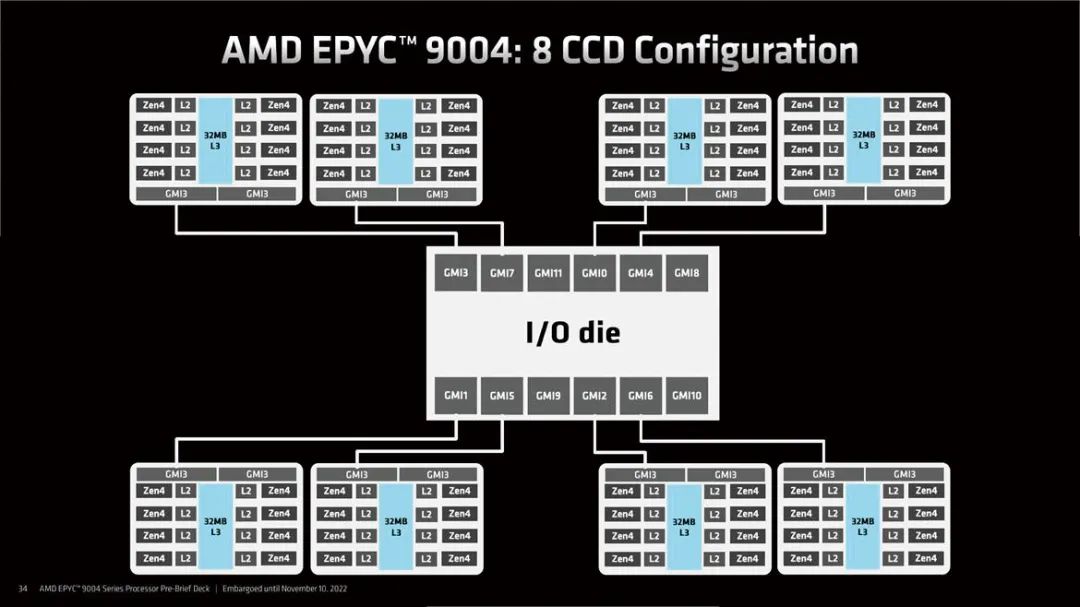

▲EPYC 9004的8CCD连接模式,注意GMI11和GMI9等端口的空闲。

在窄连接模式中,如果8个CCD连接到IO芯片上,就像上文提到的那样,将使用GMI0~GMI7进行连接。此时每个CCD的1个GMI3端口将被激活,并与IO芯片相应的GMI3端口进行连接,空余剩下的4个端口。

▲EPYC 9004的4CCD连接模式,每个CCD采用2个GMI总线连接IO芯片。

在宽连接模式中,每个CCD的2个GMI3端口将被激活,并和IO芯片上的GMI3端口进行连接。以4个CCD为例,每个CCD的第一个GMI3端口将先和GMI0~GMI3端口连接,然后第二个GMI3端口会和GMI8~GMI11端口连接,GMI7、GMI5、GMI4和GMI6端口将被闲置。

全新的SP5插槽:更大、更稳固

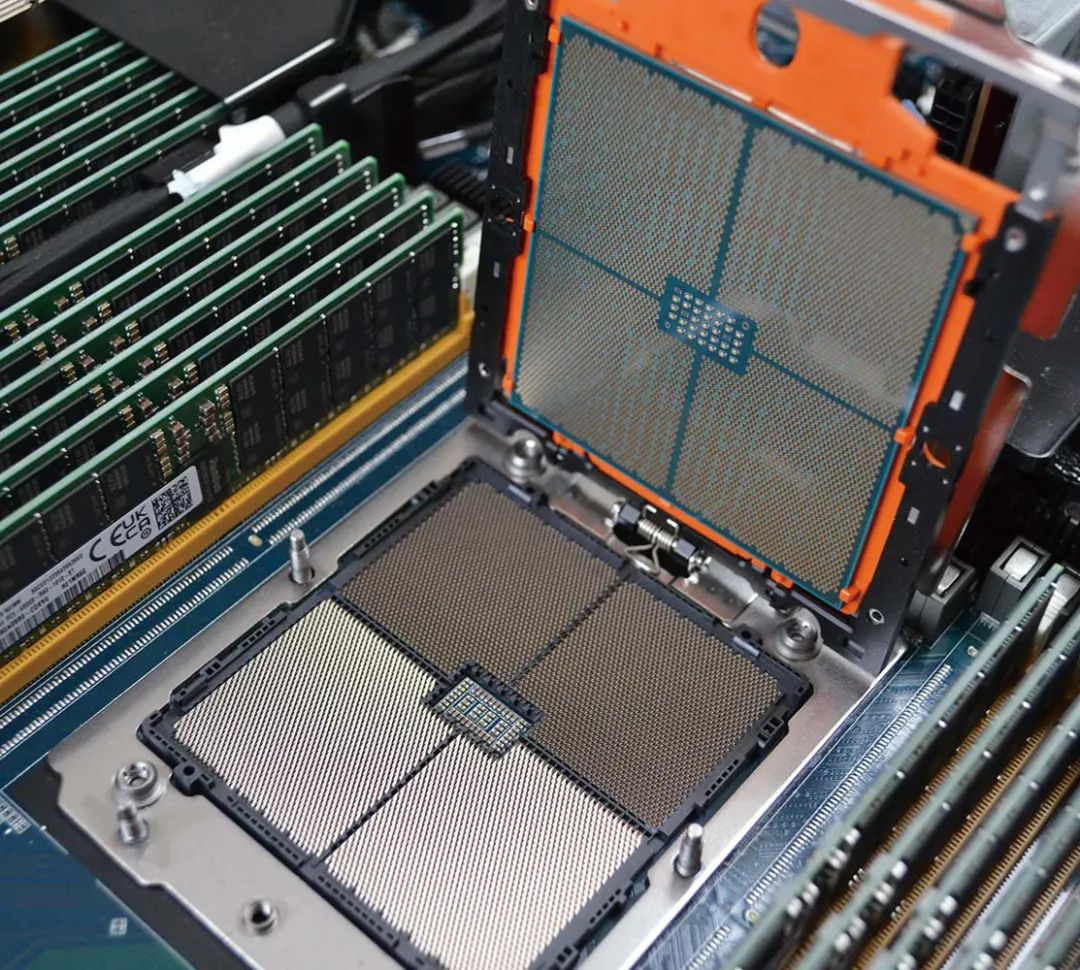

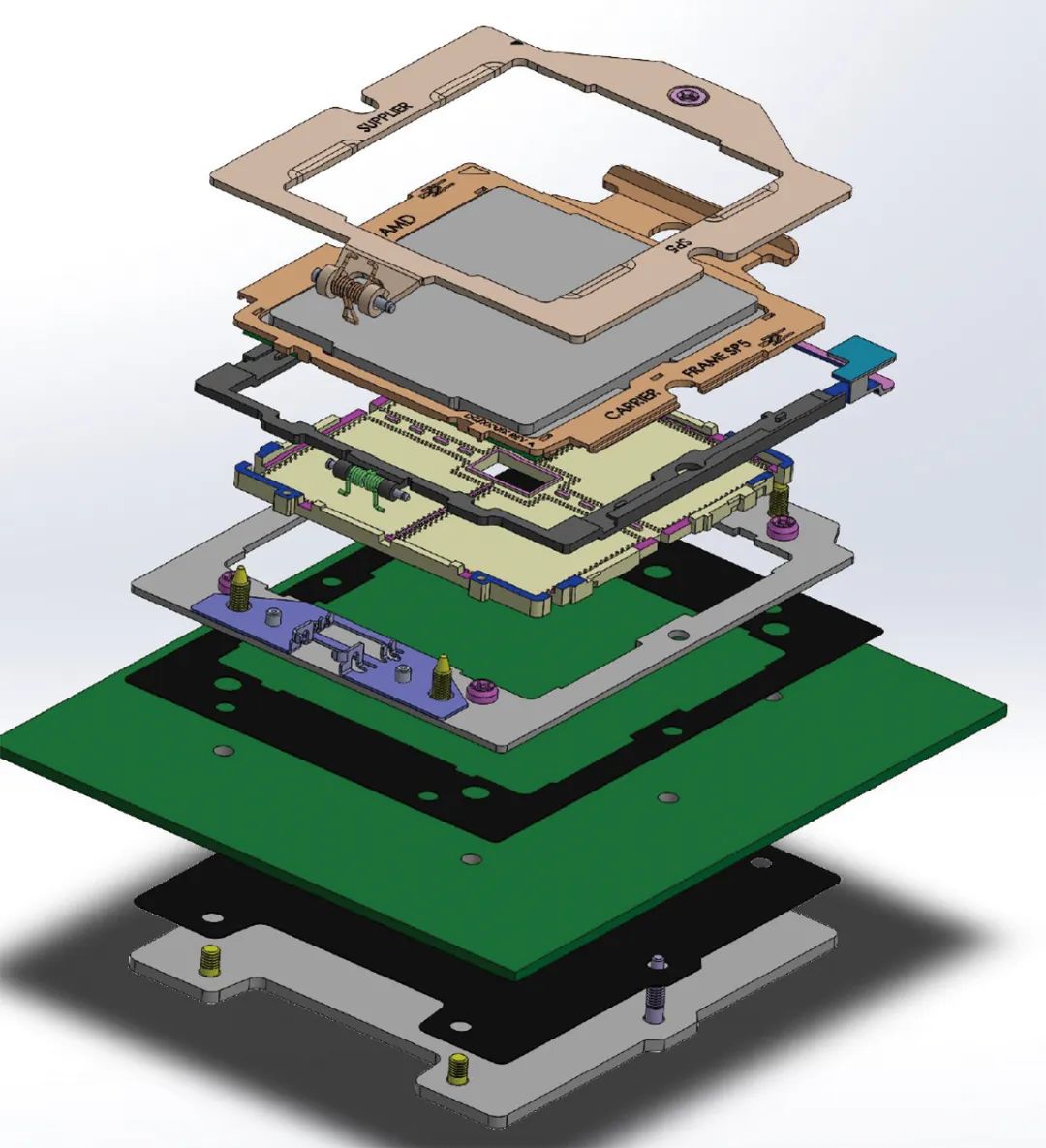

EPYC 9004的插槽上也被更新。新插槽被称作Socket SP5,不兼容上一代Socket SP3。不兼容的原因主要是因为EPYC 9004系列处理器的基板为了放下12个CCD和IO芯片,变得更大。更多的内存通道、供电和CPU核心,也要求有更多的触点来传输数据。

▲Socket SP5和插入其中的EPYC 9004处理器,共有6096个触点。

官方数据显示,Socket SP3的长宽分别是58.5mm、75.4mm,面积为4410.9mm2,包含了4094个触点或者弹性接触片。相比之下,Socket SP5的长宽分别为72mm、75.4mm,总面积达到5428.8mm2,包含了高达6096个触点或者弹性接触片。Socket SP5的CPU供电能力高达400W,这刚好对应了EPYC 9004系列处理器的最大功耗值。

▲ AMD给出了不同接口处理器的散热器示意图,可见SP5的散热器更大。

▲Socket SP5结构分层图

Socket SP5在安装方式上没有做出太多改变,依旧采用先让处理器模块“滑入”扣具,然后扣下并固定在主板上的方式。这种安装方式和桌面处理器需要手动将处理器放入插槽的方法完全不同,起固定作用的主要是扣具。值得注意的是,之前在Socket SP3处理器上出现过3个紧固螺丝由于紧固不到位导致接触不良,从而使得某些内存通道消失的情况。因此在Socket SP5上,AMD选择了多达6个紧固螺丝来实现主板和CPU的稳定连接,并平衡应力。相比上代产品,Socket SP5在耐久性方面更为出色。

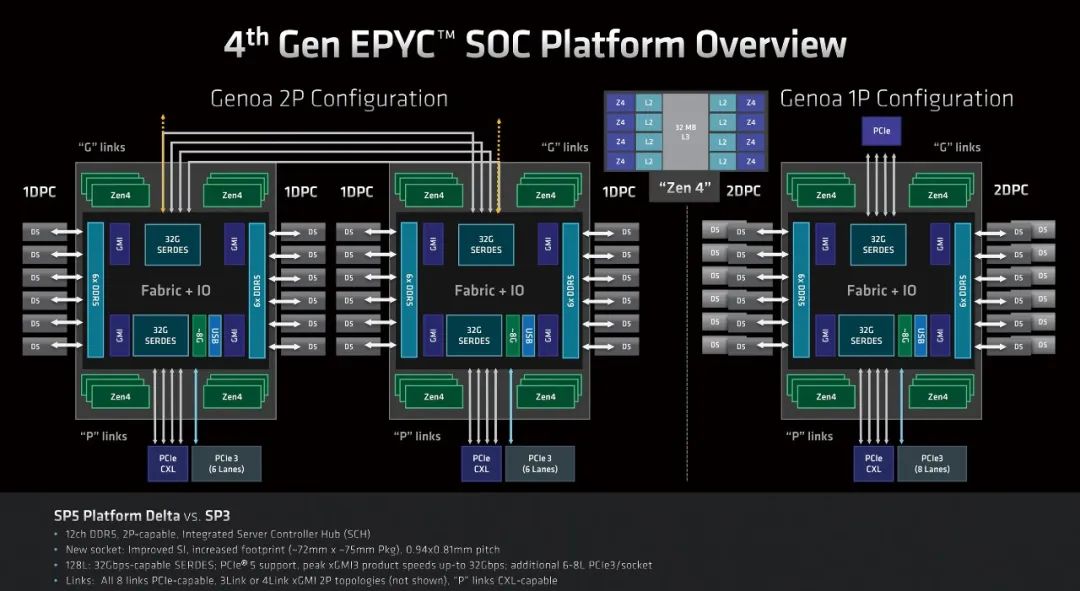

双CPU互联:最多对外提供160条PCIe 5.0总线

再来看有关双CPU互联的内容。EPYC 9004系列中2P型号的处理器可以搭建双路系统,而在2个CPU的互联上,它有一些新的变化。

▲AMD EPYC 9004系列处理器的1P、2P配置图

▲AMD依旧采用IF总线连接2个处理器,不过EPYC 9004多了很多功能和设置。

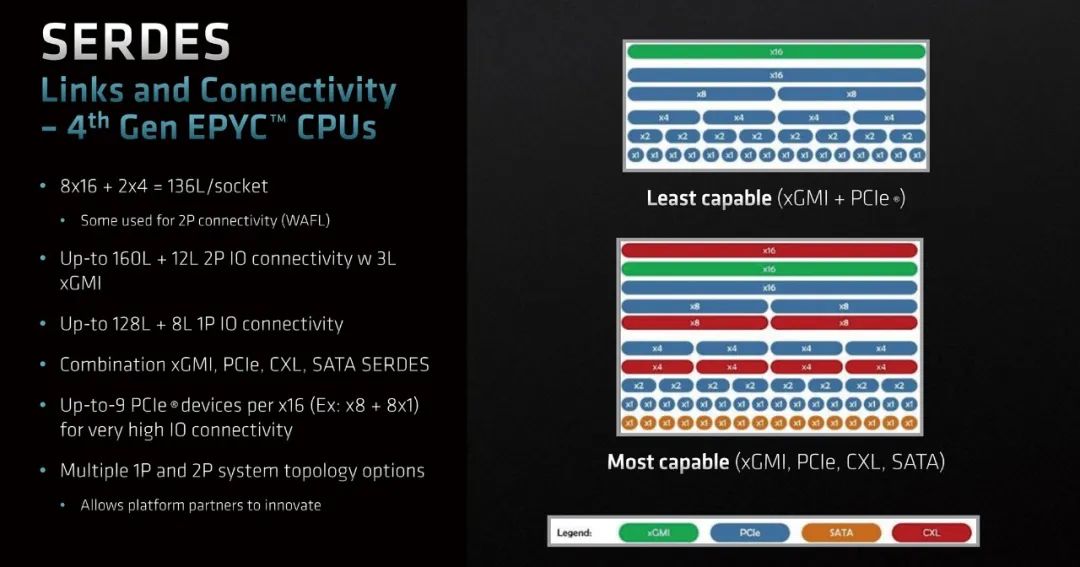

每个EPYC 9004处理器能够对外提供128条PCIe 5.0通道。当组建2P系统时,通过IF总线使用的SerDes(串行器-解串器,AMD的SerDes支持两种类型的连接,一种类型是支持标准的GMI或者PCIe接口、Infinity Fabric总线等,另一种则是支持其他类型的接口,包括SATA、CXL等,用户可以根据需要进行配置),最多有64条通道被设置为4条Infinity Fabric总线(后文简称IF总线)来实现2个CPU的互联传输。也就是说,在AMD的定义中每一条IF总线实际上相当于PCIe 5.0 x16的规格。

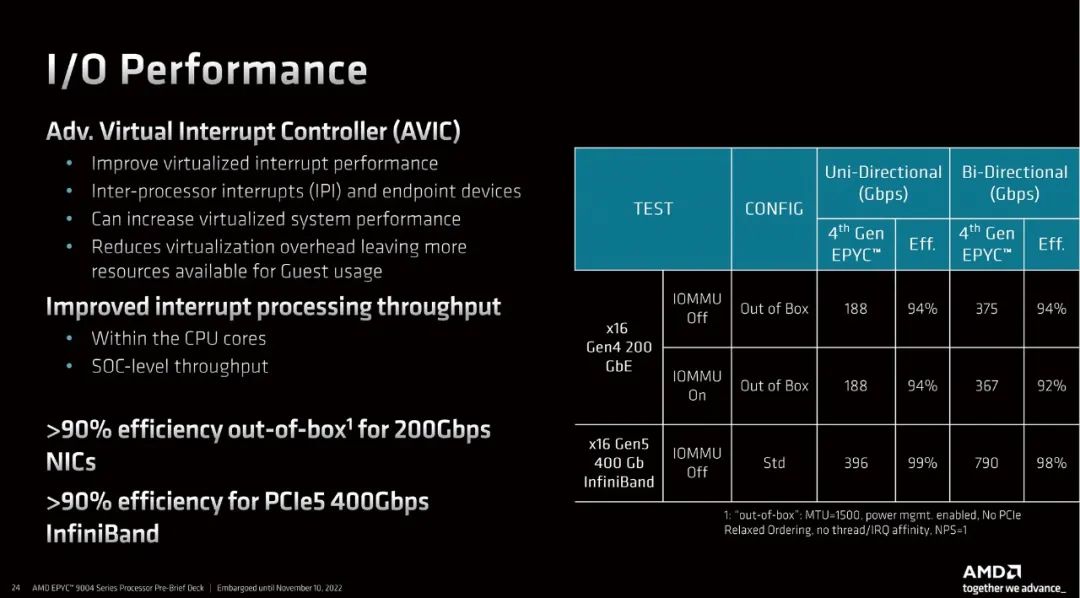

▲EPYC 9004的IO性能一览

早期的IF总线采用的是PCIe 3.0 x16规格,带宽较低。在升级到PCIe 5.0 x16规格后,其带宽大增,所以可能有部分用户认为3条IF总线已经足以承担2个CPU的互联工作。AMD允许用户自行选择启用3条还是4条IF总线实现2P互联操作。如果是3条的话,那么多余的1条IF总线可以被释放为PCIe 5.0 x16通道。这样一来,两个CPU在3路IF总线连接的情况下,每个CPU最多可以空余80条PCIe 5.0通道,2个CPU就是160条。另外,IO芯片还能够对外释放12条PCIe 3.0通道。

▲EPYC 9004处理器的扩展和连接都非常自由

AMD对走线也进行了更新。现在IO芯片中的总线控制器(SerDes)被分为2个,体现在CPU的物理结构上,就是背部触点两侧都可以连接总线输出。在上一代EPYC 7003上,只有一侧可以输出IF总线或PCIe总线,并往往在主板上部。此时如果要连接主板下部的设备,就需要较长的走线并增加主板设计的复杂性。在EPYC 9004上,由于有两个总线控制器且线路可以从CPU两侧走,因此更方便。AMD将CPU上部的线路称为P总线,下部称为G总线。其中P总线往往用于组成IF总线连接CPU,G总线用于连接外部设备。当然厂商也可以自由设置,比如使用“2P+2G” 的方式来连接CPU,或者其他厂商认为方便的设计亦可。

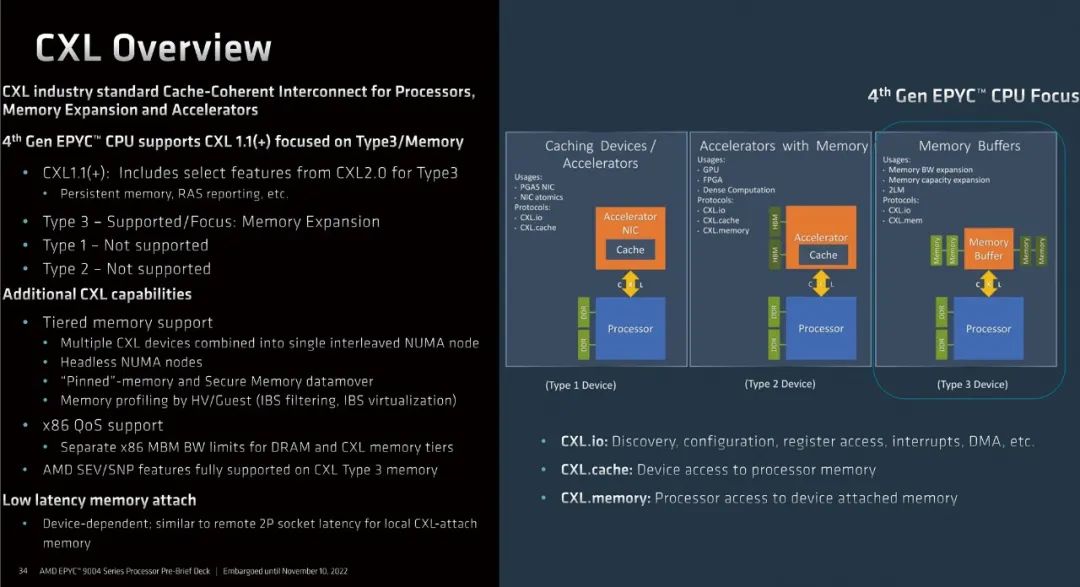

CXL 1.1+:提供超大规模的内存寻址空间

在互联技术特性上,EPYC 9004对CLX 1.1+的支持是一个亮点。本刊之前介绍过有关CXL的技术内容,CXL的全称是Compute eXpress Link,它是一个开放的行业标准,主要用于在CPU和加速单元(GPU、DPU)或者一些IO设备之间提供高速缓存一致性互联,同时允许CPU在连接设备的相同内存区域上工作,从而提高性能和电源效率,并降低软件复杂性,减少数据移动次数。该规范以PCIe 5.0作为技术基础,最新修订版本的CXL 3.0则以PCIe 6.0作为技术基础。

CXL规范的推出速度非常快,在CXL 1.0技术还未准备好之前,CXL 2.0技术就已经到来,新规范要求在总线的SerDes级别提供内置支持,从而实现和远程内存组的低延迟连接。因此,AMD不得不在新处理器的设计后期重新设计了CXL部分功能,还融入了包括持久内存和RAS报告等功能,但是其余部分则不能全部支持,因此AMD称之为CXL 1.1+。目前AMD的CXL总线基于PCIe 5.0规范,和PCIe 5.0共用物理接口。

▲ AMD的CXL 1.1+只支持第三类,也就是内存扩展。

CXL支持三类设备,第一种常用于网卡这类高速缓存设备,第二种常见于GPU、AI等应用的内存加速器,第三种是内存扩展控制器,通常作为内存缓冲器,常用作内存带宽或是容量的扩展。EPYC 9004目前只支持第三种方案,允许用户将远程内存作为本地内存进行寻址,并且允许将多个CLX Type-C设备聚合成一个交错的NUMA节点,还支持“headless NUMA”节点。其他功能包括能够优化本地内存和CXL内存之间延迟差异的QoS机制,支持AMD的SEV-SNP密钥扩展和AES-256-XTS等功能。

AMD目前最多允许将64个PCIe 5.0通道分配给CXL 1.1+,单个CXL 1.1+允许最多16个通道,因此单个CXL 1.1总线带宽为双向128GB/s。如果启用全部64个通道的话,带宽会高达双向512GB/s,这已经高出了12通道DDR5内存的460GB/s了。考虑到EPYC 9004高达96个CPU核心对内存带宽的需求,这正是AMD支持CXL 1.1+的意义所在。

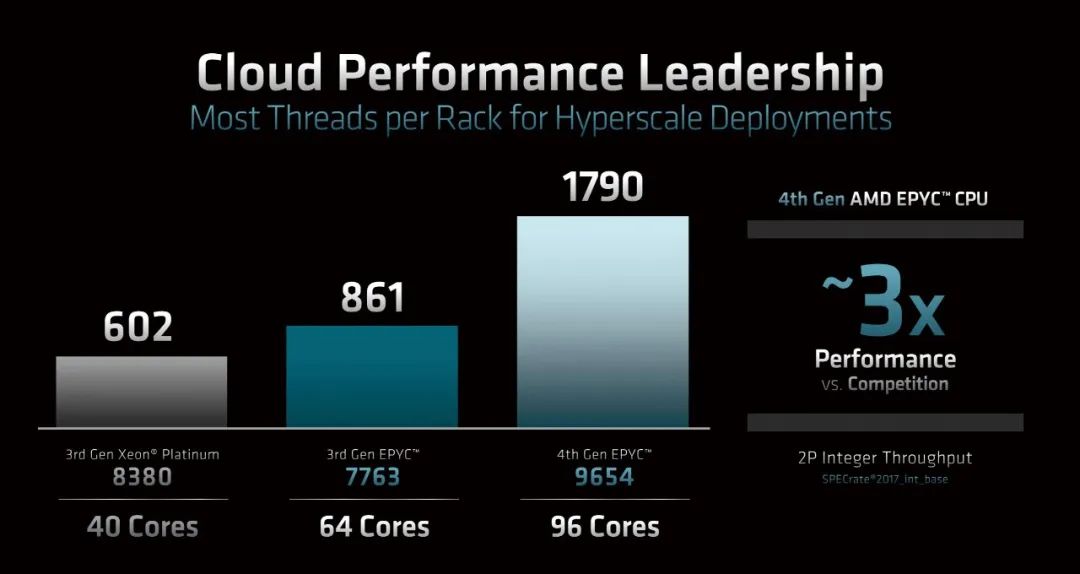

性能预览:轻松抛离竞争对手

在架构介绍部分,AMD提及了不少性能方面的信息,不过最终还得看综合性能情况。AMD选择了英特尔第三代至强可扩展处理器,也就是Ice Lake-X架构的产品进行对比。

▲ EPYC 9004在云端方面的性能大幅度领先

▲AMD宣称EPYC 9004在多项性能中领先

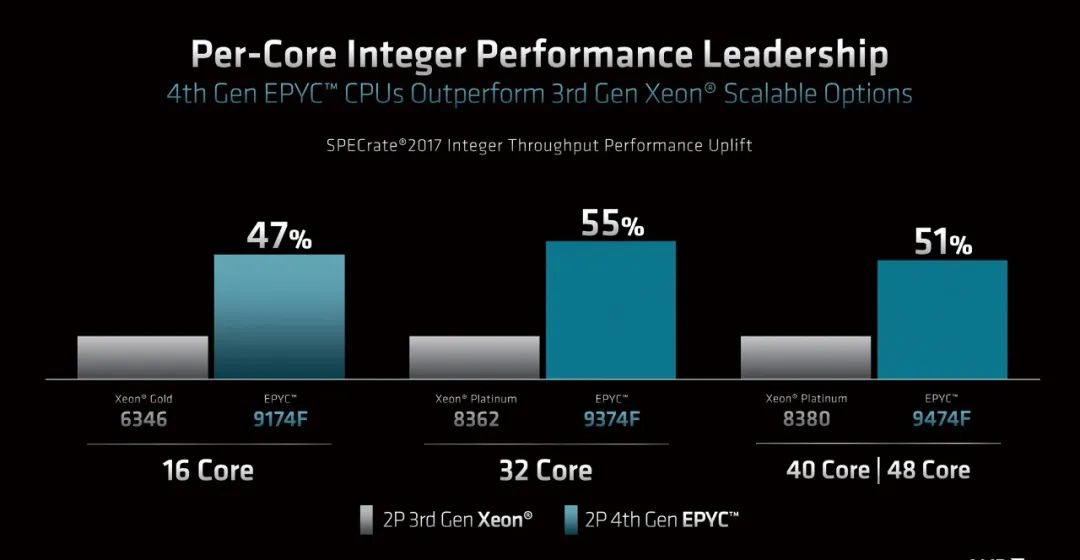

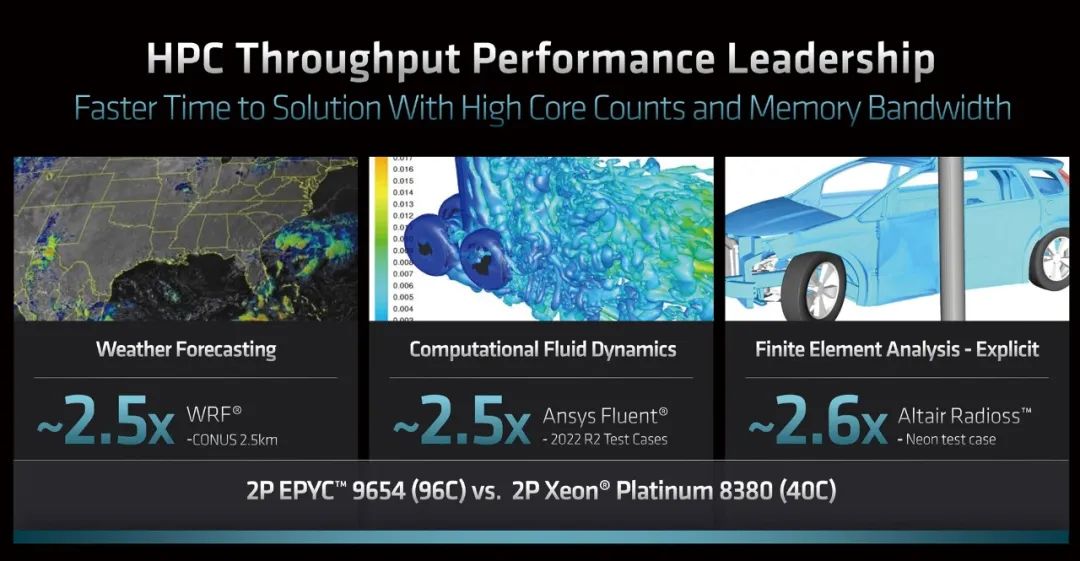

首先来看单核心性能。AMD使用了16、32、40/48核心的处理器进行对比。EPYC 9004系列的不同型号处理器在整数、浮点性能方面超越英特尔产品最多可达55%、96%。虚拟化性能方面,EPYC 7003的表现就足以抗衡英特尔产品,EPYC 9004的性能更是英特尔产品的2.8倍之多。在FSI模拟、3D渲染和商务(MySQL业务查询)方面,EPYC 9654的性能分别是英特尔至强铂金8380的大约2.1倍、2.4倍和2.7倍。HPC性能方面就更不用多说了,2P配置的EPYC 9654在天气预报、计算流体和有限元分析方面分别是2P配置的英特尔至强铂金8380的大约2.5倍、2.5倍和2.6倍。HPC单核心性能方面,同样是这三项测试,32核心的EPYC 9374F性能是同为32核心的至强铂金8362的2倍、1.7倍和1.7倍。

▲EPYC 9004系列不同型号处理器的单核心整数性能都大幅领先对手

▲EPYC 9004系列不同型号处理器的单核心浮点性能同样大幅领先

▲HPC性能方面,EPYC 9004实现了对英特尔处理器的碾压态势。

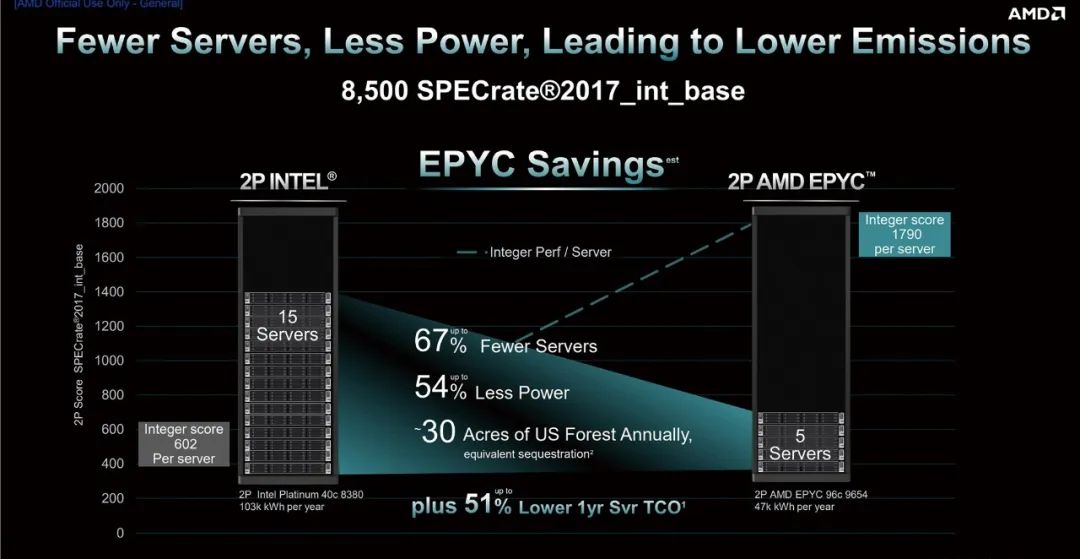

此外,AMD还评估了空间和电能需求。在同时处理1995个虚拟化需求的时候,2P的EPYC 9654处理器只需要5台服务器即可完成,与之对应的英特尔至强铂金8380则需要15台服务器,AMD节约了67%的机架数量、52%的电能消耗(相当于34英亩森林所释放的二氧化碳值),降低了40%的1年服务TCO。

▲AMD还评估了空间和电能需求,EPYC 9004系列更是大获全胜。

在同样性能的情况下,比如在SPECreat 2017整数基准测试中同样获得8500分,AMD只需要1P EPYC 9654的处理器使用10台服务器即可,英特尔则需要2P的至强铂金8380的处理器使用15台服务器,这意味着AMD节约了67%的处理器数量、20%的核心数量、50%的能源消耗和46%的1年服务TCO。

AMD还展示了EPYC处理器在产业环境方面的情况。目前已经有数百家企业使用或者正准备使用AMD的产品,同时媒体和内容、制造业、5G和金融服务等行业都在使用AMD EPYC产品持续创造价值。历经四代进化,AMD EPYC终于开创了一个非常不错的产业环境,并正在逐渐拓展自己的市场范围。

总结:强大的产品无须多言

从已知的信息和规格来看,EPYC 9004系列处理器代表了当前最先进、最强大的计算性能,无论是架构设计还是产品性能都没有什么可挑剔的地方。

▲EPYC 9004的晶元结构示意图,不同的部分清晰可见。

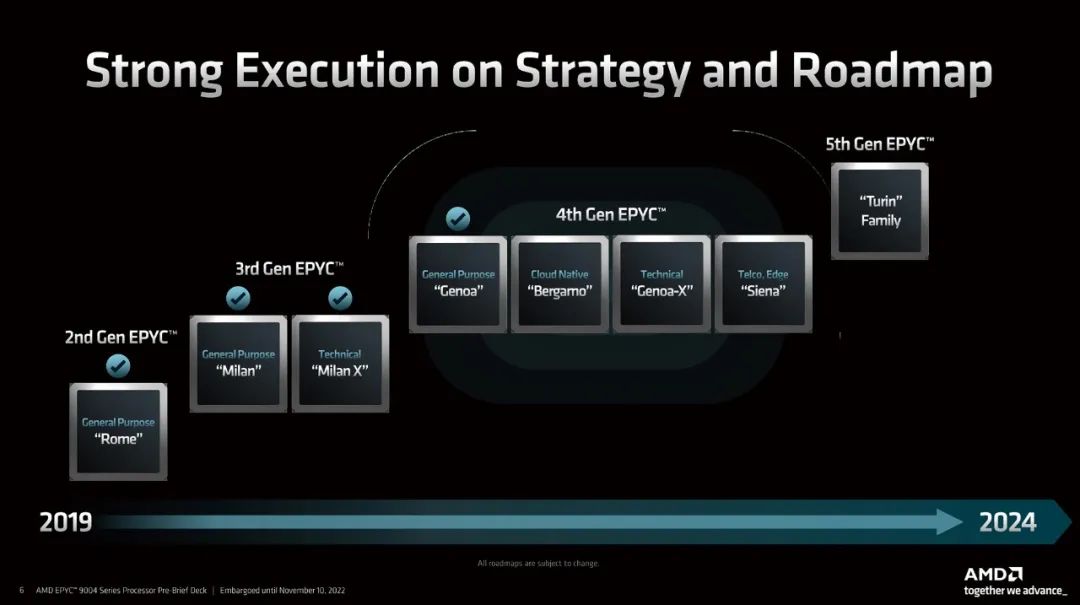

▲AMD EPYC产品路线图一览

AMD还给出了EPYC未来的产品路线图。目前AMD发布的EPYC 9004系列是代号为“Genoa”的产品。接下来,AMD还将陆续推出采用3D V-Cache技术的“Genoa-X”,面向云计算服务的“Bergamo”(贝尔加莫),以及面向电信基础设施和边缘计算的“Siena”(锡耶纳)。在2023年~2024年,AMD将推出全新设计的Zen 5架构以及第五代EPYC处理器家族,代号“Turin”(图灵)。AMD在前三代EPYC大获成功之后,已经开始计划利用EPYC进入更多市场,继续和英特尔等厂商展开正面厮杀。这样的竞争态势,显示出AMD强大的进取心。就像全新进化的AMD新品牌平台 “同超越,共成就 _”(“together we advance_”),持续进步的AMD还会带给我们怎样的惊喜呢?一起期待吧!

编辑:黄飞

-

AMD EPYC嵌入式9004和8004系列处理器介绍2024-12-18 3116

-

第五代AMD EPYC处理器预计下半年发布2024-09-18 1667

-

AMD EPYC处理器:AI推理能力究竟有多强?2024-03-15 1482

-

AMD第四代EPYC(霄龙)系列处理器介绍2024-01-29 4099

-

AMD EPYC 9554处理器参数分析2023-11-20 5900

-

AMD推出全新AMD EPYC(霄龙)8004系列处理器2023-09-20 1945

-

AMD 3D V-Cache技术的第四代EPYC处理器性能介绍2023-08-14 1253

-

全新亚马逊EC2 M7a实例使用第四代AMD EPYC处理器2023-06-20 2032

-

AMD 推出第四代 AMD EPYC 处理器,为嵌入式网络、安全、存储与工业系统提供卓越性能2023-03-15 1562

-

第四代AMD EPYC处理器独家测试2022-12-15 4277

-

AMD EPYC 9004系列正式发布:升级支持DDR5内存,最高频率4800MHz2022-12-06 3879

-

新思科技携手AMD发布第三代处理器AMD EPYC 70032022-04-12 3210

-

第四代移动通信系统有哪些关键技术?2021-05-26 3059

-

英特尔正式推出第四代酷睿Haswell处理器2013-06-03 1831

全部0条评论

快来发表一下你的评论吧 !