宽禁带半导体概述 碳化硅寿命面临什么挑战

制造/封装

描述

引言

功率半导体作为电力电子行业的驱动力之一,在过去几十年里硅(Si)基半导体器件以其不断优化的技术和成本优势主导了整个电力电子行业,但它也正在接近其理论极限,难以满足系统对高效率、高功率密度的需求。而当下碳化硅(SiC)和氮化镓(GaN)等宽禁带半导体以其优异的电学和热学特性使得功率半导体器件的性能远远超过传统硅材料的限制。然而,目前宽禁带半导体的市场渗透率还比较低,只有当相应的制造技术足够成熟,成本具有竞争力时,才会实现大规模应用。足够的技术成熟度则意味着宽禁带(WideBandgap, WBG)半导体器件还需要不断改进和优化,今天我们就来聊聊碳化硅目前在可靠性和寿命方面有哪些主要的限制。

宽禁带半导体概述

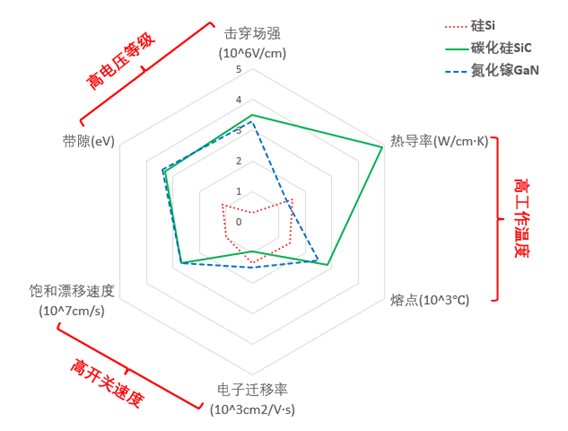

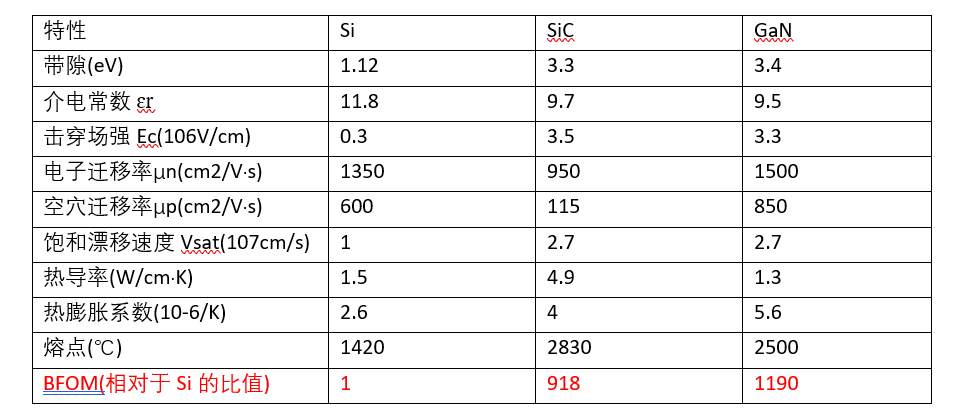

宽禁带半导体,指的是价带和导带之间的能量偏差(带隙)大,决定了电子从价带跃迁到导带所需要的能量。更宽的带隙允许器件能够在更高的电压、温度和频率下工作。下图展示是目前较为热门的宽禁带半导体材料,碳化硅和氮化镓相对于硅的特性对比[1]。

这张图想必大家都很熟悉了,这里我们再一起回顾一下(今天我们主要围绕碳化硅展开)。

首先宽禁带半导体以其带隙命名,其禁带宽度为硅的3倍左右,意味着需要更大的能量来激发电子导电,这也解释了为什么WBG材料的击穿电场强度是传统硅材料的10倍。另外,禁带宽度也关系到最大工作温度,禁带宽度越大意味着本征载流子浓度越低,从而宽禁带半导体可以运行在比硅基更高的温度,因为功率半导体保持其性能的运行温度的前提是其本征载流子浓度低于电离掺杂浓度。

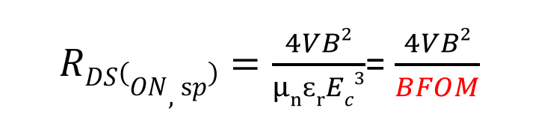

我们从理论上评估半导体材料时常用到Baliga优值(BFOM—Baliga’s Figure Of Merit),我们可以通过它来理解碳化硅的优势。

其中,RDS(ON,sp)是我们所说的比导通电阻,Ec是电场强度,μn是电子迁移率,ɛr是介电常数。

从上表[1]我们可以看到,WBG由于其优越的BFOM,RDS(ON,sp)低于硅,在相同的芯片尺寸下,WBG功率器件的RDS(ON,sp)要小得多,从而导通损耗更低。对于给定击穿电压和RDS(ON),WBG拥有比硅更小的芯片尺寸,可实现更小的结电容和栅极电荷,从而降低了开关损耗。

碳化硅作为新一代的半导体材料,凭借其宽禁带、高击穿场强、高热导率等优异的性能,使得电力电子系统能够工作在更高电压、更高频率和更高功率密度。但相比于硅基器件,从碳化硅到碳化硅器件的整个生产工艺和技术还没有达到硅那样的成熟度,所以碳化硅的可靠性并没有表现得很突出,寿命甚至比硅基的小。

碳化硅可靠性

经过半个多世纪的发展,硅材料到器件的整个制造工艺已经相当成熟和完善,而碳化硅在这期间只是保持着研究和探索,直到近十多年才开始规模应用。随着碳化硅功率器件(主要集中在SiC MOSFET 和SBD)不断进入市场,应用中在验证它优异电学特性带来的优势时,对于其可靠性和寿命的考量也越来越重要,例如经常被提及的阈值电压漂移,短路鲁棒性以及封装技术等,这些因素使得碳化硅的可靠性受到了极大的挑战。

阈值电压漂移(栅极氧化层可靠性)

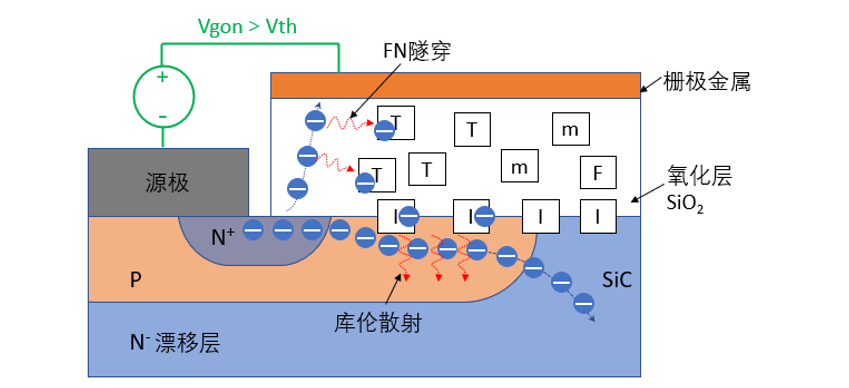

与硅相比,碳化硅具有更高的临界击穿场强以及其带来的更高的耐压和相同耐压下更薄和更小的漂移区电阻,但是更高的临界场强意味着碳化硅MOSFET的栅极氧化层面临着更高的电场强度。由于SiO2/SiC的介电常数比值ɛs/ɛox≈2.5,这意味着氧化层内部的电场强度约为碳化硅半导体中的2.5倍。SiO2的击穿电场强度约为10MV/cm,但基于目前的技术,为了保证良好的可靠性,碳化硅MOSFET最大允许氧化物的正向偏置约为3.5~4.0MV/cm,负偏置约为1.5~2.0MV/cm。

关于栅极氧化物的可靠性,我们实际应用中更为关注栅极阈值电压漂移。由于制造工艺导致SiC/SiO2界面的界面态密度(Dit)比Si/SiO2界面高出了近2~3个数量级,由此引起的栅极阈值电压不稳定性严重影响了碳化硅的可靠性。

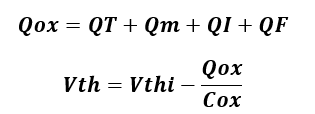

关于阈值电压漂移的机理[2],大致解释如下。我们认为碳化硅热生长的氧化物包含着四类正电荷:移动电荷(m)、固定氧化物电荷(F)、捕获氧化物电荷(T)和界面态电荷(I)。

时间关系的阈值电压可以表示为

Vthi为初始阈值电压,Cox为栅极氧化层比电容。理论上,在驱动和高温条件下较大的正Vth位移归结于两个方面。首先是电子直接隧穿进入SiC/SiO2界面附近的氧化物陷阱;另外,在较薄栅极氧化层的情况下,Fowler-Nordheim隧穿电流会向氧化层注入额外的电子,然后引起进一步的Vth位移。第二,在高温和栅极偏置条件下的显著Vth位移归结于在工作时间内额外氧化物陷阱的激活。

阈值电压Vth的不稳定性由两个部分组成:永久部分和可恢复部分。前者为偏置温度不稳定性(BTI: BiasTemperature Instability),后者为Vth的迟滞现象。

永久部分

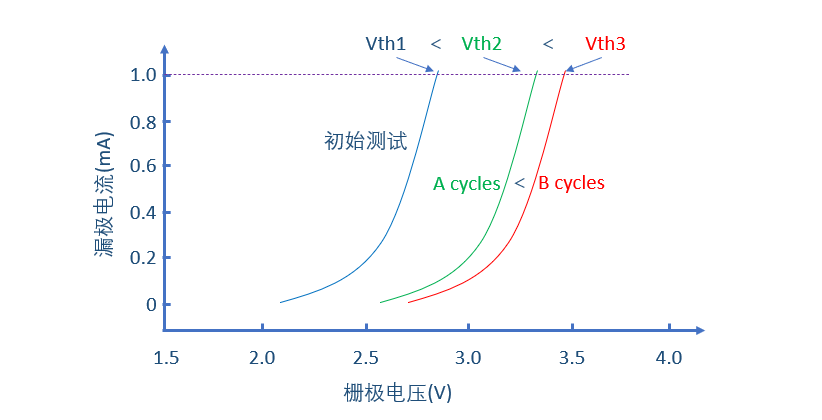

当器件满足设计需求时,我们更多关注的便是可靠性,其中对于栅极可靠性经常通过高温栅极偏置验证,在高温环境(如175℃)下,对栅极施加特定的正栅极电压,在没有漏极电流的情况下存储1000小时。在此类“静态”的栅极偏置测试中,正栅极电压可以导致Vth正偏,相反,负栅极电压会导致Vth向下偏移。通常,这样的情况下阈值电压偏移在几百mV,这对于设计良好的栅极氧化层而言属于正常范围。然而,对于实际应用而言,HTGB并不能反映阈值电压不稳定性的实际情况,功率半导体器件在应用中大多处于正栅极偏置和高结温(Tj)的脉冲电流下,这种情况将会导致更大的Vth偏移,此处功率循环(PC)在评估模块不同材料相关的失效机制同时也能够更贴近实际工况地考量Vth偏移及其带来的影响。在经过一定测试PC循环后,Vth正向偏移,可以用下图概念性地描述下。

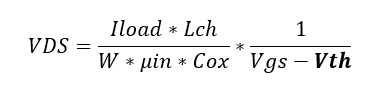

Vth的偏移会影响碳化硅MOS的导通电阻,即导通压降VDS。我们可以粗略地将VDS表示为

其中,Lch为沟道长度,W为沟道宽度,Cox为氧化层比电容,μin为反型层电子迁移率。Lch、W和Cox我们可以认为器件的常数,而电子迁移率随温度升高而降低。可以看出阈值电压Vth的正向偏移会增大碳化硅MOSFET的导通电阻,从而增加导通损耗,继而增加结温。比如在功率循环中,随着Vth不断增大,导通电阻随之不断增大,从而ΔTj将不断增大,更大的结温又将加速阈值电压的退化,直到器件某一点出现失效。这样一直由于阈值电压偏移导致的正反馈,对于碳化硅MOSFET的可靠性产生了严重的影响。

可恢复部分

除了永久性的阈值电压偏移,还发现在碳化硅MOSFET的开关过程中Vgs,on和Vgs,off应力下也会导致阈值电压的偏移。Vth的迟滞是可以完全恢复的,与其关断时的启动电压也就是Vg,off有关,并随着正栅极电压的增加而略有增加,此外研究表明跟具体的器件结构也有关系。

Vth的迟滞现象取决于界面态的充放电情况,当Vg,off为负值时,器件处于积累状态,供体陷阱捕获空穴,Vg,off负得越多,捕获空穴越多。当器件从积累到耗尽,再变成反转时,费米能级快速穿过碳化硅带隙,使得界面态进入非稳态,并发生供体陷阱的放电,导致Vth减小,Vg,off越小,Vth就越小。这将影响到碳化硅MOSFET的动态性能,Vth的减小变相地加快了开启,降低了开通损耗Eon;但同时也可能导致漏极电流的过调,从而增加开关损耗,加速器件老化。并且也会导致短路时峰值电流的增加,加剧短路工况。

另外,对于多并联的情况,由于Vth迟滞引起的不规则Vth减小将影响动态均流,从而降低器件的可靠性和使用寿命。虽然是可以恢复的,但对于开关速度更快的碳化硅而言,对于动态特性的影响还是不容忽视的,实际中合理的选取Vg,off和设计驱动参数显得尤为重要。

2. 短路的鲁棒性

对于碳化硅MOSFET而言,另一个讨论较多的便是短路耐受时间(SCWT)。传统的硅基IGBT的耐受时间在10us左右,而碳化硅只有几个微秒(如2~4us),具体数值跟每家供应商的设计相关。

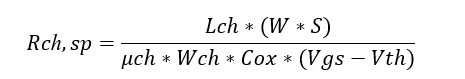

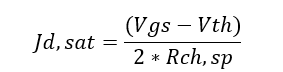

碳化硅的比沟道电阻我们可以用以下式子[3]表示,

其中,Lch和Wch为沟道长度和宽度,μch为沟道迁移率,Cox为氧化层比电容,Vgs为驱动电压,Vth为阈值电压,W和S为MOSFET元胞宽度和间距。

可以看出,增加电子迁移率和优化结构可以达到降低沟道电阻的目的,但任何减小沟道电阻的措施都会相应地导致饱和电流密度的成比例增大,饱和电流密度可以表示为,

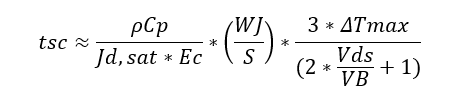

从而影响到短路耐受时间tsc。短路耐受时间tsc我们可以表达为,

其中, 是材料密度,Cp为比热,Jd,sat为饱和电流密度,Ec为临界电场,WJ为JFET区的宽度,S为单元间距,ΔTmax为最大可接受温升,Vds为施加的漏源极电压,VB为器件耐压。

是材料密度,Cp为比热,Jd,sat为饱和电流密度,Ec为临界电场,WJ为JFET区的宽度,S为单元间距,ΔTmax为最大可接受温升,Vds为施加的漏源极电压,VB为器件耐压。

可以看出,短路耐受时间与临界电场成反比,所以碳化硅往往比类似等级的硅器件所能承受的短路电流短,而降低沟道电阻或进一步缩短短路耐受时间,需要进行权衡。较短的短路耐受时间对于实际应用中驱动电路设计提出了更高的要求,同时能否在较短的短路时间内保护住也成为碳化硅可靠性的一个重要话题。

3. 封装

半导体芯片、铜和陶瓷材料之间的热膨胀系数(CTE)在高温下的巨大变化会引起显著的热应力,限制着器件最高工作温度和寿命,同时由于绑定线引入的杂散电感,影响着电路的稳定性。随着碳化硅种种优异的性能,传统基于硅基的封装技术已无法很好地适应其高速发展的步伐。

基于碳化硅的高临界电场和低本征载流子浓度,碳化硅芯片工作在超过200℃的高温下,同时碳化硅的芯片尺寸更小带来了更大的热应力集中,传统封装的热应力几乎不能满足,需要引进新的封装技术,提高热机械可靠性。目前我们可以尝试采用不同材料的DCB或者AMB来提高碳化硅模块的性能,如AlN,Si3N4等。

同时,碳化硅更高的开关速度,对于杂散电感更为敏感,因此要求封装中更低的杂散电感,需要引入新的芯片互连技术。如更改绑定线的材料,如铜绑定线,或者铜带绑定;又如Semikron Danfoss推出的汽车级碳化硅模块eMPack,采用柔性薄膜进行芯片间的互联。

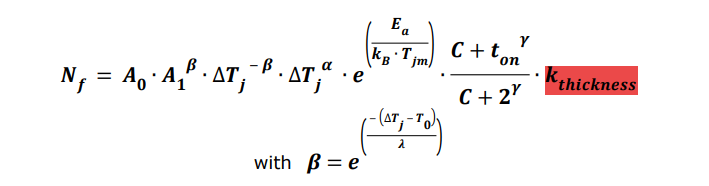

另外,Semikron Danfoss在功率循环AN 21-001的寿命模型中提到了根据芯片厚度等引入的修正因子kthickness

对于耐压小于1200V的IGBT此因子为1,对于1700V的IGBT为0.65,而由于碳化硅材料的杨氏模量(弹性模量)约为硅的3倍,考虑到这个因素,对于耐压小于1200V的SiC此因子只有0.33。

所以,要想充分发挥碳化硅的性能,提高其可靠性和寿命,先进的封装技术是必不可少的,这也是目前大力发展的方向之一。

总结

碳化硅以其高临界电场和高热导率等优势给已经接近物理极限的硅半导体带来了延续,推动着电力电子系统的发展,但碳化硅并不像硅那样,经过多年的发展和多年的市场应用,技术和成本都已经相当成熟。虽然碳化硅有着相当优异的物理特性和电学特性,但是生产工艺的成熟度还没有达到和传统硅一样,就像上述栅极氧化层可靠性,短路鲁棒性以及封装等等依旧限制着碳化硅器件的可靠性和寿命。

相信随着碳化硅生产工艺和外部配套的不断发展,其可靠性和寿命将得到不断地提升。

参考文献:

[1]‘Review of wide band-gap technology: power device, gate driver, and converterdesign’, Krishna Ravinchandra, 2022

[2] ‘Roleof Threshold Voltage Shift in Highly Accelerated Power Cycling Test for SiCMOSFET Modules’, Haoze Luo, 2020

[3] ‘Demonstrationof constant-gate-charge scaling to increase the robustness of silicon carbidepower MOSFETs’, James A. Cooper, 2021

[4] ‘RecentReview on Failure in Silicon Carbide Power MOSFETs’, Divine Khan Ngwashi, 2021

[5]Application Note AN 21-001, ‘Power cycle model for IGBT product lines’, ArendtWintrich, 2021

编辑:黄飞

-

宽禁带半导体:聊聊碳化硅(全是干货!)#电路知识 #电工 #电工知识微碧半导体VBsemi 2024-01-17

-

碳化硅二极管选型表2019-10-24 1907

-

碳化硅半导体器件有哪些?2020-06-28 4434

-

碳化硅基板——三代半导体的领军者2021-01-12 4439

-

被称为第三代半导体材料的碳化硅有着哪些特点2023-02-20 3293

-

碳化硅肖特基二极管的基本特征分析2023-02-28 2650

-

宽禁带半导体SiC功率器件有什么样的发展现状和展望说明2021-02-01 2045

-

宽禁带半导体发展迅猛 碳化硅MOSFET未来可期2022-07-06 1890

-

对话|成本下降对宽禁带半导体应用多重要?2022-10-28 2153

-

什么是宽禁带半导体?2023-05-06 7704

-

宽禁带半导体的核心材料碳化硅衬底到底贵在哪里?2023-10-09 2196

-

第三代宽禁带半导体:碳化硅和氮化镓介绍2024-12-05 3728

-

安森美在碳化硅半导体生产中的优势2025-01-07 1125

全部0条评论

快来发表一下你的评论吧 !