应用笔记|如何使用 STM32U575/585 微控制器的 GPDMA

描述

目录预览

1.前言

2.GPDMA 通用指南

3.外设、存储器和 GPDMA 配置

4.系统性能

1.概述

本应用笔记适用于 STM32U575/585 微控制器,这些微控制器是基于 Arm Cortex核心的器件。

提示: Arm 是 Arm Limited(或其子公司)在美国和/或其他地区的注册商标。

参考文档:

• 参考手册基于 Arm的 STM32U575/585 32 位 MCU(RM0456)

• STM32U585xx 数据手册(DS13086)

• STM32U575xx 数据手册(DS13737)

2.GPDMA 通用指南

2.1GPDMA 概述

在减载 CPU 的控制下,GPDMA 控制器通过链表执行存储器映射外设和/或存储器之间的可编程数据传输。

GPDMA 是双端口 AHB 主设备和系统外设。大多数外设和存储器都与之建立连接。在需要数据传输时,这一点提 供了很大的灵活性并提高了系统性能。链表是存储器中程序化的数据结构,旨在让每个 GPDMA 通道为链接和安排 DMA 数据传输做好准备。GPDMA 有 16 个通道。

2.2 GPDMA 通道分配

用户必须分配一个通道用于 GPDMA 传输。为了能够同时处理来自源的 GPDMA 传输(读访问)和到达目标的GPDMA 传输(写访问),GPDMA 对给定 GPDMA 通道使用专用 FIFO。FIFO 单元的单位是一个字节。

FIFO 的大小决定了通道能够有效处理的最大 DMA 突发大小(突发长度与数据宽度的乘积)。注意,通常突发越大,系统总体性能越好:更高吞吐率/带宽传输,更低系统总线占用率。

鉴于系统总线为 32 位字宽,建议将 DMA 源/目标数据宽度设定为 32 位(GPDMA_CxTR1 中的 S/DDW_LOG2[1:0]),以便最大限度减少总线使用量。

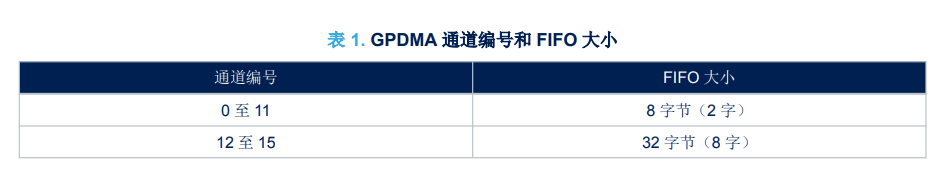

如下表所示,有两类通道,分别具有不同的 FIFO 大小和寻址模式:

• 通道 0 至 11:

– FIFO 大小为 8 字节(2 字)。

– 寻址限于线性模式:固定寻址(通常用于外设寄存器访问)或连续数据增量寻址(通常用于存储器访问)。

• 通道 12 至 15:

– FIFO 大小为 32 字节(8 字)。

– 支持线性和二维寻址模式:二者均适用于源和目标,可设定两个地址跳转/偏移量:

◦ 每个编程突发后

◦ 每个编程块后

建议将通道 0 至 11 分配用于从 AHB/APB 外设到 SRAM 的传输或从 SRAM 到 AHB/APB 外设的传输,除非存储器需要二维寻址或外设是支持突发请求的 AHB 外设。

然后,建议将突发设定为 1 字(FIFO 大小的一半),除非应用需要处理 8 或 16 位数据宽度。建议将通道 12 至 15 分配用于存储器之间的传输。然后,出于性能方面的考虑,建议将突发设定为默认的 4 字(FIFO 大小的一半)。

同样地,将通道 12 至 15 优先用于始于支持突发请求的 AHB 外设,比如 OCTOSPI、HASH 和 ADC。然后,通常将始于/止于外设的半传输设定为突发。建议将始于/止于存储器的(半)传输设定为 4 字突发。

对于具有更高带宽要求的 AHB 外设的始于/止于一些外设的传输,同样优先选择通道 12 至 15。建议将始于/止于存储器的(半)传输也设定为 4 字突发。

2.3 GPDMA 端口选择

用户必须为始于源(GPDMA_CxTR1 中的 SAP)的传输分配一个端口,并且为止于目标(GPDMA_CxTR1 中的 DAP)的传输分配一个端口。在执行下一次数据传输之前,会通过下一个链表项和数据结构动态更新此分配。

关于 GPDMA 的总线拓扑可总结如下(参见第 4 节 了解更多信息):

• GPDMA 端口 0 直接连接到 APB1 和 APB2 外设,不穿过 AHB 矩阵(参见图 2 和图 4)。

• AHB 矩阵的默认从设备(参见图 2 和第 4.3.2 节 )为:

– GPDMA 端口 0 的 AHB1 外设(MDF、FMAC 和 CORDIC)

– GPDMA 端口 1 的 SRAM1

建议按照以下方式使用 GPDMA 的两个主设备端口:

• 将端口 0 分配用于始于/止于外设的(半)传输,无论是 AHB 还是 APB 外设。将端口 1 分配用于其他(半) 传输(分别止于/始于存储器)。对于 APB1 和 APB2 外设,端口 0 避免穿过互连矩阵,减少了相应通道上的 总体延迟。这也减少了互连总线矩阵包含的和之后的 AHB 总线活动。

• 端口 1 被分配用于存储器至存储器的传输(特别是访问 SRAM1 时,但不仅限于此)。对外设使用端口 0 并 对任何存储器使用端口 1 的优势在于:

– 外设至存储器和存储器至外设的传输过程中两个端口上的带宽平衡

– 避免至存储器的突发直接影响外设访问的延迟

这是针对性能的典型和推荐配置。当然,用户可以自由地选择任何可以访问源位置的端口,以及任何可以访问目标 位置的端口。

当通道未激活时,GPDMA 为加载下一个链表项而分配的链接端口由用户在通道层面进行定义(GPDMA_CxCR 中 的 LAP)。下一个链接列表项已准备就绪并存储在内存中。然后,建议将端口 1 分配用于加载下一个链表项。

本文档以 GPDMA 和可能受到 GPDMA 协助的外设的组合功能为基础,为系统开发人员提供一些以性能为导向的编程指南

-

应用笔记 | STM32U575/585 MCU 硬件开发入门2023-09-28 5295

-

STM32U575/585 MCU硬件开发入门2023-09-06 679

-

STM32U575/585微控制器中嵌入的通用DMA(GPDMA)相关2023-08-01 674

-

如何在STM32U5系列微控制器中使用GPDMA2022-12-02 589

-

如何使用STM32U575/585微控制器存储器和外设2022-11-24 737

-

如何将 GPDMA 用于 STM32U575/585 微控制器2022-11-21 653

-

应用笔记|STM32U575/585 MCU 硬件开发入门2022-11-16 4785

-

STM32U575/585微控制器的超低功耗特点2022-07-29 3615

全部0条评论

快来发表一下你的评论吧 !