如何快速实现系统上下电时间

描述

前言

电路设计中,满足MCU的上电时序,是系统设计最基本最重要的要求之一,因此设计中我们会格外关注系统电源的上下电时间,如果上下电时间过长,可能会导致MCU启动失败或系统运行逻辑混乱,因此缩短MCU电源的上电和放电时间就显得尤为重要。

如何加快系统上电时间?

以LDO或Buck类电源为例,之前项目中遇到一个问题,因为使能引脚EN输入电压范围跟输入引脚VIN一样,因此设计时直接将使能引脚接电源,后面板子回来做硬件测试时发现电源上电期间有抖动现象,且上电时间比较长。

后来通过分压电阻将使能引脚用起来,上电抖动消失,并且上电时间明显减小。那么,为什么会有这种情况?

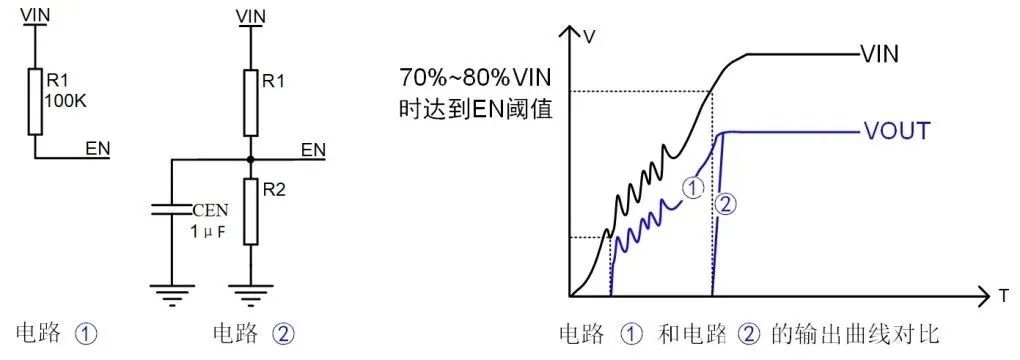

原因:使能引脚通过外部上拉来默认使能,会过早地让电源芯片达到使能阈值,输出就会跟随输入,即输入有多慢输出就有多慢,且上电时输入端的抖动也会传送给输出,并且这种接法在输入电压不高的情况下打开芯片可能会导致芯片输出又跌落的情况发生。如下图1所示为设置EN直接上拉和采用分压电路时的输出曲线示意图。

图1 EN上拉至输入和采用分压电路时的输出曲线

曲线①,使能上拉至输入,此时输出上升时间长且会受到输入波动的影响;

曲线②,合理采用分压电阻,当VIN上升到70%~80%的时候,再使EN的电压到达使能阈值,此时输出上升边沿陡峭,输出平稳,摒除了输入电源的不稳定阶段,减小了输入电压波动的影响。同时预留了20%~30%的余量,避免电源波动导致输出关闭。此时的上电对于MCU来说才是干净利落的!

如何快速使系统下电?

系统快速下电的必要性:

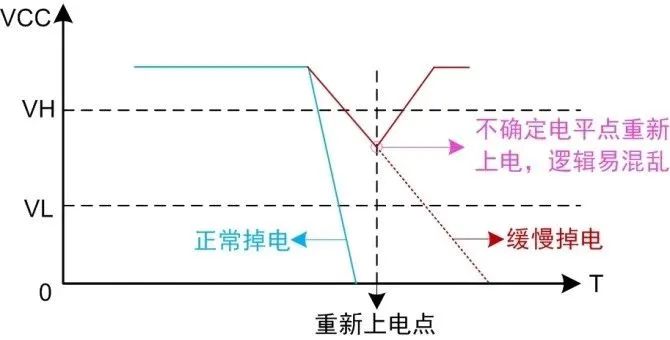

系统在做快速上下电测试时,经常会遇到由于下电缓慢,导致系统下电不完全导致的重新开机逻辑混乱问题。如下图2所示:

图 2 掉电缓慢示意图

如上图2所示,当电源掉电,负载不能及时泄放能量时,就会出现MCU等数字器件掉电缓慢的情况。若此时重新上电,由于芯片内部无法及时“归零”,对MCU等数字器件来说,这是一种不确定的状态,此时再对系统进行重新上电的操作,就容易造成MCU逻辑混乱,系统不能启动的情况。

因此电源关闭后使MCU的电源快速下降至近0V,使系统在短时间内到达一种确定的状态,也是快速重新上电时系统能正常启动的关键因素。

哪些方法:

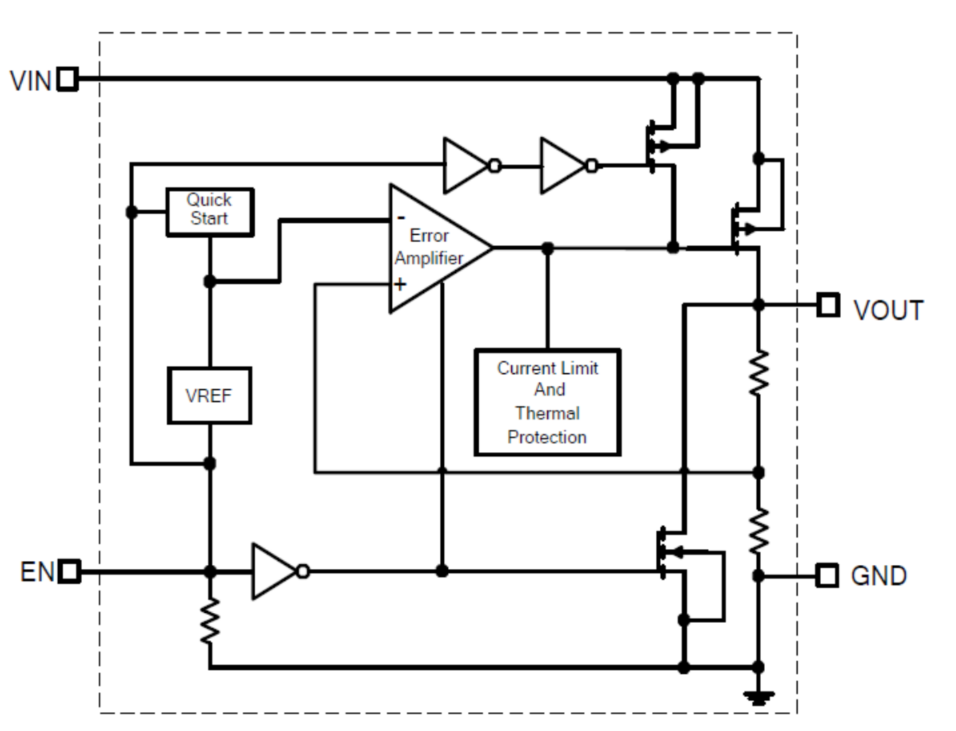

以LDO为例,有的LDO芯片内部是带有快速泄放电路的,如下图3规格书中描述。这是一款带有快速放电功能的电源芯片。其内部功能框图如下图4所示,基本原理是使能引脚EN拉低后,通过反相器变为高电平到达内部NMOS,此时NMOS的Vgs>0,因此导通将输出VOUT拉低到GND泄放能量。

图3

图4

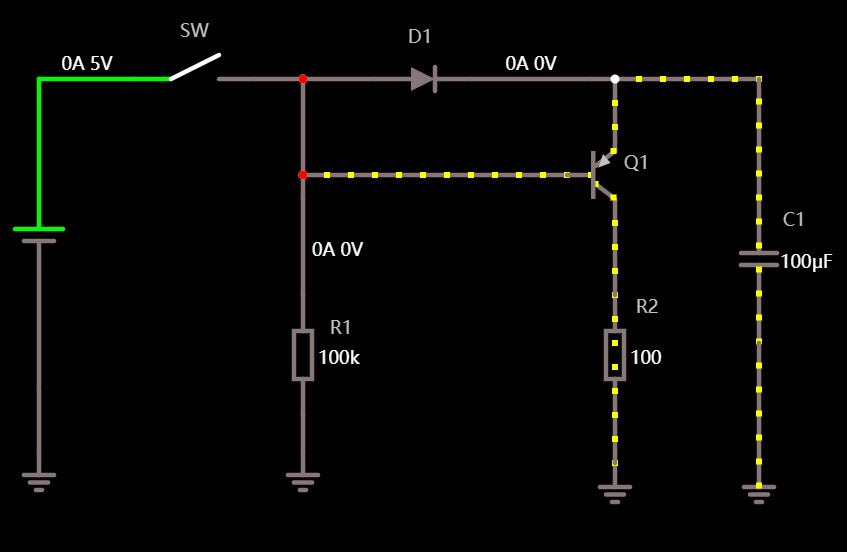

搭建分立电路做快速泄放电路,很多人分享过,这里大概讲下原理,电路原理图如下图5所示。

开关SW闭合时:

5V电源通过二极管D1成为电压4.7V-Out。因为二极管D1是一个肖特基二极管,其正向压降比较小,约为0.3V。

此时三极管Q1的b极电压为5V,e极电压为4.7V,Q1不导通

开关SW断开时:

三极管Q1的e极电压从4.7V开始下降,b极电压从4V开始下降,Vbe = -0.7V,将Q1打开,大电容C1的电压4.7V-Out通过三极管Q1、电阻R2快速泄放到地。

图 5 电路原理图

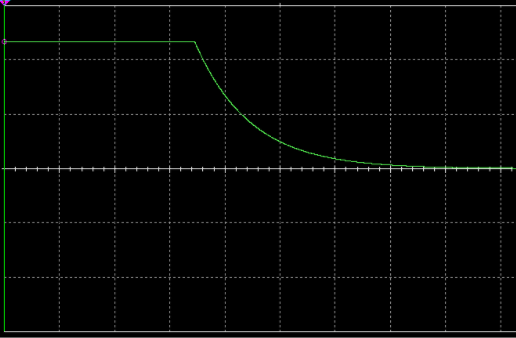

仿真波形图如下:可以看出加了泄放电路的下电波形明显要快于未添加的。

图 6 未添加泄放电路的仿真图

图 7 添加泄放电路的仿真图

审核编辑:郭婷

-

HarmonyOS实战:快速实现一个上下滚动的广告控件2025-06-24 654

-

UCD9090器件是否有上下电时间间隔要求?2024-12-13 285

-

你了解GD32 MCU上下电要求吗2024-02-02 2151

-

远程透传网关-单网口快速实现台达 PLC-ISPSoft程序远程上下载2024-01-22 2385

-

PLC远程上下载程序如何实现?plc远程维护方案2024-01-19 4422

-

为什么要测试芯片上下电功能?芯片上电和下电功能测试的重要性2023-11-10 3205

-

如何解决电源上下电瞬间波形震荡问题?2023-10-25 3348

-

如何解决MCU上下电问题?2023-08-04 2643

-

汽车电子整车上下电管理系统设计2023-07-25 916

-

ESP32如何获取系统上电时间?2023-02-17 879

-

系统快速下电的方法2022-08-26 4871

-

LDO应用:如何解决MCU上下电问题?2022-02-09 698

-

电源模块的上下电时序说明2020-12-10 1802

-

基于时间上下文的跟踪检测方法2017-12-19 856

全部0条评论

快来发表一下你的评论吧 !