设计具有复杂功能的ATE测试仪解决方案

描述

本应用笔记通过描述引脚电子(PE)器件的主要模块和不同的测试器架构,为理解和设计具有复杂功能的ATE测试仪提供了解决方案。

介绍

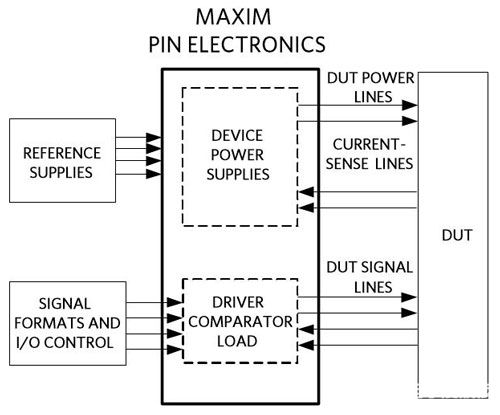

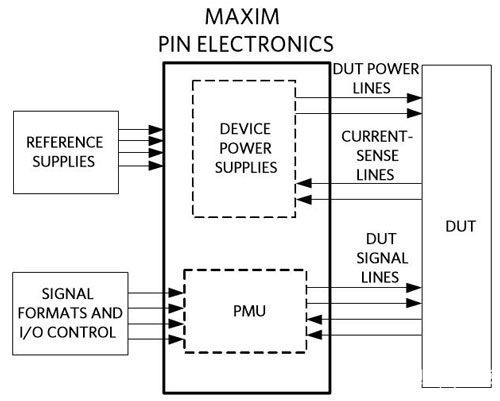

自动测试设备 (ATE) 是一种测试设备,旨在一次在一个或多个设备上执行单个测试或一系列测试。不同类型的ATE测试仪包括电子、硬件和半导体器件的测试,这些测试由Maxim的ATE高度集成引脚电子(PE)器件产品组合提供支持。这些 PE 器件能够以精确的电压和电流提供信号和电源。它还可以测量被测器件 (DUT) 的电气特性。本应用笔记描述了复杂PE器件的主要模块,并描述了不同的测试器架构,从而简化了ATE测试仪的设计。

PE 器件的主要模块包括驱动器、比较器、负载、参数测量单元 (PMU) 和器件电源 (DPS)。定时器件、数模转换器(DAC)、模数转换器(ADC)、多路复用器、继电器和开关是测试仪中上述主要模块的支持模块。Maxim广泛的产品组合支持主要的PE模块和支撑模块。以下部分详细介绍了 PE 设备的主要模块。

驱动器 + 比较器 + 负载 (DCL)

DCL驱动的信号通过结合可配置的负载条件,在各种电压电平和频率上检查DUT功能。传统上,设备的交流特性是用测试仪的DCL模块测试的。

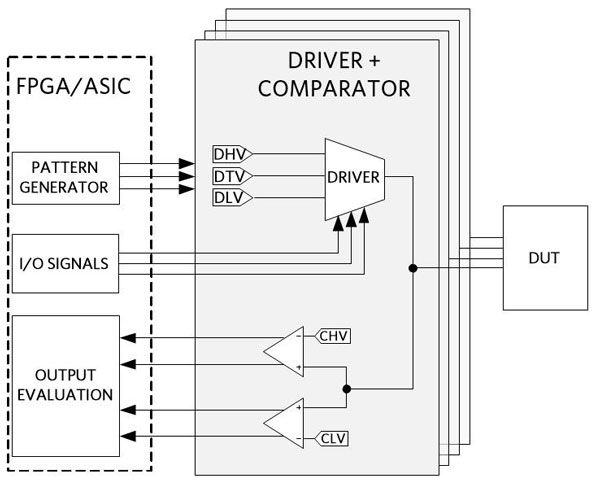

图1.使用 DCL 的测试仪框图。

测试仪速度和功耗是ATE产品的关键参数。Maxim的PE驱动器可以在不影响信号保真度的情况下高速工作,即使在较高频率下也能提供低功耗。这是通过在先进的BiCMOS半导体制造工艺中实现PE设计来实现的。例如,MAX9979具有高速驱动器,支持1V时1.1Gbps的数据速率P-P具有1.2W/通道的低功耗。

司机

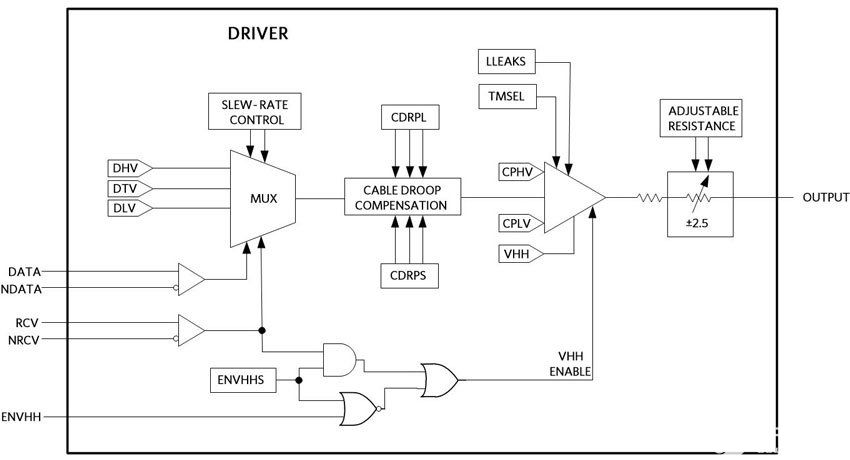

驱动器负责在不同电压电平下切换设备。任何器件中的电压电平都可以编程或通过模拟输入进行设置。具有集成电平设置DAC的PE IC支持通过串行接口对不同的电压电平进行编程。不带集成DAC的PE IC通过模拟输入设置电压电平。除驱动器模块外,还使用外部DAC、FPGA和电源来配置和提供模拟输入。峰峰值输出电压决定了PE驱动器工作的最大数据速率。该器件的最大数据速率由特定输出电压摆幅下的上升/下降时间计算得出。

三电平和四电平驱动器在当今的PE市场中占主导地位。四电平驱动器可以驱动非常高的电压(通常为 V呵呵~13V)以及三电平驱动器支持的电压电平。三电平驱动器可以在驱动高压(V卫生署)、驱动低电压 (V目录)和终止电压 (VDT),分别是模拟输入或内部 DHV、DLV 和 DTV 电平设置 DAC 的电压电平。所有内部DAC均可通过SPI接口进行配置。

驱动器的作用类似于三个或四个不同电压电平之间的多路复用器开关。多路复用器开关由高速差分输入 DATA/NDATA 和 RCV/NRCV、单端输入 ENVHHP 以及模式控制位 TMSEL 和 ENVHHS 控制。有关控制字位和数字输入,请参阅数据手册,以接通驱动器,然后在电压电平(DHV、DLV、DTV 和 V呵呵—详见表 1。

| 鞘鞘 | 环境 | 恩维赫普 | RCV | 数据 | 驱动器输出 |

| X | X | 1 | 0 | 0 | 驱车前往 DLV |

| X | X | 1 | 0 | 1 | 驱车前往 DLV |

| 0 | 0 | 1 | 1 | X | 高阻抗接收 |

| 1 | 0 | 1 | 1 | X | 驱车前往数字电视 |

| X | 1 | X | 1 | X | 驱动至 V呵呵 |

| X | 0 | 0 | X | X | 驱动至 V呵呵 |

如图2所示,驱动器的其他特性包括电缆下垂补偿、压摆率控制、驱动器电压钳位和可调输出阻抗。通常,驱动器的输出阻抗为50°C,但Maxim的ATE产品组合中的某些器件支持可调驱动器输出阻抗。在具有可调阻抗功能的驱动器中,驱动器的固定阻抗为48?和 ±2.5 的可编程阻抗?(分辨率为360m?),可通过串行接口位进行调整。这有助于克服从测试仪到DUT使用的同轴电缆的公差。压摆率电路用于调节驱动器输出电压的上升和下降时间。驱动器缓冲压摆率可通过串行接口进行控制。

图2.显示驱动程序附加功能的驱动程序框图。

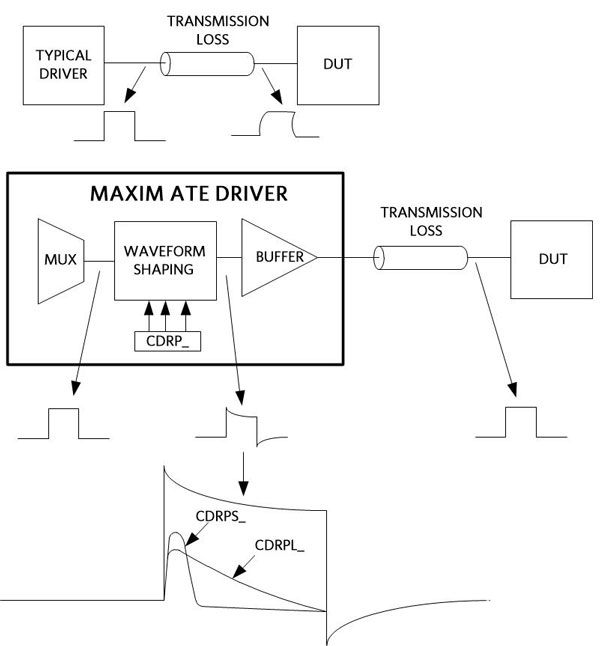

驱动器电缆压降补偿

使用有损互连器件工作会降低 DUT 的输出波形,因为传输线路中的频率相关压降,从而导致信号高度降级或无法使用。电压下降可以通过电缆下降补偿电路进行补偿。Maxim的PE驱动器补偿电路通过在标称输出波形中增加双时间常数衰减波形来抵消这种衰减。图3显示了典型驱动器与电缆下垂补偿驱动器之间的比较。要了解有关电缆性能问题的更多信息,请参考Maxim的应用笔记4338:电缆损耗解决方案。

图3.典型驱动器中的电缆下垂补偿与Maxim ATE驱动器的比较。

驱动器电压钳

当通道配置为高阻抗接收器时,高压和低压箝位限制DUT_电压并抑制反射。箝位电压可以使用模拟输入/电平设置DAC(CPHV_和CPLV_)进行设置。仅当驱动器处于高阻抗模式时,才会使能箝位。对于瞬态抑制,将箝位电压设置为超出最小和最大预期 DUT 输出电压范围的大约 0.7V。然后,过压保护保持活动状态,无需负载DUT_。驱动器箝位始终且仅在驱动器高阻抗模式下启用。

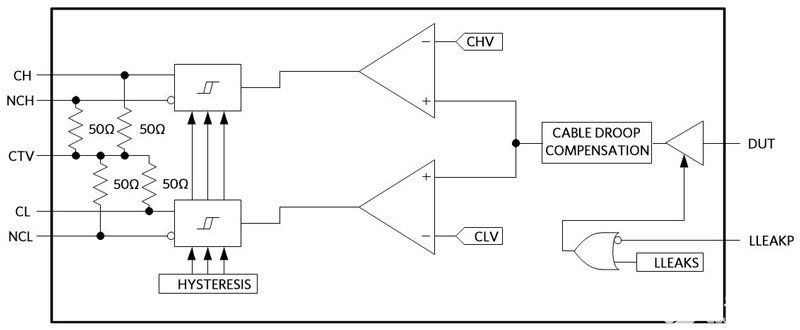

比较仪

高速比较器的一个输入在内部连接到DUT_节点,另一个输入连接到CHV或CLV(内部DAC或外部模拟输入)。比较器的输出是输入条件的逻辑结果。高速比较器可以有两种类型——窗口比较器和差分比较器。

窗口比较器

两个独立的比较器构成一个窗口比较器。窗口比较器输出CH和CL由DAC电压CHV和CLV控制,如图4所示。表2显示了窗口比较器的真值表。从真值表中,一个示例条件是当 DUT 电压在 CLV 和 CHV 电压之间的窗口内时 (V中新社< V被测器< VCHV),则CL比较器输出为高电平,CH输出为低电平。

| 条件 | CH | CL | |

| VDUT < VCHV | VDUT < VCLV | 0 | 0 |

| VDUT < VCHV | VDUT > VCLV | 0 | 1 |

| VDUT < VCHV | VDUT > VCLV | 1 | 0 |

| VDUT < VCHV | VDUT > VCLV | 1 | 1 |

图4.窗口比较器显示输出 CH 和 CL。

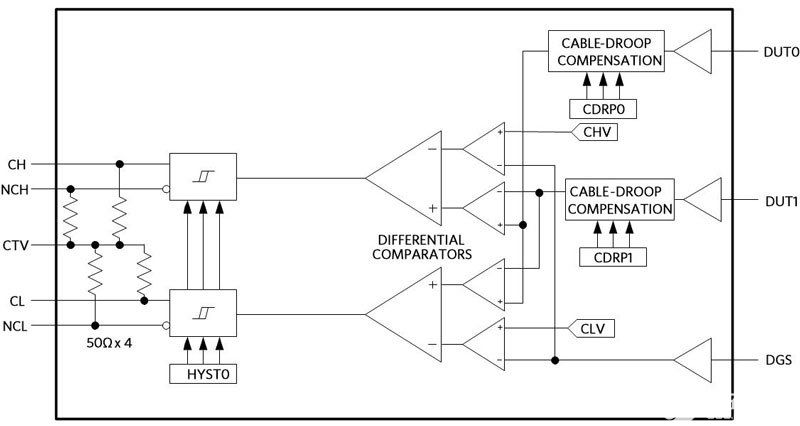

差分比较器

差分比较器比较两个DUT之间的电压电平以及DAC电压(CHV、CLV),并产生输出CH和CL。 假设比较器比较DUT0、DUT1和电平设定器CHV和CLV之间的电压电平,则图5显示了比较器的工作,其中V总局是 DUT 接地检测处的电压。表3显示了差分比较器的真值表。

| 条件 | CH | CL | |

| V被测器0- 五被测器1< VCHV- 五总局 | V被测器0- 五被测器1< V中新社- 五总局 | 0 | 0 |

| V被测器0- 五被测器1< VCHV- 五总局 | V被测器0- 五被测器1< V中新社- 五总局 | 0 | 1 |

| V被测器0- 五被测器1< VCHV- 五总局 | V被测器0- 五被测器1< V中新社- 五总局 | 1 | 0 |

| V被测器0- 五被测器1< VCHV- 五总局 | V被测器0- 五被测器1< V中新社- 五总局 | 1 | 1 |

图5.差分比较器。

负载块

在测试过程中,设备必须在加载或卸载条件下进行测试。负载模块有助于功能测试,以及验证不同负载条件下的电压和电流水平。可以控制串行接口位以启用和禁用PE IC中的负载。PE IC中有两种不同类型的负载,一种是无源负载,另一种是有源负载。

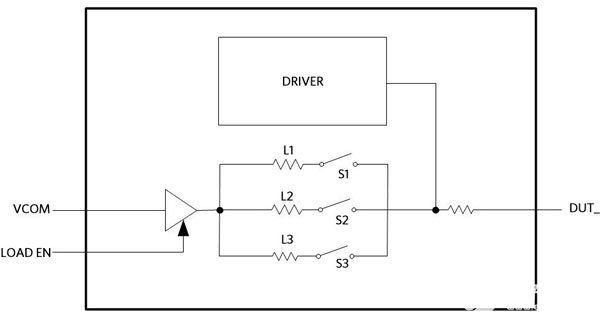

被动负载

具有无源负载的PEC具有两个或多个阻性负载选项,可通过选择开关将“换向”电压(VCOM)或在本例中为端接电平连接到DUT,如图5所示。每条路径通过通过串行接口控制的开关单独连接到 DUT。负载有助于与开漏 DUT 输出的比较器和上拉进行快速开路/短路测试。

当开关一 (S1) 启用时,负载一 (L1) 连接到 DUT。使能开关二 (S2) 时,负载二 (L2) 连接到 DUT。当 S1 和 S2 都启用时,连接到 DUT 的负载将是 L1 和 L2 并联连接。

图6.显示负载选项的被动负载。

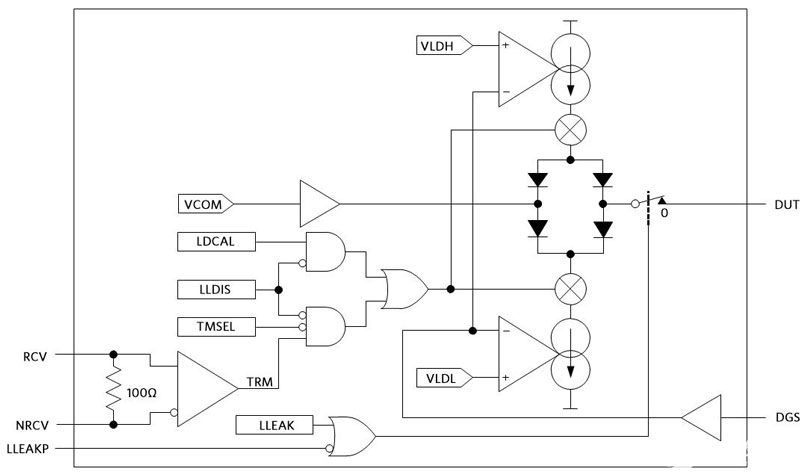

有源负载

有源负载,也称为可编程电流负载,在功能测试期间充当 DUT 的负载。有源负载是线性可编程电流源和灌电流、换向缓冲器和二极管桥,如图7所示。模拟控制输入或电平设置DAC设置灌电流/拉电流和换向缓冲器输出电压。

源电流和灌电流分别是流出和流入PE的DUT引脚的电流。当换向缓冲器输出电压电平小于 DUT 电压时,电流从 DUT 流向有源负载可编程灌电流(或 VLDL),导致被测器件源出电流。当换向缓冲器输出电压电平大于DUT电压时,电流从有源负载可编程源(或VLDH)流经二极管桥流向DUT器件,导致被测器件吸收电流。VLDH 和 VLDL DAC 电压分别用于改变源电流和灌电流的量。

图7.有源负载显示电流源和灌电流、换向缓冲器和二极管桥。

参数测量单元 (PMU)

PMU 强制并测量进入 DUT 的电流和电压。理想情况下,PMU 用于测试被测器件的直流特性。测试 系统 架构 由 可 与 一组 PE IC 共享 的 PMU 或 用于 DUT 每 个 引脚 的 PMU 组成, 称为 每 引脚 PMU (PPMU)。PPMU 架构成倍地缩短了测试时间,因为每个 DUT 引脚都可以同时进行测试。

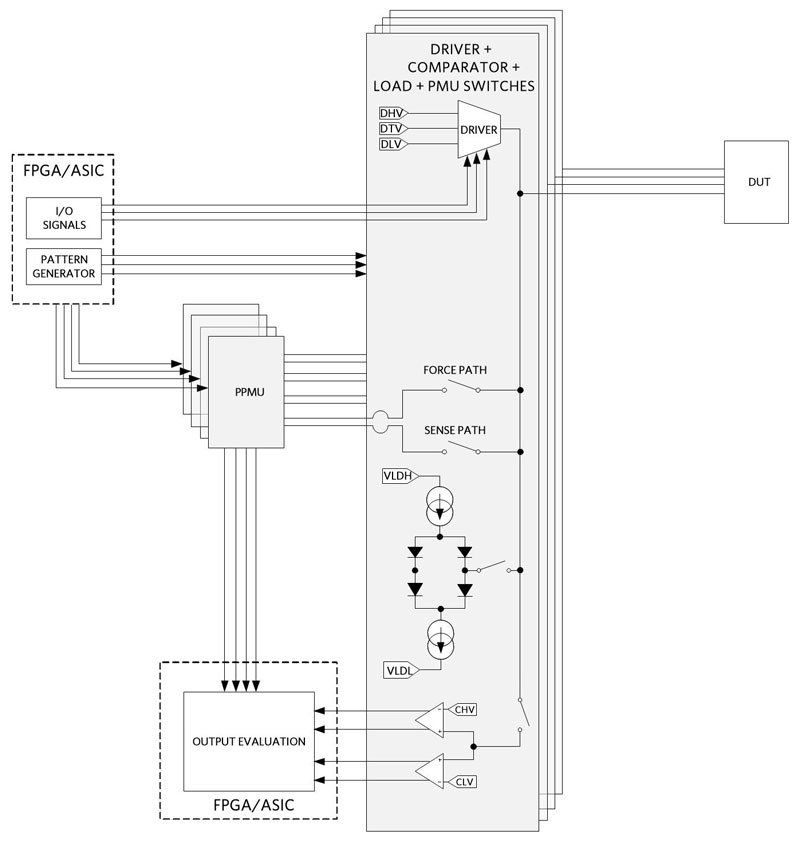

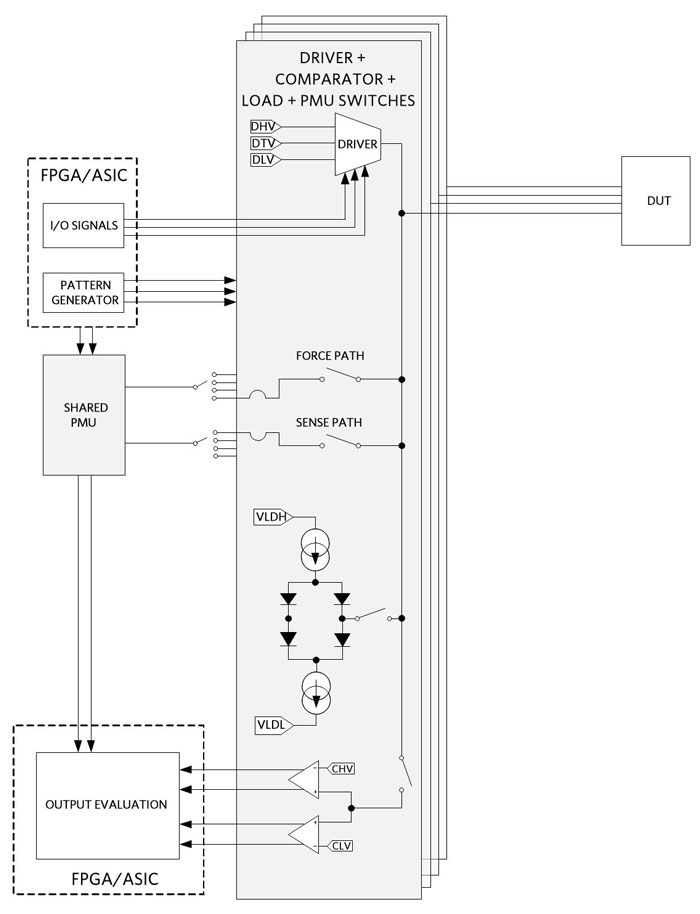

图8.使用 PMU 的测试仪框图。

PMU 具有不同的工作模式,具体取决于 PMU 输出引脚是强制电流 (FI) 还是电压 (FV),PMU 测量引脚是测量电压 (MV) 还是电流 (MI)。每个PMU都有电压钳位,以避免在FI模式下产生任何瞬态电压。它还具有电流钳位,以避免在FV模式下产生任何瞬态电流。请参考Maxim应用笔记4343,了解PMU的力电压/测量电压(FVMV)、力电压/测量电流(FVMI)、力电流/测量电压(FIMV)和力电流/测量电流(FIMI)模式。

PMU 交换机与 PMU

PMU 开关提供内部连接到 DUT 节点的力和检测路径,允许使用另一个外部 PMU 或直流电源。这些力和检测路径通过串行接口进行控制。力路径通过相对较低的电阻通过外部 PMU 或直流电源将电流/电压驱动到 DUT。检测路径提供来自 DUT 节点的更高电阻(零电流)反馈路径。

设备电源 (DPS)

测试环境中的DPS提供DUT所需的电源电压。DPS 可在力电压 (FV) 和力电流 (FI) 模式下运行。当DPS在FI模式下工作时,可编程电压钳位确保电压在DUT的范围内。当负载电流在可编程电流限值内时,工作在 FV 模式下的 DPS 充当电压源。如果达到电流限值,则DPS电压源转换为电流源/吸收。

DPS具有类似于典型电源的力和检测线,以及回读和测量电压和电流的能力。考虑一个测量电源电流(I抄送) 通过改变电源电压 (V抄送).DPS(在FV模式下工作)的力和检测线连接到器件电源引脚。力线在输出端提供所需的电压电平,检测线监视施加的电压电平。DPS 内部的补偿电路试图保持恒定的电源电压,而不管 DPS 和 DUT 之间的电阻如何。电源电流 (I抄送) 通过取决于所选电流范围的检测电阻进行测量,从而提供可调电源电压 (V抄送).PMU和DPS相似,但DPS具有比PMU更高的电流能力。

钳位和电流限制

DPS 具有电压控制输入,允许独立设置输出电压。DPS 输出具有可调节的箝位,可限制负输出电压和正输出电压和电流。DPS 的操作模式类似于 PMU 的模式。在FV模式下,输出电压与输入电压成正比,输入电压由内部寄存器设置决定。在FI模式下,输出电流与输入电压成正比,比例常数取决于DPS内部的检测电阻。

可编程电压箝位可用于限制FI模式下的输出电压。输出端的 FV 和 FI 模式下提供可编程电流限制。使能、禁用和设置电压钳位和电流限值由内部寄存器设置控制。

测试仪架构

测试仪可广泛分为片上系统 (SoC) 测试仪或内存测试仪。在 SoC 测试仪中,每个引脚都可以在不同的电压/电流水平下进行测试。在存储器测试仪中,几个驱动器用于将数据发送到DUT的存储器地址,这些地址通常是仅输入引脚;通常不需要在这些引脚上测试回读。由于这种单向通信,比较器模块更常用于SOC测试仪,而不是存储器测试仪。测试 时间 和 测试 系统 成本 是 设计 测试 系统 架构 时 的 两个 重要 考虑因素。图 9、10 和 11 描述了测试仪架构的一些示例。

图9.带有驱动器和比较器的测试仪架构。

图 10.采用 DCL 和 PPMU 的测试仪架构。

图 11.具有 DCL 和共享 PMU 的测试仪架构。

审核编辑:郭婷

-

蓝牙测试仪的作用2024-03-30 2217

-

绝缘电阻测试仪2024-12-16 661

-

信而泰网络测试仪校准解决方案2025-01-13 6213

-

回收二手网络测试仪 回收WIFI测试仪2018-06-25 1978

-

回收WT-200网络测试仪2021-07-25 850

-

具有语音功能的RCL测试仪2016-11-22 1029

-

ADI脉冲氧化测试仪解决方案2017-02-07 686

-

防雷元件测试仪是什么,它的功能都有哪些2021-03-05 2103

-

是德科技发布具有增强功能的下一代双脉冲测试仪2022-06-01 2946

-

ATE电源测试仪的适用范围介绍2022-06-09 1298

-

纳米软件带你了解ate测试及ate自动测试系统2023-11-24 2342

-

电容电感测试仪有什么特点 电容电感测试仪使用方法2023-12-20 2241

-

绝缘电阻测试仪的功能和特点2024-05-07 3169

-

多功能网络测试仪怎么用2024-05-27 3582

-

行业不同,防水测试仪咋选?2025-02-11 1089

全部0条评论

快来发表一下你的评论吧 !