经验分享——我把LDO做成了OSC

描述

01—背景

某个多功能芯片Spec要求是使用+/-5V供电,而内部部分单元需要用到一些特殊电压的供电,因此需要设计一个LDO,由于是GaAs pHEMT工艺,只有N-Channel型晶体管,再加之作者主要设计MMIC,本来也没有什么电源的理论基础,所以设计不了结构很复杂的LDO。第一版时,仅仅使用了电阻分压+源极跟随器的方式,非常简单,测试功能也是正常的。

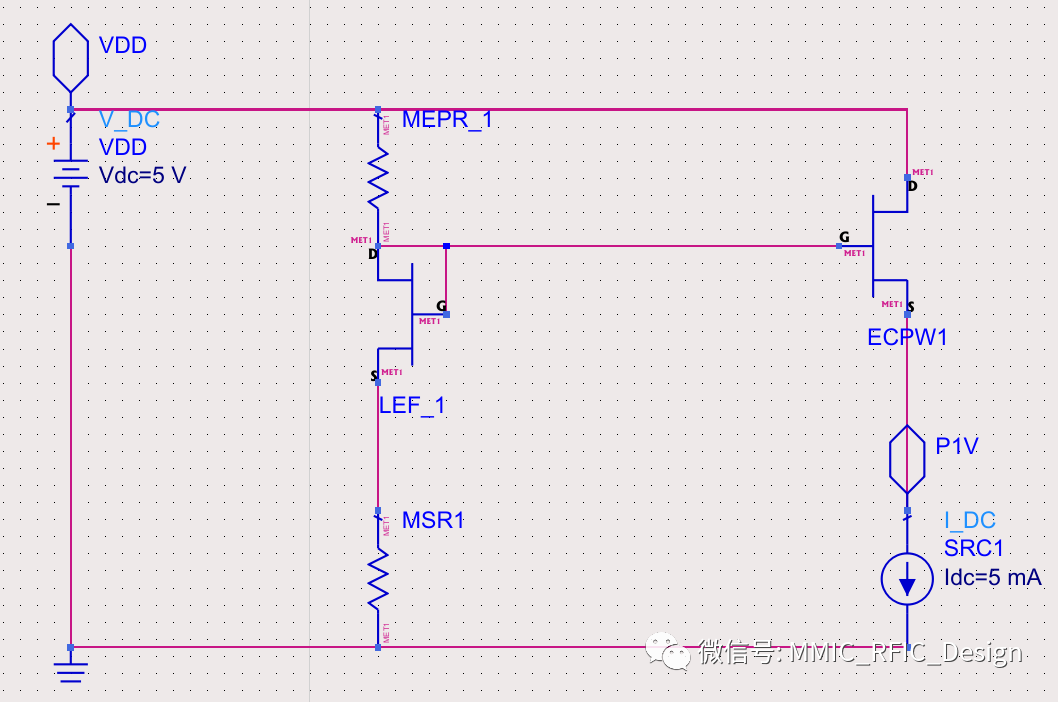

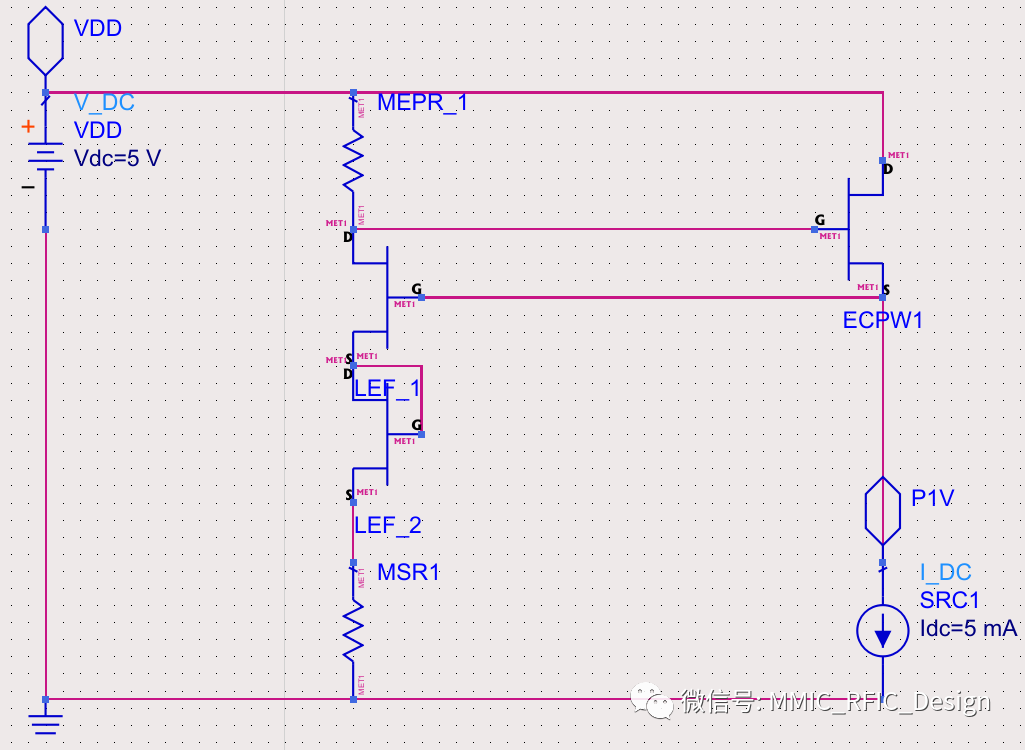

但是担心容易受高低温、工艺波动等因素影响,所以第二版时,就异想天开地改了个结构,增加了负反馈,自以为能改善电源性能:

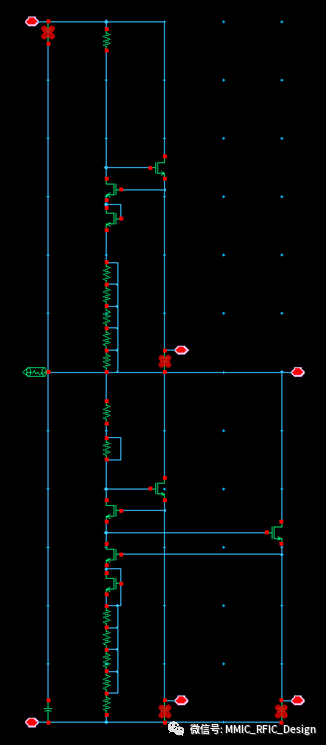

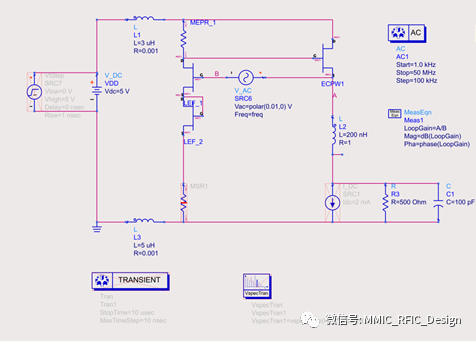

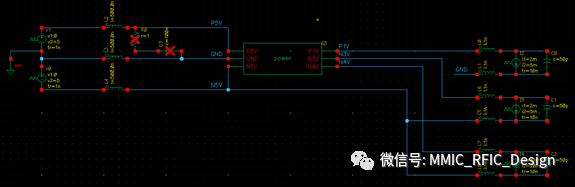

电源一共有三路,其中+5V生成了一路+1V/5mA输出,-5V生成了一路-4V/15mA和一路-3V/5mA输出。完整的原理图如下图所示,排列是从上到下依次+5V,GND,-5V,打叉的是滤波电容(实际上没有加):

02—问题

测试件单独加-5V时,电压电流都在正常范围内,单加+5V时,电流1~2mA,好像也没啥问题。如果同时加上±5V,虽然电流也在正常范围内,但如果用万用表笔测GND和-3V网络,会发现电压剧烈波动,同时-5V的供电电流也在8~18mA范围内波动。

(左)+5V/2mA(中)-5V10mA(右)无关

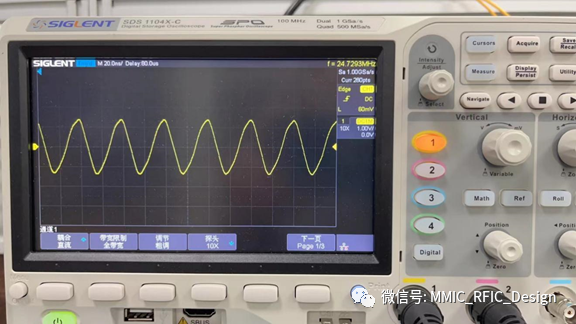

开始以为是万用表表笔引入了外界干扰,直到后来用示波器看到了+5V/GND/+1V的网络上存在明显的振荡波形!例如下图是某一次在测试件的GND上看到的波形,大概有150mVpp@24.7MHz:

经过反复测试确认,外接电源用的导线不同方式摆放或缠绕时,振荡幅度或者频率会变化,由于测试板做得很粗糙,仅仅是将所有IO PAD键合到PCB上,外围完全没有放置任何电源滤波电容,所以怀疑与此相关,于是给PCB上的±5V对地分别添加了一个10uF的电解电容,振荡消失。

03—分析

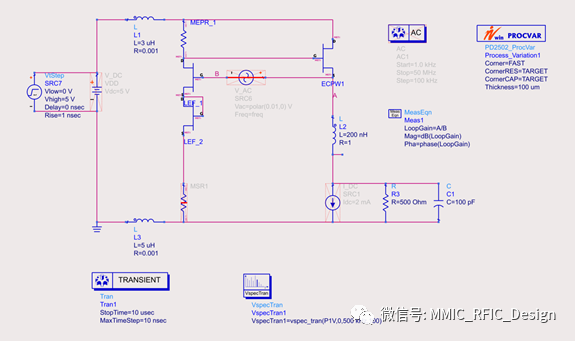

事后,开始在网上疯狂搜索LDO稳定性相关的文章,找教程学习环路稳定性相关的仿真,在ADS中使用AC仿真,在反馈路径中注入扰动信号,扫频分析得到环路的增益和相位特性,即Bode图

上图中的元件参数和下面的仿真结果都是通过仿真尝试得到的,使结果与实际情况接近。其中电感是模拟的外接电缆、PCB走线、键合线在内的寄生电感。

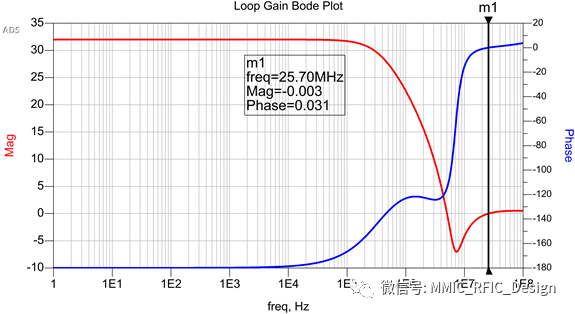

对数扫频时的Bode图如下,增益0dB、相位0(180)deg刚好在25.7MHz附近:

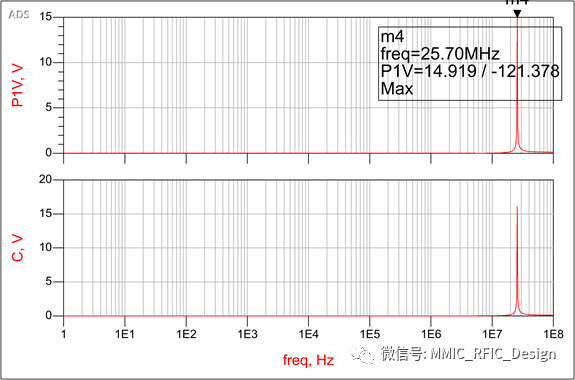

如果通过Bode图看增益和相位还不是很直观,那么下面这个输出电压随扫频信号的变化就非常明显了:25.7MHz振荡了。

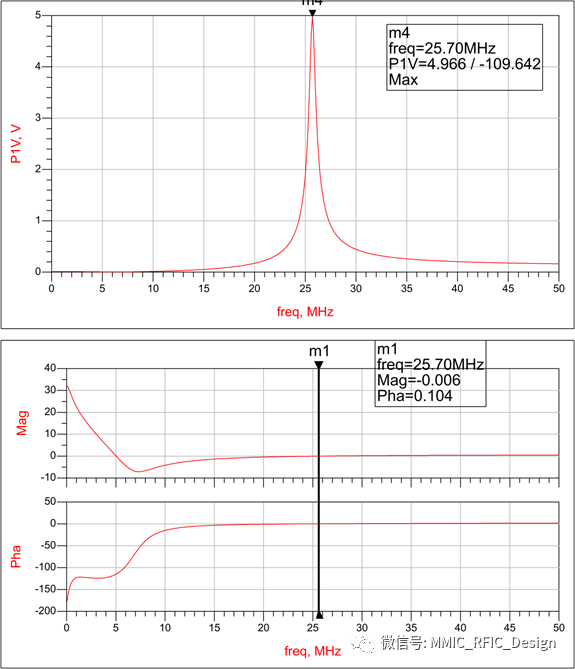

下面两张图与上面基本一致,只是将频率由对数坐标轴改为线性坐标轴,便于观察几十MHz附近的变化:

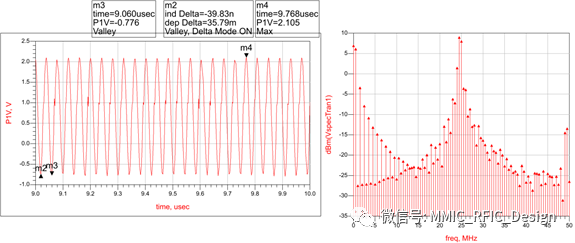

去掉环路仿真的扫频信号,直接进行Transient仿真,可以看到振荡波形及其频谱分布:

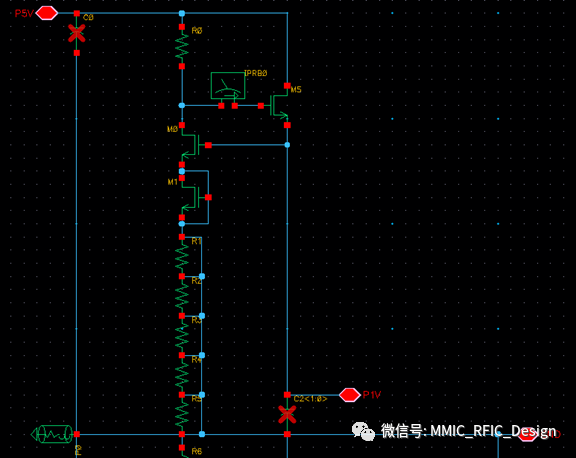

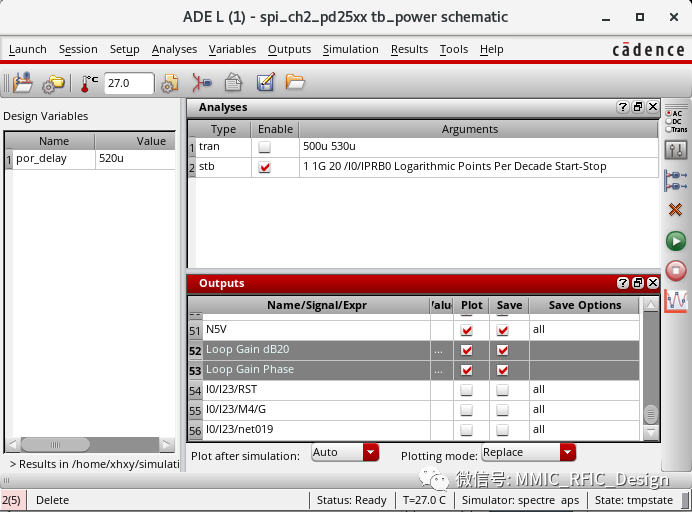

在Virtuoso环境中搭建testbench,在输出晶体管的栅极上插入了一个电流探头IPRB0:

使用ADE中的STB仿真计算环路的频率响应,它可以自动判断穿越频率、增益裕度和相位裕度。

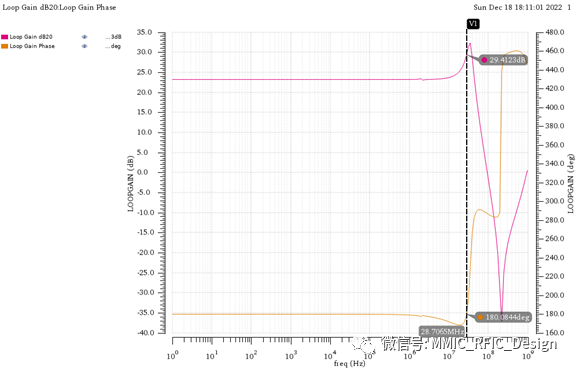

由于Virtuoso的PDK是没有仿真用的电路模型,这里的模型是我大致参考原ADS PDK的晶体管参数自定义的VerilogA模型,但是也能得到相似的仿真结果。下图是无+5V电源滤波电容时的闭环特性,显然28MHz附近发生了振荡:

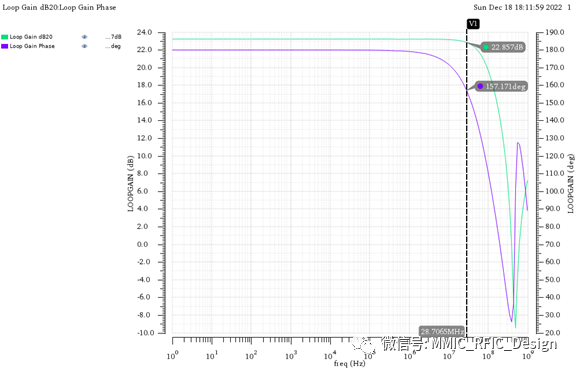

电源输入增加滤波电容后:

04—结论

结论就是吃了没有电源基础知识的亏,LDO还是有非常深的门道的,业余选手要谨慎踩坑……

这里有一个值得思考的问题就是:如果你当前的设计不完美但能工作正常,你是否会考虑一个未知的改进方案?

审核编辑:汤梓红

-

X86主板原理图设计经验分享2011-11-28 7535

-

我也成功做成了一个电子钟2013-11-07 3316

-

STM32的OSC和OSC32的差別?2014-03-28 23515

-

我从51 把程序改成了430 但是现在显示其上就是乱码?2015-05-21 3113

-

把晶体管电路设计书中电路做成板子,组队做实验,目标50人2016-03-27 4293

-

NanoPi2 如何把USB做成调试串口2016-11-23 4742

-

STM32如果不使用外部晶振的话,OSC_IN和OSC_OUT通过10K电阻接地,那OSC32_IN和OSC32_OUT也是一样的方法吗?2017-05-03 10835

-

请问怎么把logo做成封装?2019-01-16 2413

-

怎么在AD中把这个孔做成焊盘?2019-09-19 3738

-

xtal不会osc2019-10-22 2940

-

x-OSC是什么?x-OSC有哪些功能?2021-07-15 1327

-

OSC_IN和OSC_OUT的接法2022-01-26 4438

-

我的LDO怎么了?2022-11-03 377

-

Made with KiCad(141):我把流体模拟,做成了一张名片2025-09-19 1040

-

手撕AU-48语音模组:双麦降噪+消回音+USB,我把对讲机改成了“录音棚”2026-04-21 165

全部0条评论

快来发表一下你的评论吧 !