SPI至RS-485/RS-422设计解决方案的详细物理层设计注意事项

描述

作者:Richard Anslow and Dara O’Sullivan

在本文的第一部分“为工业4.0实现可靠的有线状态监控——第1部分”中,我们介绍了ADI公司的有线接口解决方案,这些解决方案可缩短客户设计周期和测试时间,并加快工业CbM解决方案的上市时间。讨论了几个方面,包括选择合适的MEMS加速度计和物理层,以及EMC性能和电源设计。此外,第 1 部分还介绍了三种设计解决方案和性能权衡。本文(第 2 部分,共 2 部分)重点介绍第 1 部分中介绍的 SPI 至 RS-485/RS-422 设计解决方案的详细物理层设计注意事项。

为MEMS实现有线物理层接口的常见挑战包括管理EMC鲁棒性和数据完整性。然而,当在长RS-485/RS-422电缆上扩展时钟同步接口(如SPI)时,以及在同一双绞线(幻象电源)上组合电源和数据时,还存在一些额外的挑战。本文讨论以下关键注意事项,并提供设计物理层接口的建议:

管理系统时间同步

数据速率与电缆长度的关系建议

共享电源和数据架构的滤波器设计和仿真

幻象电源实现的无源元件性能权衡

组件选择和系统设计窗口

实验测量

时间同步和电缆长度

设计SPI至RS-485/RS-422链路时,电缆和组件会影响系统时钟和数据同步。在长距离电缆传输中,SCLK 信号将通过电缆产生传播延迟,对于 100 m 电缆,大约为 400 ns 至 500 ns。对于 MOSI 数据传输,MOSI 和 SCLK 通过电缆同样延迟。但是,从从MISO发送到主站的数据将与SCLK不同步,其速度是电缆传播延迟的两倍。最大可能的SPI SCLK由系统传播延迟设置,其中包括电缆传播延迟以及主组件和从组件传播延迟。

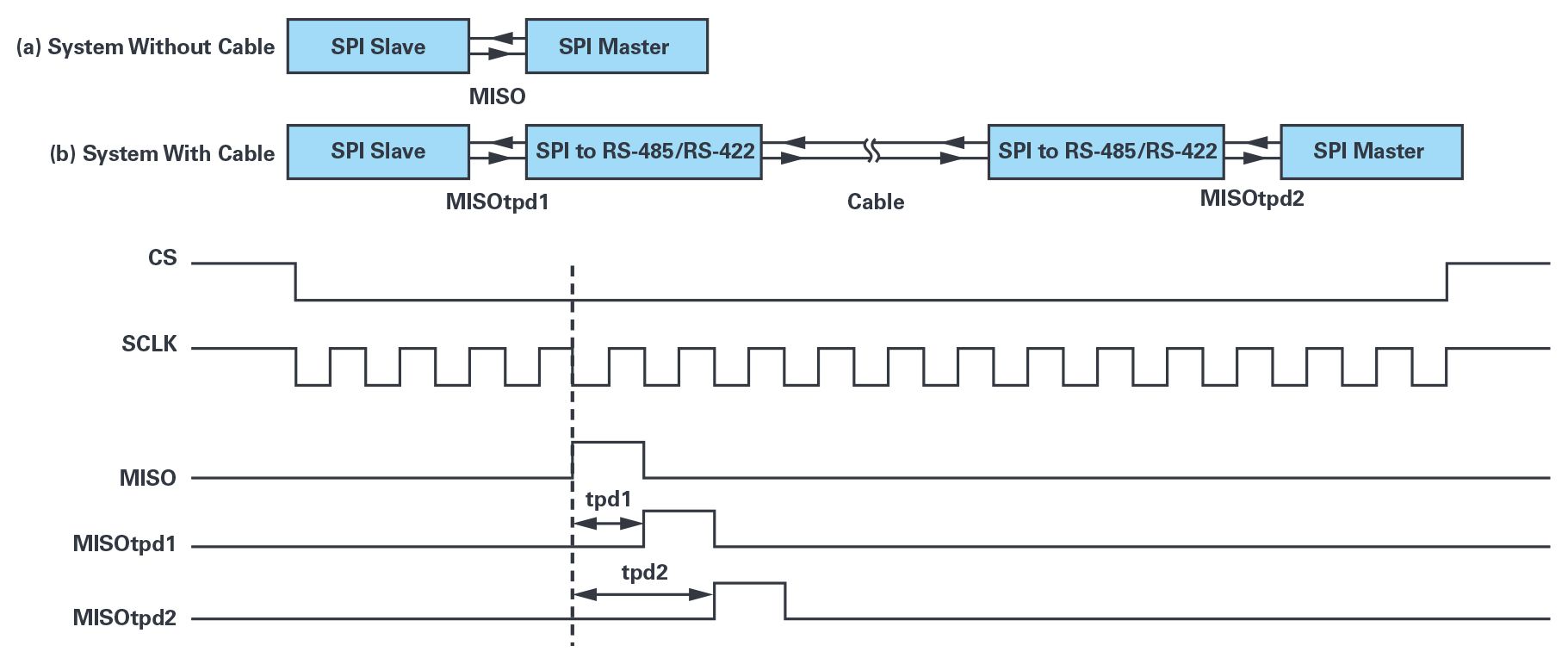

图1说明了系统传播延迟如何导致SPI主站的SPI MISO采样不准确。对于没有RS-485/RS-422电缆的系统,MISO数据和SPI SCLK将以很少或没有延迟的方式同步。对于带电缆的系统,SPI从站的MISO数据与SPI SCLK不同步,有一个系统传播延迟,如图1中的tpd1所示。MISO数据通过两个系统传播延迟(称为tpd2)不同步地返回主站。由于电缆和组件传播延迟导致数据向右移动,因此会出现不准确的数据采样。

图1.同步MISO数据和SPI SCLK,适用于带或不带长RS-485/RS-422电缆的系统。

为了防止MISO采样不准确,可以减少电缆长度,降低SPI SCLK或在主控制器中实现SPI SCLK补偿方案(时钟相移)。理论上,系统传播延迟应小于SCLK时钟周期的50%,以实现无差错通信,在实践中,系统延迟限制为40%SCLK可以作为一般规则。

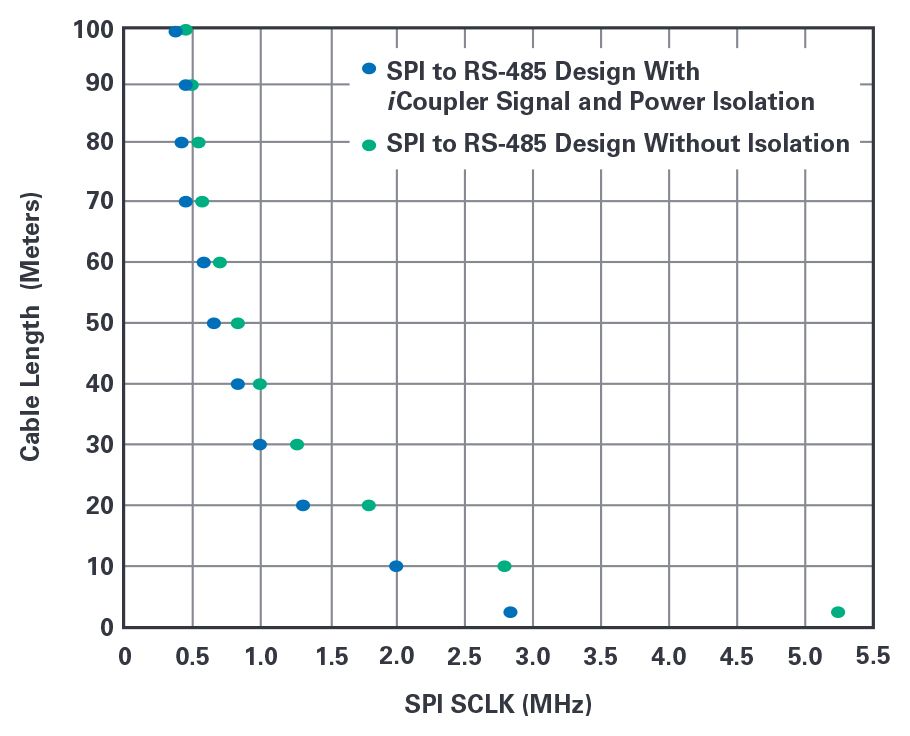

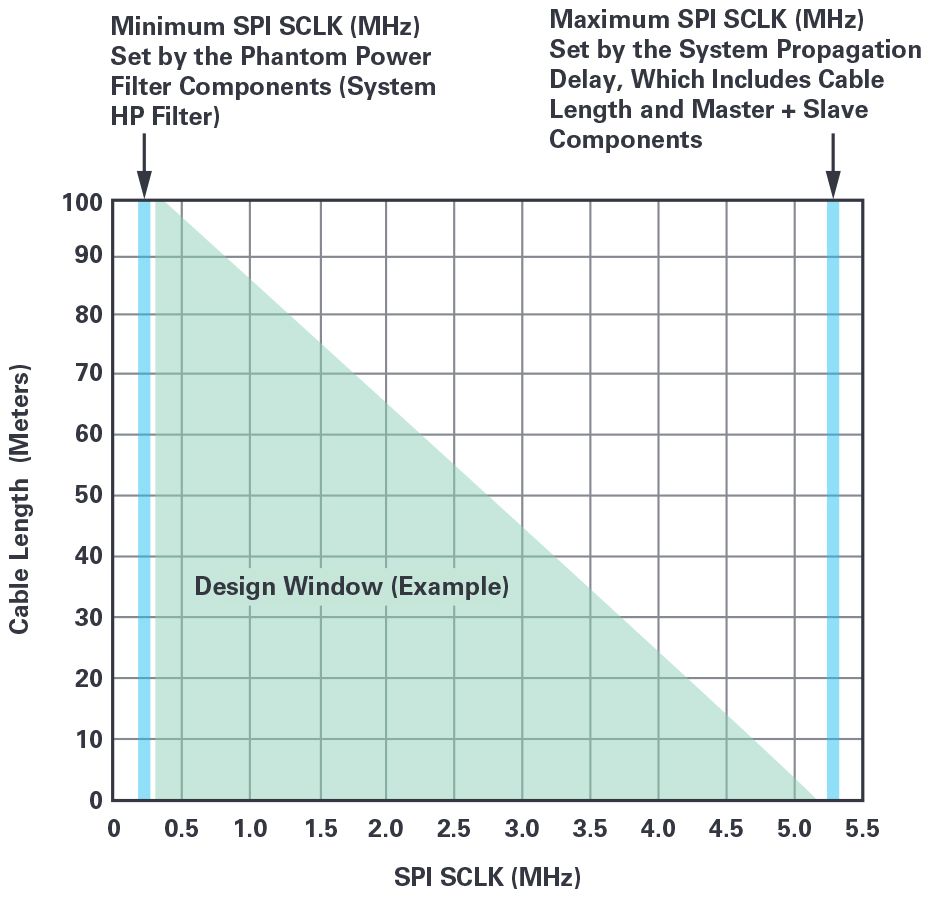

图2提供了第1部分所述的两种SPI至RS-485/RS-422设计的SPI SCLK与电缆长度的比较指南。1非隔离设计采用ADI公司的高速EMC鲁棒型小尺寸RS-485/RS-422器件(ADM3066E和ADM4168E)。隔离式设计还包括ADI公司的iCoupler信号和电源隔离型ADuM5401器件,为SPI至RS-485/RS-422链路提供额外的EMC鲁棒性和抗噪性。这种设计增加了额外的系统传播延迟,从而限制了在较高SPI SCLK速率下的操作。对于较长的电缆(大于 30 m),强烈建议增加隔离,以帮助缓解接地环路和 EMC 事件,例如静电放电 (ESD)、电气快速瞬变 (EFT) 和耦合到数据传输电缆的高压浪涌。当电缆长度扩展到30 m或更大时,隔离式和非隔离式设计的SPI SCLK与电缆长度性能相似,如图2所示。®

图2.SPI SCLK 与隔离和非隔离设计的电缆长度指南。

幻象电源

背景

幻象电源将电源和数据结合在一根双绞线上,可在主设备、从设备之间实现单电缆解决方案。将数据和电源结合在一根电缆上,可在空间受限的边缘传感器节点上实现单连接器解决方案。

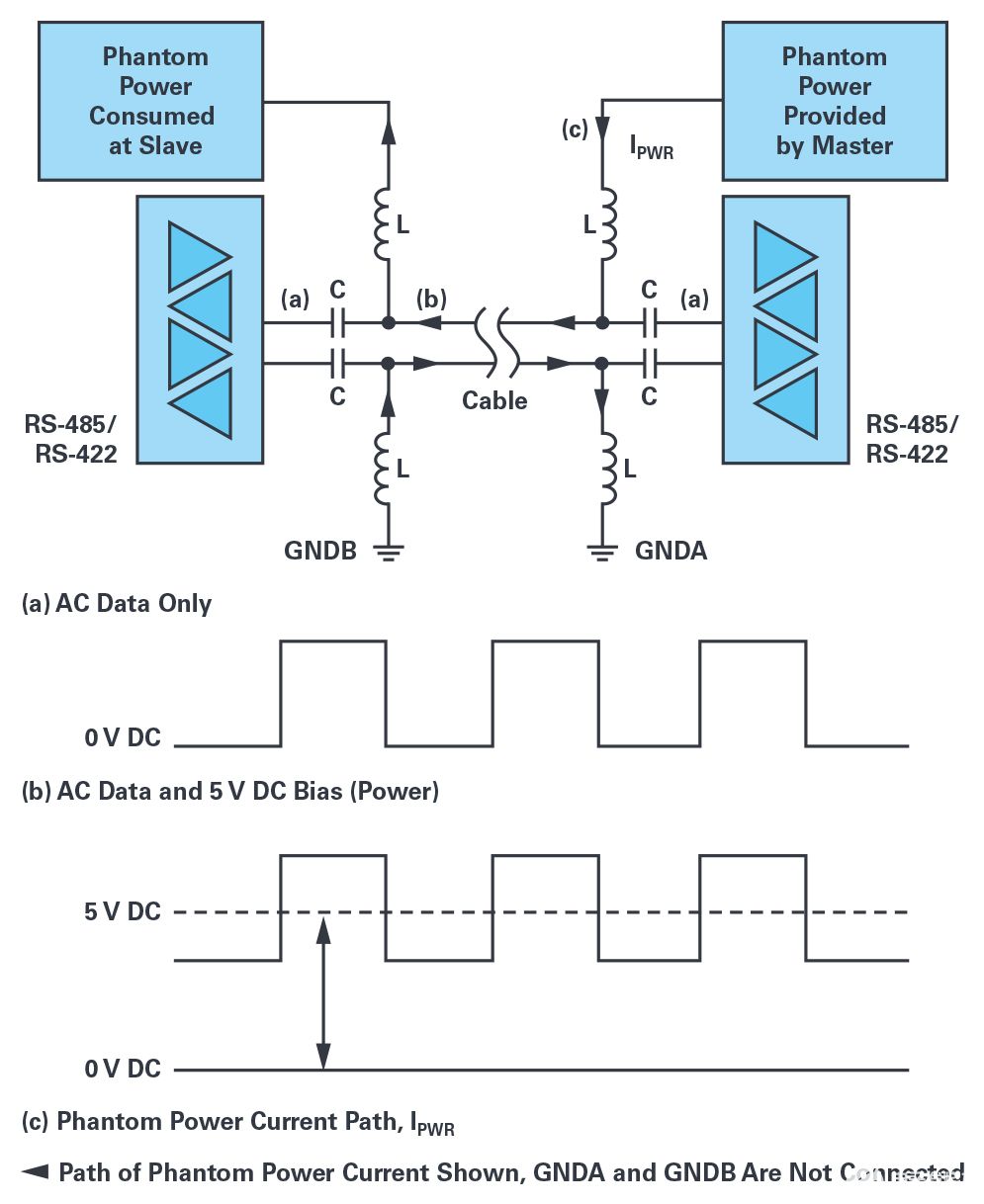

电源和数据使用电感电容网络分布在一根双绞线上,如图3所示。高频数据通过串联电容耦合到数据线,这还可以保护RS-485/RS-422收发器免受直流总线电压的影响,如图3a所示。图3显示了通过连接到数据线的电感器连接到主控制器的电源。5V直流电源偏置交流数据总线,如图3b所示。在图3c中,电流路径显示为I压水堆在主站和从站之间,使用电缆远端状态监控 (CbM) 从属传感器节点上的电感器从线路中提取功率。

图3.幻象电源物理层交流和直流电压电平。

高通滤波器

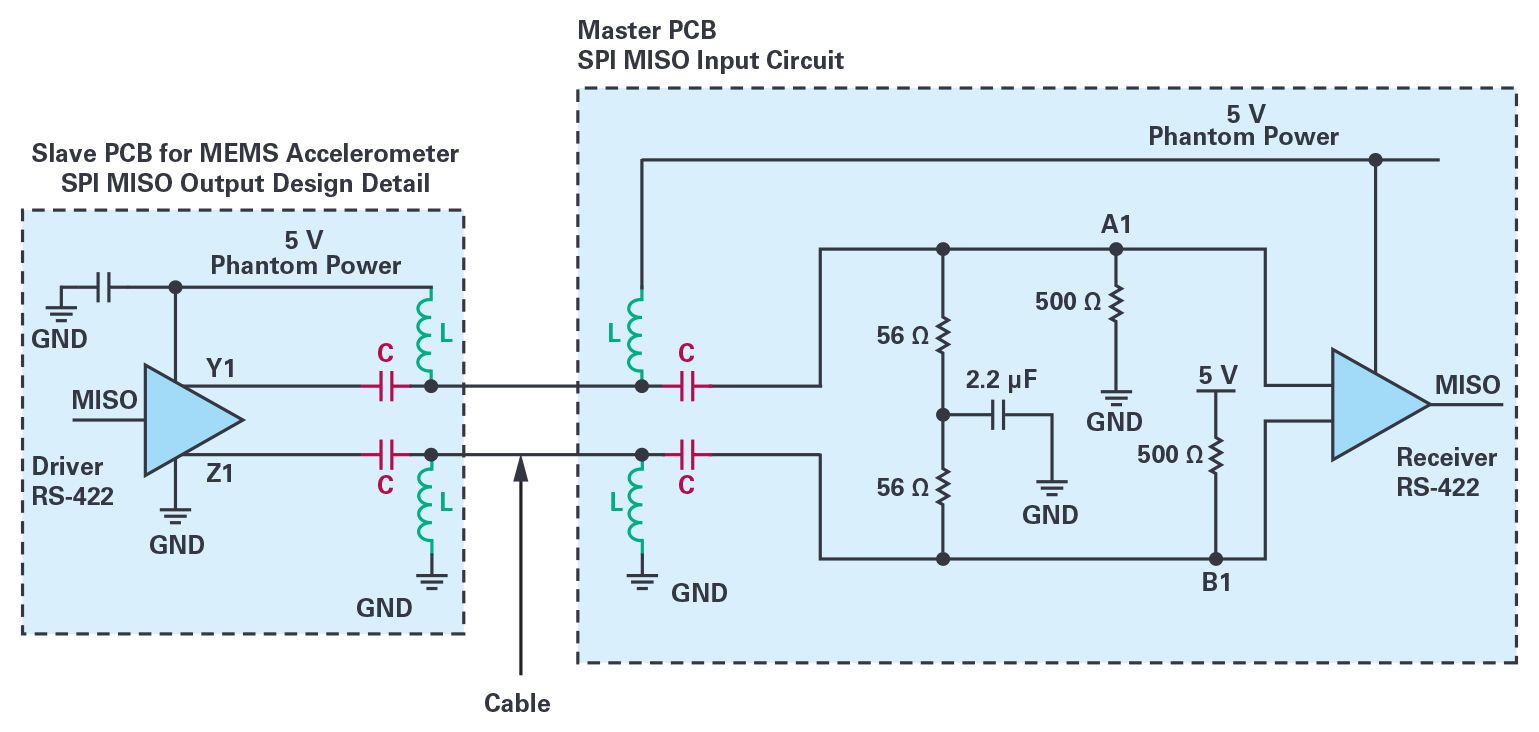

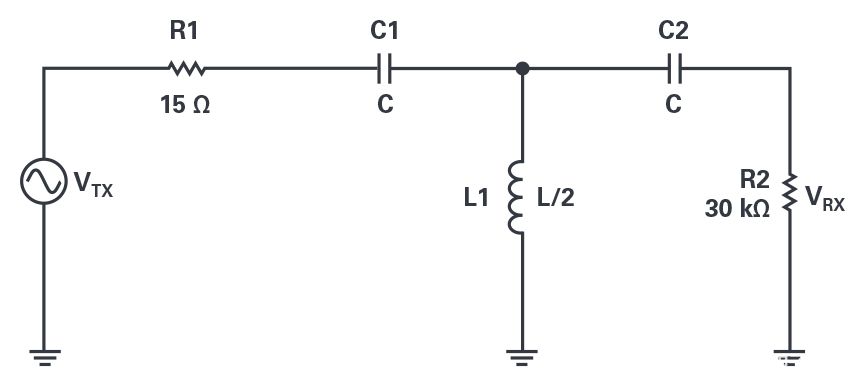

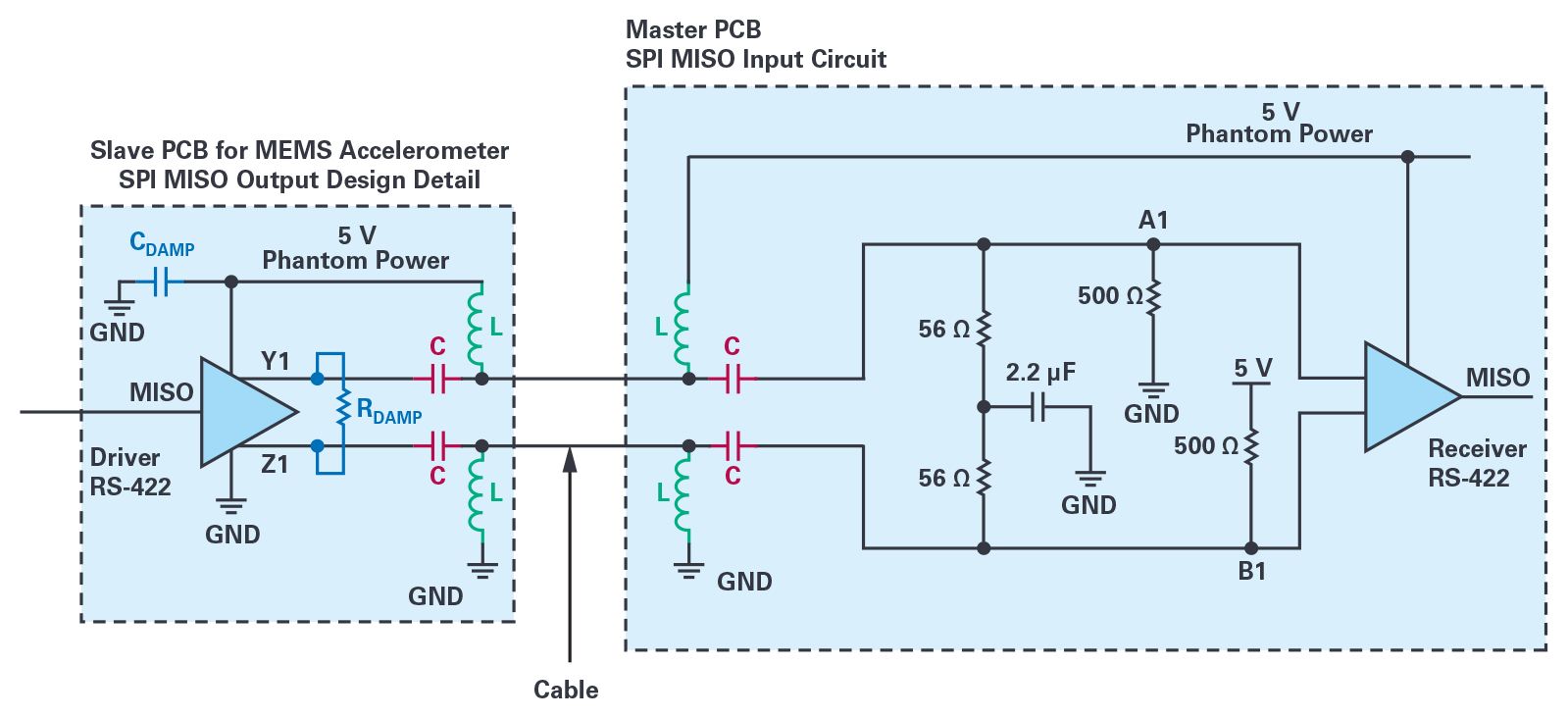

就本文而言,假设将幻象功率电感-电容网络添加到两根导线上,用于路由SPI MISO信号的RS-485/RS-422转换。图4显示了RS-485/RS-422的主从SPI设计以及SPI MISO数据线的幻象电源滤波器电路。滤波电路是高通的,因此要求传输的数据信号在直流或非常低的频率下没有内容。

图4.SPI至RS-485/RS-422设计和幻象电源滤波器电路。

二阶高通滤波器电路如图5所示,这是图4的简化表示。发送RS-485/RS-422设备的电压输出标记为V德克萨斯州,具有R1 15 Ω输出阻抗。R2 30 kΩ是接收RS-485/RS-422器件的标准输入阻抗。可以选择电感(L)和电容(C)值,以适应所需的系统数据速率。

图5.用于RS-422发送和RS-485/RS-422接收数据路径的二阶高通滤波器。

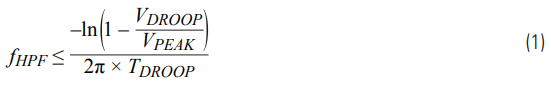

选择电感(L)和电容(C)值时,需要考虑最大RS-485/RS-422总线电压下降和下降时间,如图6所示。存在标准,例如单双绞线以太网,2其中规定了最大允许电压下降和下降时间,如图6a所示。对于某些系统,最大允许电压下降和下降时间可能更大,受信号极越点的限制,如图6b所示。

电压下降和下降时间可以与图5的仿真配合使用,以确定系统高通频率。

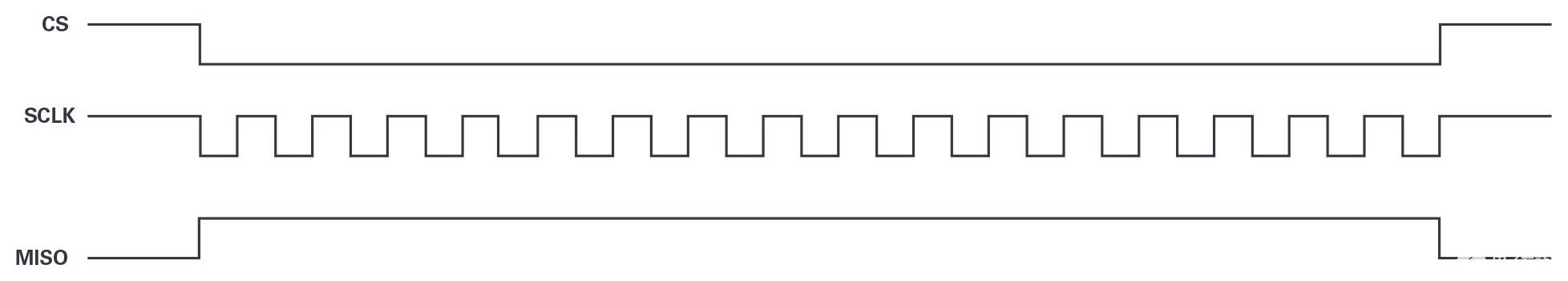

对于阻尼良好的系统,高通滤波器截止频率与下降要求之间的关系由公式1给出。3

图6.RS-422接收器的电压下降和下降时间。

在向RS-485/RS-422通信系统添加SPI幻象电源时,很明显,最小可能的SPI SCLK速率将受到幻象电源滤波器组件的限制。

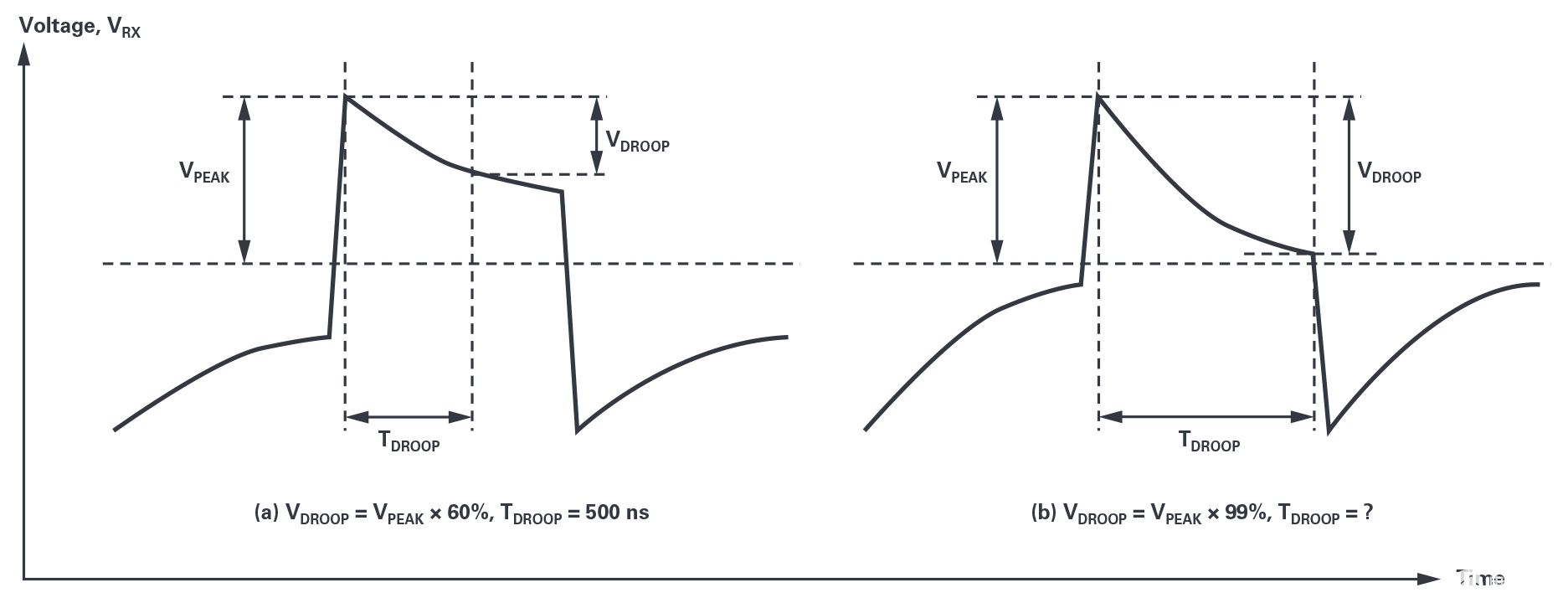

为了实现无位差错的可靠通信,需要考虑最坏情况下的最小SPI SCLK,例如,所有SPI MISO采样位均为逻辑高电平,如图7所示。如果所有采样的MISO位都是逻辑高电平,则会导致比特率低于系统SPI SCLK。例如,如果SPI SCLK为2 MHz,并且所有16位均为逻辑高电平,则幻象电源LC滤波器网络的等效SPI MISO比特率为125 kHz。

图7.SPI协议,带MISO 16位突发,全逻辑高电平。

如“时间同步和电缆长度”一节所述,更长的电缆需要较低的SPI SCLK速率。但是,幻象电源限制了可能的最低SPI SCLK速率。平衡这些相反的要求需要仔细选择和表征无源滤波器元件,尤其是电感器。

无源元件选择

选择合适的功率电感器时,需要考虑许多参数,包括足够的电感、额定/饱和电流、自谐振频率(SRF)、低直流电阻(DCR)和封装尺寸。表1给出了选定的功率电感器和感兴趣的参数。

额定电流需要满足或超过远程供电MEMS传感器节点的总电流要求,并且额定饱和电流需要大得多。

电感不会对高于其引用SRF的交流数据呈现高阻抗,并且在某一点将开始具有容性阻抗特性。所选电感SRF会将SPI上可以使用的最大SPI SCLK限制为RS-485/RS-422物理层,如表1所示。在长电缆上工作时,可能无法到达电感SRF;例如,可能无法通过 10 m 的电缆达到 11 MHz(部件号 744043101 的 SRF)的 SPI SCLK 速率。在其他情况下,当在长电缆上工作时,电感SRF可以达到较低的SPI SCLK速率(2.4 MHz,1.2 MHz)。如前所述,在幻象电源滤波器网络中使用时,电感也会限制尽可能低的SCLK速率。

较大的电感值采用 12.7 mm × 12.7 mm 封装,而较小值的电感器采用 4.8 mm × 4.8 mm 封装。

表2显示,由于物理限制(内部绕组),在减小电感尺寸的相反要求之间进行权衡具有挑战性。

| 部件号 | 升(微高) | 我额定(毫安) | 自谐振频率 (SRF) (兆赫) | 直流电阻 (Ω) | 包装尺寸(毫米) |

| 744043101 | 100 | 290 | 11 | 0.6 | 4.8 × 4.8 |

| LPS8045B-105 | 1000 | 230 | 1.3 | 3.22 | 8.0 × 8.0 |

| 76877530 | 1000 | 300 | 2.4 | 3.3 | 7.8 × 7.0 |

| SDR0805-102KL | 1000 | 210 | 3.0 | 4.5 | 7.8 × 7.8 |

| 7687714222 | 2200 | 260 | 1.2 | 6.5 | 10 × 10 |

| SRR1208-222KL | 2200 | 280 | 0.65 | 4.2 | 12.7 × 12.7 |

| 参数 | 对封装大小的影响 |

| 足够高的电感 | 电感值越高,内部绕组越大,封装尺寸越大。 |

| 更高的SRF | SRF 越高,内部绕组越少,尺寸越小。 |

| 更高的额定电流和饱和电流 | 内部绕组更少,但封装尺寸更大。 |

| 低直流电 | 为了实现更低的DCR,电线需要更粗,绕组更少。 |

选择合适的直流阻断电容器的限制仅限于瞬态过压额定值和直流电压额定值。直流电压额定值需要超过最大总线电压偏置,如图3所示。在电缆或连接器短路期间,电感电流将变得不平衡,并将被端接电阻耗散。隔直电容器需要额定峰值瞬态电压,以防短路。例如,在电感饱和电流约为1 A的低功率系统中,相应的隔直电容的额定电压应至少为50 V dc。4

系统实施

设计窗口和组件选择

在长RS-485/RS-422电缆上扩展时钟同步接口(如SPI)时,以及在同一双绞线(幻象电源)上组合电源和数据时,图8总结了本文中提到的设计约束。可能的最小SPI SCLK由幻象电源滤波器组件设置,这些元件在SPI数据线上高通滤波器数据。最大SPI SCLK由幻象功率电感自谐振频率(SRF)或系统传播延迟(以SPI SCLK值较低者为准)设置。

图8.设计窗口约束。

表3提供了建议的电感和电容值,以及通过仿真图5并使用图6和公式1作为指导确定的相应最小SPI SCLK。这假设 V下垂是 V 的 99%峰.该最小SPI SCLK还考虑了最坏情况,如图7所示,其中数据突发中的所有位均为逻辑高电平。相应的电缆长度使用图2估算。最大SPI SCLK由系统传播延迟或电感SRF值设置。

下面是一个计算示例。

要确定最大 SPI SCLK,请执行以下操作:

指定系统所需的电缆长度。在本例中,我们将选择 10 m 的 RS-485/RS-422 电缆。

使用图2确定系统可能的最大SPI SCLK。对于 10 m 的电缆,这大约是 2.6 MHz SPI SCLK。将最大SPI SCLK降额10%以允许LC元件容差,从而提供2.3 MHz的SPI SCLK。最大可能的SPI SCLK也可能受到所选电感的SRF的限制。

要确定最小 SPI SCLK,请执行以下操作:

考虑一个SPI协议,其中MISO线路上的所有位都是逻辑高电平。在本例中,我们将选择16位SPI协议,其中16位SPI MISO数据将在32次SCLK转换期间采样。如果所有 16 位均为逻辑高电平,则有效比特率为 2.3 MHz / 32 = 72 kHz。

使用图5和V上的72 kHz方波德克萨斯州、电缆 V 远端的电压波形接收可以模拟各种 L 和 C 值。随着电缆长度的增加,电感值和电感封装尺寸也会增加。电容值也会增加。

L 和 C 值的选择是主观的,取决于所需的下降设置,如图 6 所示。对于此示例,我们将假设 V下垂= V峰×99%。

使用 100 μH 电感器和 3.3 μF 电容以及 V 上的 72 kHz 方波德克萨斯州产生 T下垂7 μs,其中 V下垂= V峰×99%。

一 吨下垂6 μs 至 7 μs 相当于 2.3 MHz 至 2.6 MHz SPI SCLK。

如果选择100 μH (744043101)电感,则2.6 MHz的SPI SCLK低于11 MHz的电感SRF。

如果使用100 μH电感和3.3 μF电容,则元件PCB面积最小。当使用更大的电感器时,例如1000 μH或2200 μH,元件PCB面积可以增加三倍。理论最大值SPI SCLK由电感SRF设置,这在实践中可能是不可能的,例如,在没有时钟补偿的系统中,使用100 μH(744043101)在11 MHz时。

| L (μH) 和部件号 | 碳 (微F) | 最大SPI SCLK (MHz) | Max SPI SCLK Set By | Min SPI SCLK | 最大 RS-485/ RS-422 电缆长度 (m) |

| 100 (744043101) | 3.3 | 5.2 | 系统传播延迟 | 2.6兆赫 | 10 |

| 1000 (76877530) | 4.7 | 2.4 | 电感器SRF | 700千赫 | 60 |

| 2200 (7687714222) | 10 | 1.2 | 电感器SRF | 350千赫 | >100 |

如果使用更大的电感,例如2200 μH,则需要在网络中增加电容和电阻来抑制系统谐振。附加组件为蓝色,标记为 R潮湿(1 kΩ) 和 C潮湿(47 μF),见图9。

图9.为更大的电感和电容滤波器添加额外的系统阻尼。

实验设置

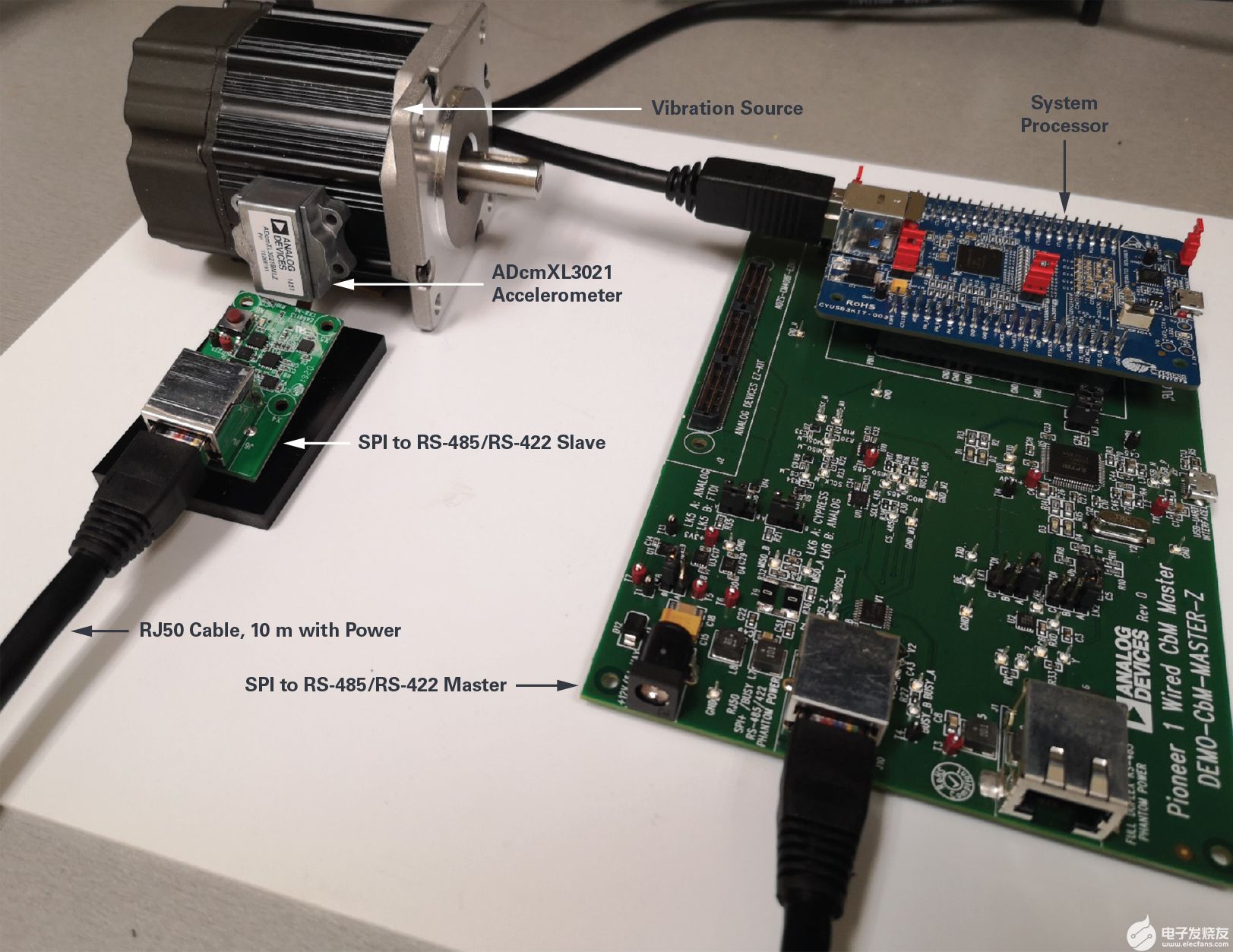

图10显示了ADI公司的有线CbM评估平台,以下简称先锋1。该系统使用本文第 1 部分中介绍的 SPI 至 RS-485/RS-422 设计解决方案。Pioneer 1还包括ADcmXL3021宽带宽、低噪声、三轴MEMS加速度计,该加速度计将高性能与各种信号处理相结合,以简化CbM系统中智能传感器节点的开发。SPI 至 RS-485/RS-422 从机将 ADcmXL3021 SPI 输出扩展回主控制器 10 m 以上,用于振动数据分析。SPI 至 RS-485 设计使用幻象功率 100 μH 电感器和 3.3 μF 电容,以最大限度地减小从接口解决方案的尺寸,其尺寸为 26 mm × 28 mm(不包括接口连接器)。

图 10.先锋1有线状态监测评估系统。

幻象电源线上的交流数据波形

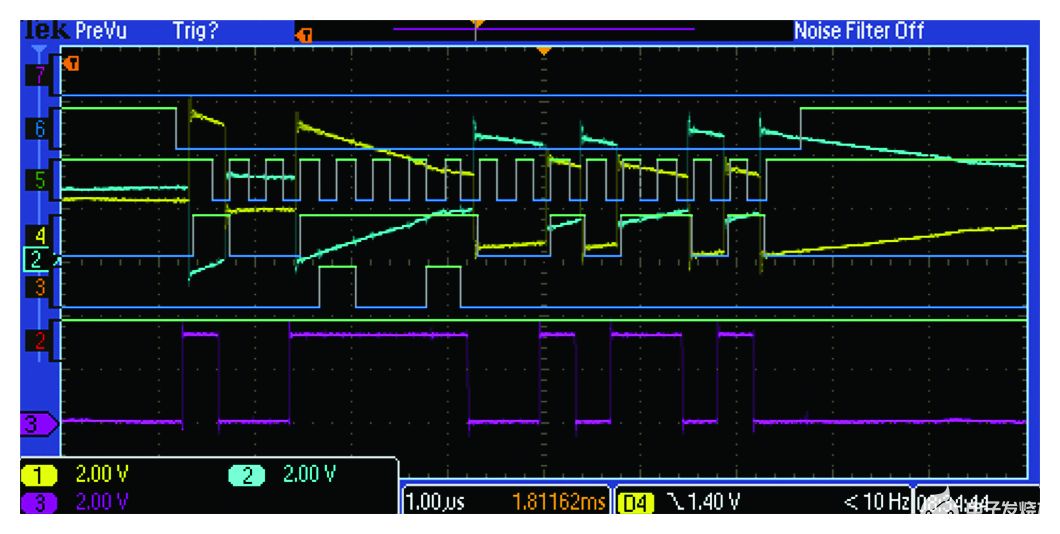

图11和表4描述了在SPI主机和从机以及RS-485/RS-422差分电压总线上测量的电压。这些电压是使用图10中的示例应用设置测量的。模拟信号1(黄色)和2(蓝色)是在SPI从输出端测量的MISO信号(紫色)的差分总线电压表示。数字信号4(黄色)显示了在主控制器采样的MISO。SPI主站的MISO信号与SPI从站MISO的极性和相位相匹配,传播延迟很小。

图 11.在SPI主机和从机以及RS-422差分电压总线上测量的电压。

| 参数 | 对封装大小的影响 |

| 2 数字(红色) | ADcmXL3021 忙于在主站测量 |

| 3 数字(橙色) | ADcmXL3021 MOSI 在主站测量 |

| 4 数字(黄色) | ADcmXL3021 味噌在主站测量 |

| 5 数字(绿色) | ADcmXL3021 标准数据终端测量 |

| 6 数字(蓝色) | ADcmXL3021 CS 作为主设备测量 |

| 3 模拟(紫色) | ADcmXL3021 从站测得的味噌 |

| 2 模拟(蓝色) | RS-422 Z引脚总线电压状态对应MISO;差分 Y 到 Z 对应于 3 个模拟(紫色)和 4 个数字(黄色) |

| 1 个模拟(黄色) | RS-422 Y引脚总线电压状态对应MISO;差分 Y 到 Z 对应于 3 个模拟(紫色)和 4 个数字(黄色) |

幻象电源线上的直流正确性

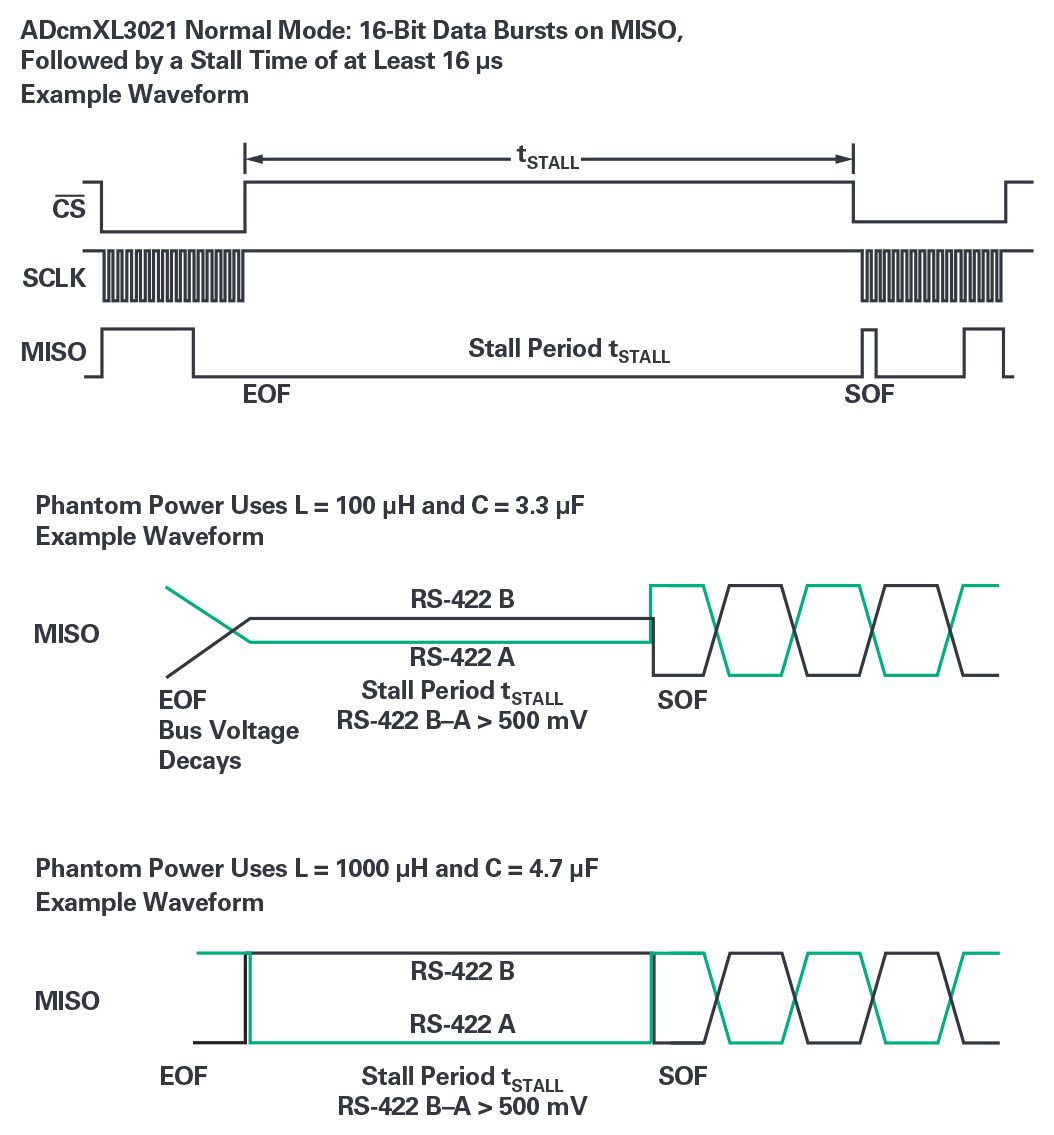

图12显示了ADcmXL3021的正常模式,其中包括一个SPI协议,该协议在MISO上发送16位数据突发,然后是失速周期(最小16 μs),然后是另一个16位数据突发。

图 12.幻象电源线上的直流正确性。

在幻象电源网络中,使用100 μH电感和3.3 μF电容:

在帧结束时(EOF),RS-485/RS-422总线电压衰减回稳定的直流状态。

失速周期直流稳态需要为500 mV>差分电压RS-422 B-A,这反映了ADcmXL3021 MISO高阻态,并确保ADM4168E收发器输出端的逻辑为0。如果使用500 Ω电阻,则可以保证这种空闲状态的正确性,如图4滤波电路所示。

然后,帧的下一个开始(SOF)将从低电平正确过渡到高电平,或者保持低电平,具体取决于ADcmXL3021的MISO数据输出。

失速周期RS-485/RS-422总线稳态未与SPI SCLK边沿对齐,因此随机噪声不会影响该时间段内的SPI MISO数据采样。

在幻象电源网络中,使用1000 μH电感和4.7 μF电容:

EOF、失速周期和SOF遵循ADcmXL3021 MISO输出,总线电压电平在失速期间不会衰减回500 mV最小直流稳态。可能会出现一些电压电平衰减,但不会达到500 mV电平。

有线评估解决方案

ADI公司开发了Pioneer 1有线系统评估解决方案,以支持ADcmXL3021三轴MEMS加速度计。如本维基指南所述,先锋1评估套件还可以借助维基指南中描述的扩展板支持表5中所示的MEMS器件。

| 部分 | 噪声密度(微克/√赫兹) | 范围(g) | 带宽(赫兹) | # 轴 |

| ADcmXL3021 | 26 | 50 | 10000 | 3 |

| ADXL357 | 80 | 10, 20, 40 | 1000 | 3 |

| ADXL372 | 200 | 3200 | 3 | |

| ADXL355 | 20 | 2, 4, 8 | 1000 | 3 |

| ADXL313 | 250 | 0.5, 1, 2, 4 | 1600 | 3 |

| ADXL363 | 550 | 2, 4, 8 | 200 | 3 |

| ADXL375 | 200 | 1600 | 3 | |

| ADXL362 | 175 | 2, 4, 8 | 200 | 3 |

| ADXL345 | 420 | 2, 4, 8, 16 | 1600 | 3 |

| ADXL350 | 1, 2, 4, 8 | 1600 | 3 | |

| ADXL343 | 不 | 2, 4, 8, 16 | 1600 | 3 |

| ADXL312 | 340 | 1.5, 3, 6, 12 | 1600 | 3 |

审核编辑:郭婷

-

SPI至RS-422/RS-1设计解决方案的详细物理层设计注意事项2023-02-02 6112

-

RS-232、RS-422与RS-485的区别2012-08-15 4956

-

RS-485和RS-422接口介绍2014-10-03 5347

-

RS-232、RS-422和RS-485串行数据接口标准2019-04-23 2629

-

使用RS-422和RS-485进行便捷,可靠的数据传输2020-09-18 3066

-

RS-422与RS-485接口的知识点分享2020-12-28 2975

-

RS-485注意事项是什么?2021-05-20 1597

-

USB/RS-485/RS-422/UT-850转换器使用说2009-05-14 971

-

RS-485/RS-422 Circuit Implemen2009-06-21 886

-

RS-232/RS-485/RS-422转换器解决方案2010-03-11 1032

-

RS-232C、RS-422与RS-485的由来2010-06-07 1051

-

RS-422 and RS-485 Application2010-06-30 1154

-

RS-422和RS-485的应用说明资料免费下载2019-04-09 1734

-

【理论】RS-232、RS-485、RS-422通信接口标准介绍2021-12-20 2093

-

RS-485/RS-422电路实施指南2024-03-07 950

全部0条评论

快来发表一下你的评论吧 !