什么是JESD204,我们为什么要关注它

描述

一个新的转换器接口正在稳步发展,并有望成为未来转换器的首选协议。这个新接口JESD204最初是在几年前推出的,但经过了修订,使其成为更具吸引力和效率的转换器接口。随着转换器分辨率和速度的提高,对更高效接口的需求也在增长。JESD204接口带来了这种效率,在速度、尺寸和成本方面,与互补金属氧化物半导体(CMOS)和低压差分信号(LVDS)前代产品相比具有多项优势。采用JESD204的设计具有更快的接口优势,可以跟上转换器更快的采样速率。此外,引脚数量减少,导致封装尺寸更小,走线路径数量更少,从而使电路板设计更加容易,并降低整体系统成本。该标准还易于扩展,因此可以进行调整以满足未来的需求。该标准所经历的两次修订已经证明了这一点。JESD204标准自2006年推出以来已经进行了两次修订,目前处于修订版B。随着越来越多的转换器供应商和用户以及FPGA制造商采用该标准,该标准已经得到改进,并添加了新功能,从而提高了效率和易于实施。该标准适用于模数转换器(ADC)和数模转换器(DAC),主要用作FPGA的通用接口(但也可以与ASIC一起使用)。

JESD204—这是什么?

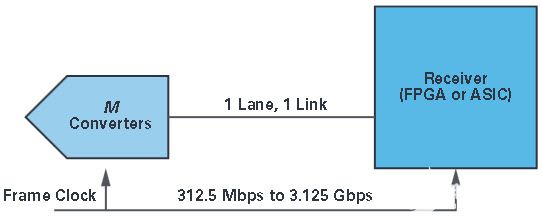

2006年4月,JESD204的原始版本发布。该标准描述了转换器和接收器之间的多千兆串行数据链路,通常是FPGA或ASIC等器件。在JESD204的原始版本中,串行数据链路定义为一个或多个转换器与接收器之间的单个串行通道。图 1 提供了图形表示。所示通道是M个转换器和接收器之间的物理接口,由利用电流模式逻辑(CML)驱动器和接收器的差分互连对组成。所示链路是在转换器和接收器之间建立的串行数据链路。帧时钟路由到转换器和接收器,并为器件之间的JESD204链路提供时钟。

图1.JESD204原始标准。

通道数据速率定义为每秒 312.5 兆比特 (Mbps) 和每秒 3.125 千兆比特 (Gbps),源阻抗和负载阻抗均定义为 100 Ω ±20%。差分电压电平定义为标称值为800 mV峰峰值,共模电压电平范围为0.72 V至1.23 V。该链路采用包含嵌入式时钟的8b/10b编码,消除了路由额外时钟线的必要性,也消除了在高数据速率下将附加时钟信号与传输数据对齐的相关复杂性。很明显,随着JESD204标准开始普及,该标准需要修订,以支持具有多个转换器的多个对齐串行通道,以适应转换器速度和分辨率的提高。

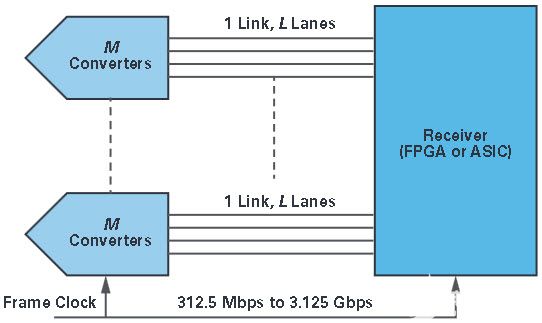

这一认识导致了JESD204标准的第一次修订,即JESD204A。该标准的修订增加了支持具有多个转换器的多个对齐串行通道的能力。支持312.5 Mbps至3.125 Gbps的通道数据速率保持不变,帧时钟和电气接口规格也保持不变。通过提高标准支持多个对齐串行通道的功能,具有高采样速率和高分辨率的转换器能够满足3.125 Gbps的最大支持数据速率。 图2显示了JESD204A修订版中为支持多通道而添加的附加功能的图形表示。

图2.第一次修订—JESD204A。

尽管最初的JESD204标准和修订后的JESD204A标准都比传统接口具有更高的性能,但它们仍然缺乏关键要素。这个缺失的元素是链路上序列化数据中的确定性延迟。处理转换器时,重要的是要知道采样信号与其数字表示之间的时序关系,以便在接收到信号后在模拟域中正确重建采样信号(当然,这种情况对于ADC来说也是如此,DAC的情况类似)。这种时序关系受转换器延迟的影响,对于ADC而言,延迟定义为输入信号采样边沿时刻与其数字表示出现在转换器输出端之间的时钟周期数。类似地,在DAC中,延迟定义为从数字信号时钟进入DAC到模拟输出开始变化之间的时钟周期数。在JESD204和JESD204A标准中,没有定义功能来确定转换器及其串行数字输入/输出的延迟。此外,转换器的速度和分辨率都在不断提高。这些因素导致了该标准的第二次修订版JESD204B的引入。

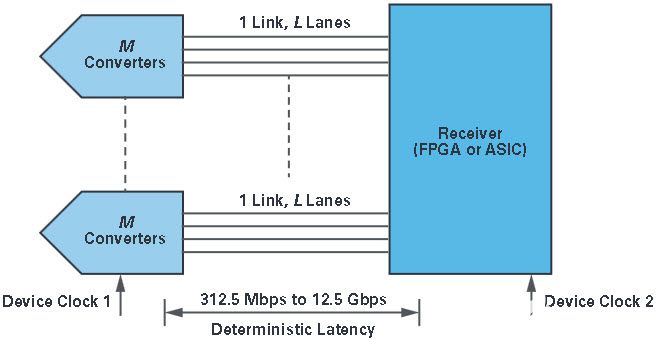

2011年7月,该标准的第二次也是当前修订版JESD204B发布。修订后的标准的关键组成部分之一是增加了实现确定性延迟的规定。此外,支持的数据速率被推高到12.5 Gbps,细分为不同的设备速度等级。此标准修订版要求从使用帧时钟作为主时钟源过渡到使用设备时钟作为主时钟源。图3显示了JESD204B版本添加的其他功能。

图3.第二个(当前)修订版 — JESD204B。

在JESD204标准的前两个版本中,没有定义任何规定来确保通过接口的确定性延迟。JESD204B修订版通过提供一种机制来解决这个问题,以确保从上电周期到上电周期以及跨链路重新同步事件,延迟应该是可重复和确定的。实现此目的的一种方法是,通过使用称为SYNC~的输入信号,在明确定义的时刻同时在所有通道上启动转换器中的初始通道对齐序列。另一种实现方式是使用SYSREF信号,这是JESD204B新定义的信号。SYSREF信号充当主定时参考,并对齐来自器件时钟的所有内部分频器以及每个发射器和接收器中的本地多帧时钟。这有助于确保通过系统的确定性延迟。JESD204B规范列出了三个器件子类:子类0——不支持确定性延迟;子类 1 - 使用 SYSREF 的确定性延迟;子类 2 — 使用 SYNC~ 的确定性延迟。子类0可以简单地与JESD204A链路进行比较。子类 1 主要用于工作在 500 MSPS 或高于 500 MSPS 的转换器,而子类 2 主要用于工作在 500 MSPS 以下的转换器。

除了确定性延迟外,JESD204B版本还将支持的通道数据速率提高到12.5 Gbps,并将设备分为三种不同的速度等级。对于定义为 100 Ω ±20% 的所有三个速度等级,源阻抗和负载阻抗相同。第一个速度等级与JESD204和JESD204A版本的通道数据速率一致,并定义了高达3.125 Gbps的通道数据速率的电气接口。JESD204B中的第二个速度等级定义了高达6.375 Gbps的通道数据速率的电气接口。该速度等级将最小差分电压电平从第一个速度等级的峰峰值降至400 mV。JESD204B中的第三级速度定义了高达12.5 Gbps的通道数据速率的电气接口。该速度等级将电气接口所需的最小差分电压电平降低到360 mV峰峰值。随着速度等级的通道数据速率增加,所需的最小差分电压电平降低,通过降低驱动器所需的压摆率,使物理实现更容易。

为了提供更大的灵活性,JESD204B版本从帧时钟过渡到器件时钟。以前,在JESD204和JESD204A修订版中,帧时钟是JESD204系统中的绝对时序参考。通常,转换器的帧时钟和采样时钟是相同的。这并没有提供很大的灵活性,并且在尝试将同一信号路由到多个设备并考虑不同路由路径之间的任何偏差时,可能会导致系统设计中不必要的复杂性。在JESD204B中,器件时钟是JESD204系统中每个元件的时序参考。每个转换器和接收器都从时钟发生器电路获得各自的设备时钟,该时钟发生器电路负责从公共源生成所有设备时钟。这为系统设计提供了更大的灵活性,但需要为给定设备指定帧时钟和设备时钟之间的关系。

JESD204—我们为什么要关注它?

就像LVDS几年前开始取代CMOS成为转换器数字接口的首选技术一样,JESD204也有望在未来几年走上类似的道路。虽然CMOS技术今天仍然徘徊,但它大多已被LVDS取代。转换器的速度和分辨率以及对低功耗的渴望最终使CMOS和LVDS不足以满足转换器的需求。随着CMOS输出端数据速率的增加,瞬态电流也会增加,从而导致更高的功耗。虽然LVDS的电流和功耗保持相对平稳,但该接口具有可以支持的速度上限。

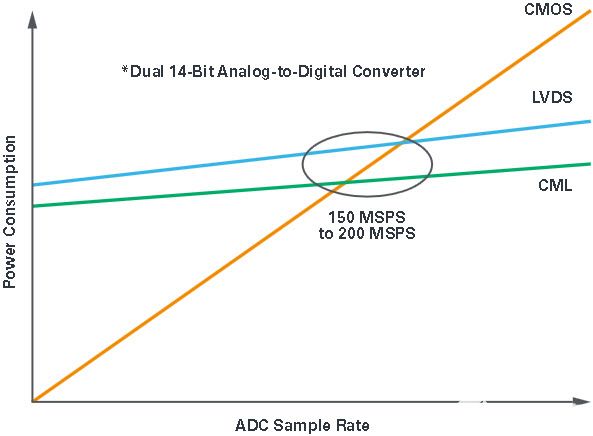

这是由于驱动程序架构以及必须全部同步到数据时钟的大量数据线。图4显示了双通道14位ADC的CMOS、LVDS和CML输出的不同功耗要求。

图4.CMOS、LVDS 和 CML 驱动器功耗比较。

在大约150 MSPS至200 MSPS和14位分辨率下,CML输出驱动器在功耗方面开始变得更加高效。由于数据的序列化,CML具有以下优点:与LVDS和CMOS驱动器相比,每个给定分辨率所需的输出对更少。为JESD204B接口指定的CML驱动器具有额外的优势,因为该规范要求随着采样速率的增加和输出线路速率的提高而降低峰峰值电压电平。

相同的转换器分辨率和采样率所需的引脚数量也大大减少。表1显示了使用具有不同通道数和位分辨率的200 MSPS转换器的三种不同接口的引脚数。对于CMOS和LVDS输出,数据假定每个通道的数据具有同步时钟,对于使用CML输出的JESD204B数据传输,最大数据速率为4.0 Gbps。使用CML驱动器发展到JESD204B的原因在查看此表并观察到引脚数的大幅减少时变得显而易见。

| 通道数 | 分辨率 | CMOS 引脚数 | LVDS 引脚数 (DDR) | CML 引脚数 (JESD204B) |

| 1 | 12 | 13 | 14 | 2 |

| 2 | 12 | 26 | 28 | 4 |

| 4 | 12 | 52 | 56 | 8 |

| 8 | 12 | 104 | 112 | 16 |

| 1 | 14 | 15 | 16 | 2 |

| 2 | 14 | 30 | 32 | 4 |

| 4 | 14 | 60 | 64 | 8 |

| 8 | 14 | 120 | 128 | 16 |

| 1 | 16 | 17 | 18 | 2 |

| 2 | 16 | 34 | 36 | 4 |

| 4 | 16 | 68 | 72 | 8 |

| 8 | 16 | 136 | 144 | 16 |

作为数据转换器领域的市场领导者,ADI公司已经看到了将转换器数字接口推向JEDEC定义的JESD204接口的趋势。ADI公司从一开始就参与了该标准,当时发布了第一个JESD204规范。迄今为止,ADI公司已经发布了几款具有JESD204和JESD204A兼容输出的转换器,目前正在开发输出与JESD204B兼容的产品。AD9639是一款四通道、12位170 MSPS/210 MSPS ADC,具有JESD204接口。AD9644和AD9641分别是14位80 MSPS/155 MSPS双通道和单通道ADC,具有JESD204A接口。从DAC的角度来看,最近发布的AD9128是一款双通道16位1.25 GSPS DAC,具有JESD204A接口。有关ADI公司在JESD204方面工作的更多信息,请访问 analog.com/jesd204。

随着转换器的速度和分辨率的提高,对更高效的数字接口的需求也在增加。业界通过JESD204串行数据接口开始实现这一点。接口规范不断发展,为转换器和FPGA(或ASIC)之间传输数据提供了一种更好、更快捷的方式。该接口经历了两次修订,以改进其实现并满足更高速度和更高分辨率转换器带来的日益增长的需求。展望转换器数字接口的未来,很明显,JESD204有望成为转换器数字接口的行业选择。每次修订都满足了改进其实施的要求,并允许标准不断发展以满足转换器技术变化带来的新要求。随着系统设计变得越来越复杂,转换器性能越来越高,JESD204标准应该能够适应和发展,以继续满足必要的新设计要求。

审核编辑:郭婷

-

JESD204B IP核的配置与使用2025-05-24 2712

-

请问AD9683的引脚如何与zynq 7015芯片中的 JESD204 ip核端口对应相连?2018-09-05 2718

-

JESD204 v5.2约束使用生成的dcp构建逻辑计时失败2018-10-19 3152

-

JESD204不允许生成比特流2019-01-02 5244

-

JESD204接口简介2019-05-29 2679

-

JESD204标准解析2019-06-17 3400

-

JESD204评估许可证问题2020-03-11 1835

-

为什么JESD204内核不使用GTX通道绑定功能来对齐通道?2020-08-18 1445

-

JESD204C标准值得注意的新特性2020-12-28 1610

-

为什么我们要重视JESD204?2021-04-13 1945

-

AD9683的引脚如何与zynq 7015芯片中的JESD204 ip核端口对应相连?2023-12-15 913

-

工程师,为什么要关注JESD204?2012-08-07 4147

-

采用JESD204标准的高速串行接口的应用2019-07-05 4130

-

什么是JESD204_我们为什么要关注它?2019-07-13 4372

-

JESD204——它是什么?2021-01-04 4491

全部0条评论

快来发表一下你的评论吧 !