应用笔记|管理STM32 MCU中的内存保护单元

描述

目录预览

1

前言

本应用笔记介绍如何管理 STM32 产品中的内存保护单元(MPU)。MPU 是用于存储器保护的可选组件。STM32 微控制器(MCU)中嵌入 MPU 之后变得更稳健可靠。在使用 MPU 之前,必须对其进行编程并加以启用。如果 MPU 没有启用,则存储系统的行为不会变化。

2

概述

MPU 可以使嵌入式系统更加稳健和安全:• 禁止用户应用程序破坏关键任务(例如操作系统核心)使用的数据• 将 SRAM 存储区域定义为非可执行(禁止执行 XN),以防止代码注入攻击• 修改存储访问属性MPU可最多保护16个内存区域。在 Armv6、Armv7 架构(Cortex-M0+、M3、M4、M7)下,这些区域可以依次拥有 8 个子区域(前提是区域至少有 256 字节))。

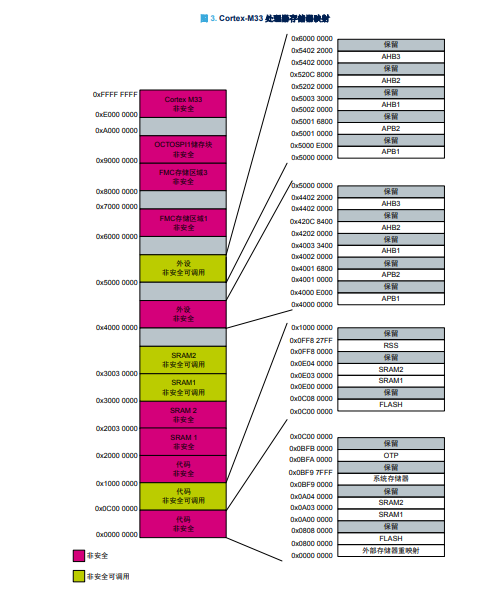

在 STM32 中,受保护区域的确切数量可能因内核和器件而有所不同,请参阅 Cortex-M33 MPU 寄存器获取详细信息。子区域的大小都是相等的,可以根据子区域号进行启用或禁用。因为最小区域大小是由缓存行长度(32 字节)驱动的,所以 8 个 32 字节的子区域对应一个 256 字节的区域。区域的编号为 0 至 15。

此外,还有一处默认区域,其 id 为-1。所有编号 0-15 的存储区域的优先级高于默认区域。这些区域可以重叠,也可以嵌套。区域 0-15 的优先级由低到高,这也决定了区域重叠的方式。优先级是固定的,不可更改。在 Armv8 架构(Cortex-M33)中,使用起始地址和终止地址来定义区域,使开发人员能够以灵活、简单的方式组织这些区域。

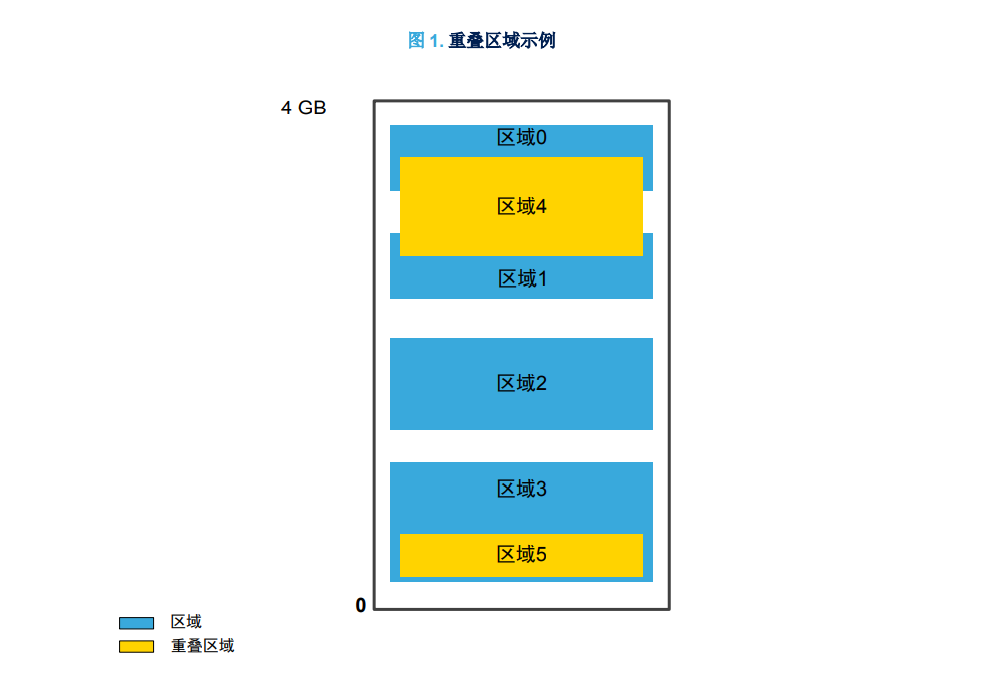

此外,正是区域大小的可灵活配置得到提升,故Cortex-M33就没有子区域的概念了。下图显示的示例包含六个区域。该示例显示区域 4 与区域 0 和 1 重叠。区域 5 完全包含在区域 3 内。因为优先级是递增的,所以重叠区域(橙色)优先。因此,如果区域 0 是可写的,而区域 4 不可写,那么位于区域 0 和区域 4 重叠部分的地址为不可写。

Conclusion:

在 Armv8 架构(Cortex-M33)中,现在不允许区域重叠。由于 MPU 区域的定义更加灵活,因此没有必要重叠MPU 区域。

MPU 是统一的,意味着没有单独的区域用于数据和指令。

MPU 还可以用于定义其他存储器属性(如可缓存性),可以导出到系统级缓存单元或存储存控制器。Arm 架构中的存储器属性设置可以支持两种级别的缓存:内部缓存和外部缓存。STM32F7 和 STM32H7 系列仅支持一种级别的缓存(L1-缓存)。

缓存控制由缓存控制寄存器实现全局控制,但 MPU 可以指定缓存策略以及区域是否可缓存。

2.1存储器模型

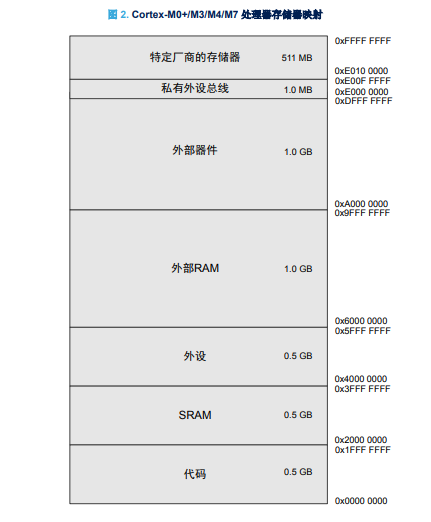

在 STM32 产品中,处理器具有固定的默认存储器映射,可提供最多 4 Gb 的可寻址存储器。

3

Cortex-M0+/M3/M4/M7

存储器类型、寄存器和属性

存储器映射和 MPU 编程将存储器映射分为多个区域。每个区域都有已定义的存储器类型和存储器属性。存储器类型和属性决定该区域的访问行为。

3.1 存储器类型

有三种常见的存储器类型:

• 普通存储器:允许 CPU 以有效方式安排字节、半字和字的加载和存储(编译器不了解存储器区域类型)。对于普通存储器区域,CPU 不一定按照程序中列出的顺序执行加载/存储操作。

• 器件存储器:在器件区域内,负载和存储是严格按照顺序进行的。这是为了确保以正确的顺序设置寄存器。

• 强排序存储器:所有操作始终按以编程方式列出的顺序执行,CPU 会等待加载/存储指令执行(有效的总线访问)结束,然后执行程序流中的下一条指令。这可能导致性能损失。

3.2 存储器属性

区域的属性与大小寄存器(MPU_RASR)是设置所有存储器属性的地方。该表显示了 MPU_RASR 寄存器中对于区域的属性和大小的简要描述。

前一个表格中的参数详情如下:

• XN 标志位控制代码的执行。为了在区域内执行指令,特权级别必须有读访问权限,而 XN 必须为 0。否则,会产生 MemManage 报错。

• 数据访问权限(AP)字段定义存储区域的 AP。

下表对访问权限进行了说明:

• S 字段面向可共享的存储区域:存储系统在一个有多个总线主控的系统(例如,一个处理器带一个 DMA 控制器)中提供总线主控之间的数据同步。强排序的存储器始终可共享。如果多个总线主控可以访问一个不可共享的存储区域,软件必须确保总线主控之间的数据一致性。STM32F7 系列和 STM32H7 系列不支持硬件一致性。S 字段相当于不可缓存的存储器。

• TEX、C 和 B 位用于定义区域的缓存属性,以及(在某种程度上)可共享性。按下表对其进行编码。

长按扫码关注公众号

更多资讯,尽在STM32

▽点击“阅读原文”,可下载原文档

原文标题:应用笔记|管理STM32 MCU中的内存保护单元

文章出处:【微信公众号:STM32单片机】欢迎添加关注!文章转载请注明出处。

-

RTThread支持内存保护功能吗?2025-10-14 478

-

芯海应用笔记:通用 MCU Flash 读写保护和 SWD 复用指导手册.2024-05-16 787

-

应用笔记 | STM32U575/585 MCU 硬件开发入门2023-09-28 5273

-

如何管理STM32产品中的内存保护单元(MPU)2023-09-07 655

-

Armv8-M内存模型与内存保护用户指南2023-08-02 888

-

如何管理STM32产品中的内存保护单元(MPU)2023-08-01 727

-

如何为MPC5744P配置内存保护单元?2023-04-04 833

-

管理STM32 MCU中的内存保护单元2022-12-23 1666

-

管理 STM32 MCU 中的内存保护单元2022-11-21 579

-

如何管理STM32产品中的MPU2022-09-28 496

-

为什么要使用MPU?MPU如何实现内存保护?2022-07-05 7511

-

Cortex-M内核的MPU内存保护单元2020-03-04 4915

全部0条评论

快来发表一下你的评论吧 !