MAX19693 DCLK抖动评估

描述

DATACLK输出边沿精度高度依赖于输入CLK信号的相位噪声。DATACLKP/N 源自 CLKP/N 输入,因此对系统的整体保真度贡献了最少的额外抖动或占空比误差。本文档详细介绍了MAX19693的建立和保持时序规格,以及其总峰峰值抖动的实验室测量。

介绍

系统时序分析通常采用加性抖动计算,以确保在温度、电压和工艺变化范围内满足正确的总线时序。从其他信号派生的时钟信号表现出占空比失真和抖动增加。千兆赫范围内的时钟速率会增加这些附加时序误差的影响。

MAX19693工作在高达2GHz的时钟频率。它对输入CLK进行分频以创建用于同步上游数字源的DATACLK信号。DATACLK 信号的微小时序变化可能导致数据接口违反设置和保持时序规范。准确量化这些误差可实现更稳健的系统设计。

数据CLK输出和数据输入时序

MAX19693的负保持时间会导致采样窗口在采样边沿之前塌陷。但是,负保持时间并不排除使用更长或正保持时间,它只是意味着采样在设置后很早就发生。保持时间可以更长,设计人员必须确保它们不违反后续设置时间要求。

DAC具有多个具有各种传播延迟的内部时钟,这些时钟决定了设置和 t拿相对于 DATACLK 输出信号的规格。MAX19693还支持双倍数据速率(DDR)和四路数据速率(QDR)数字输入速率。在 DDR 或 QDR 模式下,内部时钟系统的运行速度都比 DATACLK 快。在这种情况下,内部CLK在每个偶数时钟上升沿采样,而DATACLK输出从每个奇数时钟上升沿转换。数据系统的内部工作原理通常被掩盖,但只要最终用户遵循时序规范,它们就不应该成为问题。

数据输出函数

DATACLK是一种差分LVDS信号,用于将源数据(FPGA)与DAC输入时钟同步,以便在高速下正确进行采样对齐。源自DAC输入时钟的内部信号用于锁存四个12位LVDS输入端口上接收的数字数据:DAP/N[11:0]、DBP/N[11:0]、DCP/N[11:0]和DDP/N[11:0]。为了正确对输入数据端口信号进行时间对齐,该内部锁存时钟的一个版本作为输出信号提供给用户(DATACLK)。DATACLK 可以配置为 DDR 信号,它使用 DATACLK 的上升沿(0° 相位)和下降沿(180° 相位)来同步输入数据的锁存,也可以配置为四通道数据速率 (QDR),它使用上升(0° 相位)、上升 + 90°、下降(180° 相位)和下降 + 90° 来锁存 DAC 输入数据。

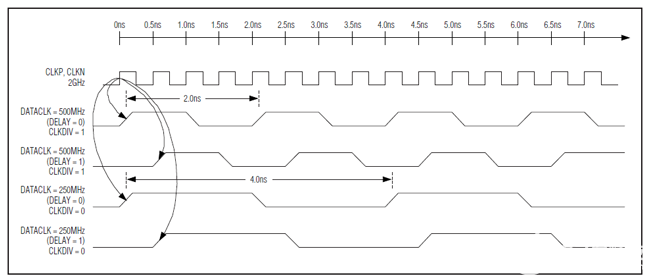

图1.DATACLK 输出和 CLK 输入时序对齐。

LVDS DATACLKP/DATACLKN (DATACLK) 输出信号通过基本的 D 触发器(2 分频或 4 分频)和缓冲电路从 CLKP/CLKN (CLK) 输入 DAC 时钟获得。由于DATACLK输出信号来自CLK输入信号,因此输入时钟上的任何抖动都将转换为输出时钟,并增加由内部缓冲和时钟域电路引起的系统抖动误差。此抖动“加法器”是所调查的值。

DATACLK 抖动和占空比误差 – 实验室分析

使用三种方法来测量DATACLK和CLK抖动,以提取DATACLK的占空比误差和抖动“加法器”。

首先是使用安捷伦/是德科技无限 DSA91304A(13GHz,40Gsps)数字信号分析仪,同时使用标准 50?输入和差分探头(7GHz,安捷伦 1134A)。输入DAC CLK的测量表明罗德与施瓦茨SMF100A信号发生器的抖动值大于预期。随后确定数字信号分析仪(DSA)的指定采样误差在500mV范围内为~17mV,从而产生~12ps峰峰值(~12ps)的最佳抖动测量能力。®®®®P-P).DSA的表现比这更好,在~6psP-P,但这不会提供回答 DATACLK 抖动问题所需的整体测量功能。

第二次尝试使用泰克 Tek 11801C 数字采样示波器 (DSO) 同时使用 50?采样头 (SD-26) 和高阻抗采样头 (SD-14)。遗憾的是,用于 Tek DSO 的触发方法要求将输入信号的一个版本连接到触发输入,通常使用功率分配器和延迟线 (DL-11)。由于 DATACLK 是输入时钟的 4 分频版本,因此采样边沿会产生类似眼图的迹线。Tek 11801C 没有高级抖动分析,直方图功能无法提供可靠的测量结果(大约 40ps®P-P输入时钟源的抖动)。

使用泰克 DPO72304SX 数字荧光示波器 (DPO) 测量 DATACLK 抖动的最终方法取得了成功。

实验室设置

MAX19693评估板用于测量抖动。评估板(EV kit)通过FPGA夹层卡(FMC)适配器连接到Xilinx VC707 FPGA评估系统,为MAX19693 RF DAC提供输入数据。罗德与施瓦茨SMF100A信号发生器配置为2.000GHz、+15dBm输出,作为连接到CLK SMA的MAX19693EVKIT的CLK源。评估板由两路实验室电源供电,一种为两个V供电1.8V。®DD和 AVCLK,第二个为 3.3V 用于 AVDD。泰克 DPO72304SX DPO 用于测量 CLK 输入和 DATACLK 输出抖动值。输入的CLK信号在评估板上的三路变压器网络之后连接到Tek P7713差分探头。类似地,另一个P7713差分探头连接到评估板上R2、R3输出抽头的DATA-CLKP/N输出信号。Tek DPO 配置为触发目标信号,并设置为使用 CLK 输入和 DATACLK 输出信号的“一键抖动”设置来测量抖动。

实验室结果

DAC时钟输入抖动和数据时钟输出抖动的评估可以采取几种不同的形式。Tek DPO 具有内置的分析算法,可测量时间间隔误差 (TIE)、总抖动 (TJ)、随机抖动 (RJ) 和确定性抖动 (DJ)。鉴于两个信号都应该是周期性的,并且基本上是固定的频率/数据速率,这些方法中的任何一种都应该指示MAX19693“增加”到系统中的抖动。

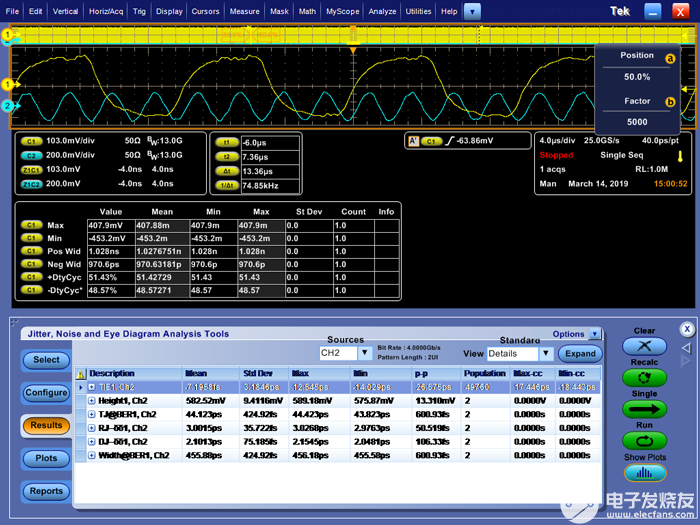

图5.CLK 输入抖动分析。

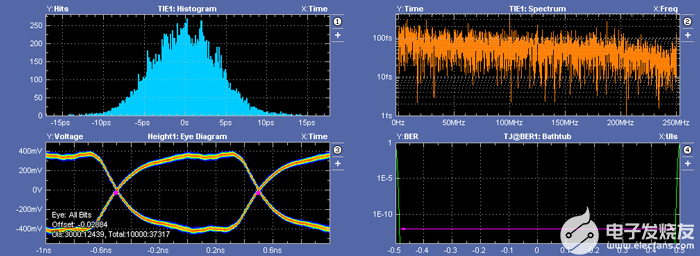

图6.CLK 直方图、眼图、TIE 光谱和浴缸图。

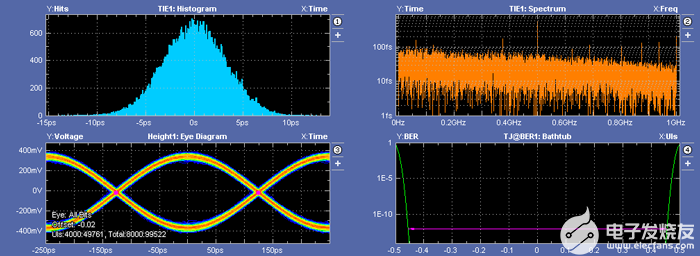

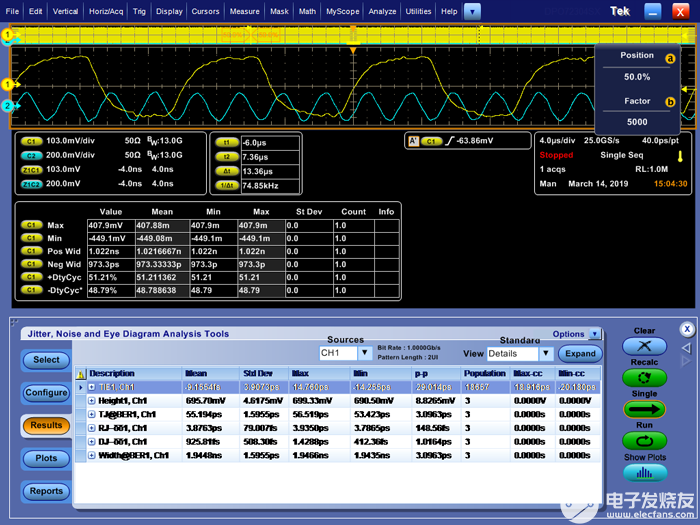

图7.DATACLK 输入抖动分析。

图8.DATACLK 直方图、眼图、领带谱和浴缸图。

下表汇总了收集的三个数据集以及输入 CLK 和输出 DATACLK 抖动测量的结果值:

表 1.CLK 输入抖动和 DATACLK 输出抖动测量

| 样本 | 绑P-P | 泰杰P-P | RJP-P | DJP-P |

|---|---|---|---|---|

| CLK 1 | 26.6点 | 601fs | 51fs | 106fs |

| DATACLK 1 | 29.0点 | 3.1点 | 149fs | 1.0ps |

| CLK 2 | 26.6点 | 601fs | 66.8fs | 727FS |

| DATACLK 2 | 29.0点 | 4.2点 | 275fs | 1.0ps |

| CLK 3 | 26.6点 | 788FS | 66.8fs | 727FS |

| 数据CLK 3 | 32,321 | 5.7点 | 275fs | 2.9点 |

直接从输出峰峰值抖动中减去输入峰峰值抖动,得到MAX19693的增量或总“增加”抖动。这种“增加”的抖动包括占空比误差和系统抖动的成分,如表2所示。

表 2.MAX19693 “新增”数据抖动

| 样本 | 绑P-P | 泰杰P-P |

|---|---|---|

| 样本 1 | 2.4点 | 2.5点 |

| 样本 2 | 3.3秒 | 3.6点 |

| 样本 3 | 5.5点 | 4.9点 |

| 样品 平均 | 3.7点 | 3.7点 |

对这三个样本求平均值,得出总“增加”峰峰值抖动的典型值为3.7ps。

数据抖动 – 仿真

仿真结果使用100mV幅度和10ps脉冲宽度的电源瞬变以及1ps上升/下降时间(500ps周期和+V)运行。e和 -Ve错开250ps。仿真选项包括无噪声选项、瞬态噪声选项和具有“蠕变”(每个周期10ps)的电源噪声序列,可提供异步电源噪声结果。蠕变仿真为300ns运行,噪声从100ns开始,在300ns时持续到结束,因此允许在200ns噪声窗口内使用大约100个周期的500MHz时钟。

表 3.MAX19693 模拟数据抖动

| 模拟 | 最小值 | 麦克斯 | JP-P | s |

|---|---|---|---|---|

| 无噪音 | -5.7fs | 10.8fs | 16.5fs | 3.3fs |

| 瞬态噪声 | -9.6fs | 14.4fs | 24.0fs | 5.4fs |

| 电源 噪音蠕变 | -1.56秒 | 2.12点 | 3.68点 | 0.84点 |

结论和建议

对内部电路的回顾和分析为“添加”到CLK输入的DATACLK输出抖动提供了2~4ps的保守估计。进一步的仿真和实际实验室测量都表明峰峰值抖动值约为3.7ps。基于这些结果,Maxim建议MAX19693 DATACLK“增加”输出抖动的保守值为4ps,用于时序预算计算。

审核编辑:郭婷

-

RC38208A评估板:高性能时钟综合与抖动衰减评估利器2025-12-26 933

-

max86178评估版无法蓝牙连接怎么解决?2023-11-30 438

-

MAX19692EVKIT-MAX19693EVKIT: Evaluation Kit for the MAX19692/MAX19693 Data Sheet MAX19692EVKIT-MAX19693EVKIT: Evaluation Kit for the MAX19692023-10-17 48

-

评估低抖动PLL时钟发生器的电源噪声抑制2023-04-11 2446

-

MAX19693 DCLK抖动评估2022-11-16 190

-

低抖动高精度时钟发生器MAX3625B相关资料分享2021-05-18 1106

-

UG-826:评估HMC7044双环时钟抖动清除器2021-05-12 857

-

请问怎样去测试MAX2607评估板?2021-04-20 1288

-

MAX40056评估套件免费试用2019-07-22 0

-

MAX44264评估板手册2011-10-19 3124

-

MAX9722AEVKIT MAX9722A、MAX9722B评估板2011-01-24 4109

-

MAX3624 低抖动、精密时钟发生器,提供四路输出2009-09-18 945

-

MAX7322EVCMAXQU-MAX7322EVKIT评估2008-05-06 743

全部0条评论

快来发表一下你的评论吧 !