高精度SAR模数转换器的抗混叠滤波考虑因素

描述

在物联网、大数据和云在行业媒体上风靡一时的时候,值得关注实现模拟世界数字化的技术进步。馈送云需要已经数字化的数据?模数转换器(ADC)是跨越这些领域的设备,是定义大数据质量和准确性的关键。ADC设计方法的进步不断突破界限,为我们周围的世界提供精确的数字表示。速度和分辨率可以以一种烧毁历史计量基准的方式推动。

高性能精密ADC在许多应用领域都很普遍。过程控制、可编程控制器、电机控制和电能分配是不同的例子。增加了不太日常的仪器领域,在这些领域中,所有类型技术的测试、研究、开发和鉴定都依赖于高精度数字转换。目前,几种ADC架构在精度方面存在竞争,根据其需求,选择符合模数转换原理,例如逐次逼近寄存器(SAR)与Σ-Δ,它们分别能够在几个MSPS下实现高达24位或更高的分辨率,在几百kSPS下能够达到32位。

当面对这些级别的分辨率和精度时,这些转换器提供的有用动态很容易超过100 dBFS(满量程)的神奇屏障,用户在设计用于数字化信号的模拟调理电路以及相关的抗混叠滤波器时面临着真正的挑战。在过去的二十年中,采样率和滤波技术发生了显着变化,现在可以结合使用模拟和数字滤波器,在性能和复杂性之间实现更好的折衷。

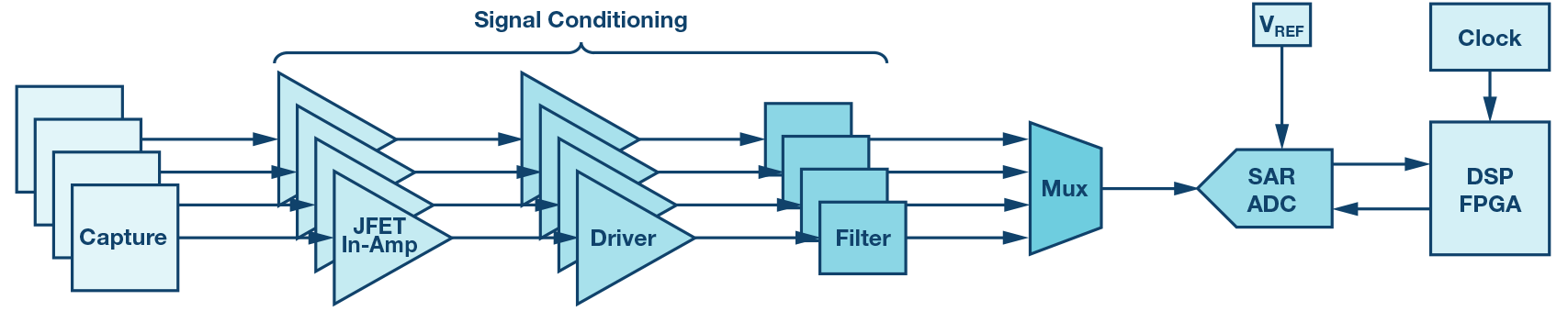

图1.典型测量信号链。

图1显示了数据采集系统这种分区的典型示例。在对差分或非差分信号(放大、缩放、电平的适应和转换等)进行调理后,后者在数字化之前被滤波以满足奈奎斯特准则。根据ADC的过采样速率,使用额外的数字滤波来符合采集系统的规格。

由于对非常宽输入动态的需求增加,上述许多应用都采用最先进的高分辨率ADC。随着动态性的提高,人们可以期待系统性能的提高,以及模拟调节链的压缩,拥堵和能源消耗的减少,甚至材料成本的降低。

过采样及其优点

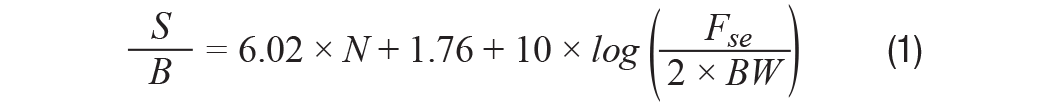

在出现非常快速、高分辨率的模数转换器之前,动态问题通过使用快速可编程增益放大器、更快的比较器和/或多个ADC的并联来解决,再加上适当的数字处理,以实现强信号的数字化并区分噪声电平附近的小幅度。在这些过时且现已过时的架构中,这转化为难以开发的复杂电路,并且在线性度、带宽和采样频率方面受到限制。目前的替代方案是通过利用现代更经济的ADC提供的高采样速率来应用过采样技术。以高于奈奎斯特定理规定的最小值的FSE速率对信号进行采样的操作可以通过处理和增加编码器的信噪比来执行增益操作,从而增加有效位的数量。事实上,量化噪声和热噪声被同化为白噪声,在整个奈奎斯特波段及以后均匀传播。过采样后,通过滤波并严格以所需的最小采样速率(2 × BW)工作来限制有用频段,每降低一个倍频程,噪声能量就会降低3 dB,如图2所示。换言之,理想情况下,过采样因子4可使信噪比理论上增加6 dB;也就是说,一个额外的位,如公式1所示:

总之,过采样有两个优点:即信噪比的提高,以及放宽对ADC之前的抗混叠模拟滤波器的要求。

图2.通过添加数字抽取滤波器来比较频谱噪声密度。

抗混叠滤波器:分区困境

理想情况下,与ADC相关的滤波器,特别是那些负责频谱混叠问题的滤波器,必须具有幅度响应,其可能带宽与其精度相比最平坦,并且具有足以适应其动态的带外衰减。过渡带通常应尽可能陡峭。因此,这些抗混叠低通滤波器必须具有能够消除寄生镜像、噪声和其他杂散音的特性。根据应用的不同,还应特别注意相位响应,并应补偿任何过大的相移。许多建议被认为是基本的,但当它们必须与指定的24位或32位转换器的要求相结合时,这些转换器的积分非线性误差仅为几个LSB和其他类似的静态和动态参数,则很难实现。

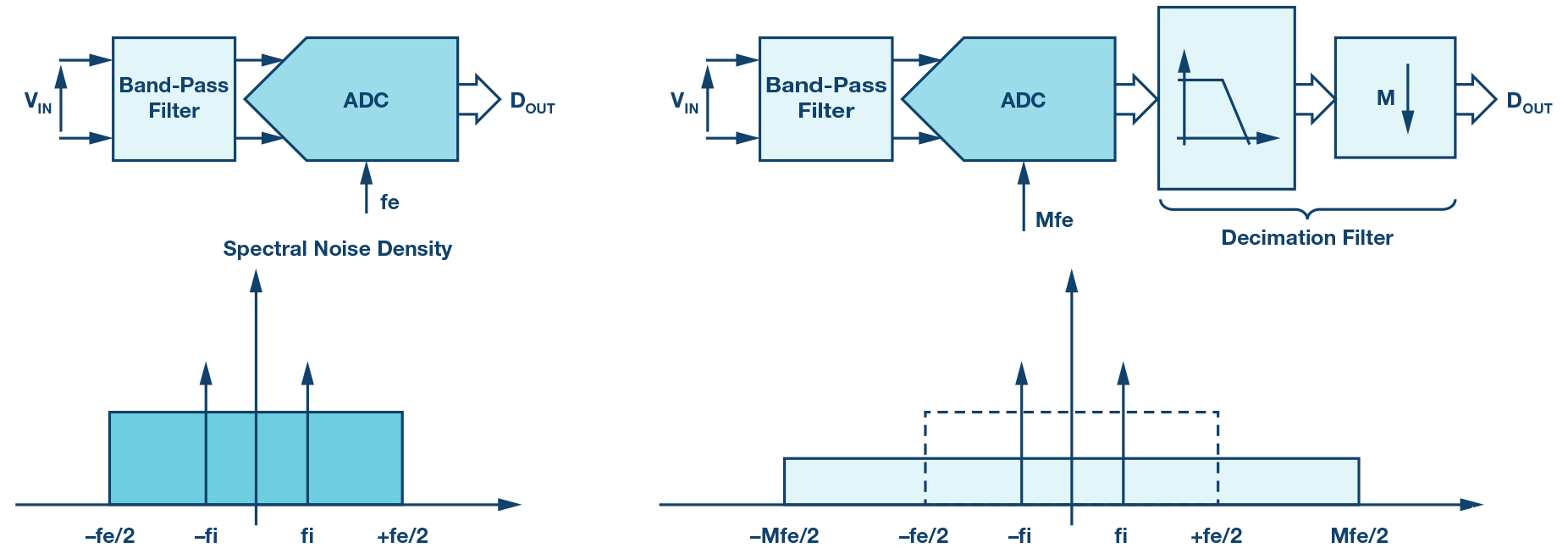

如前所述,对过采样的兴趣在这里变得非常重要,因为它不仅对信噪比有益,而且对模拟抗混叠滤波器规格及其截止频率的放宽也有好处。如图3c所示,过采样将转换带扩展至–3 dB截止频率和阻带起点之间。模拟抗混叠滤波器的阶数与过采样率成反比。表1中的数据说明了给定抑制目标的过采样率与模拟抗混叠滤波器阶数之间的关系。

图3.过采样、数字滤波和抽取降低了所需的模拟反化滤波器阶数。

目前的技术提供了高精度的SAR ADC转换速率,近年来大幅提高,目前18位分辨率从超过1 MSPS到15 MSPS。相比之下,宽带Σ-Δ型ADC以较低的吞吐速率提供更高的分辨率,具有非常高的过采样比。在数百kHz的等效(18位分辨率)输入带宽下查看Σ-Δ转换器是可能的,但内置了数字滤波的附加功能。

具有同等分辨率的Σ-Δ型ADC的带宽可达数百kHz,并具有内置数字滤波器的额外优势。这些ADC的基本特征是其整体计量精度,这与静态(直流)和动态(交流)参数有关,因此这些系统中的转换器和随附的模拟调理电路必须具有顶级规格。

相反,除过采样SAR(如LTC2512和LTC2500-32)外,大多数SAR ADC不包括数字滤波器,因此其工作不会受到一些不可避免的数字低通滤波的阻碍或限制,这会导致计算精度、带通纹波、衰减带抑制、传播时间和功耗之间的折衷。同时,AD7768-1等一些新型宽带Σ-Δ型ADC更加灵活,允许用户对其数字滤波器系数进行一定程度的可编程性。

LTC2378-20:市场上首款 20 位 SAR ADC

在性能竞赛中,2014年,凌力尔特(现为ADI公司的一部分)提供了首款具有20位分辨率和线性度的SAR ADC。LTC®2378-20 是一款出色的转换器,在接近 MSPS 的所有其他竞争产品中,它仍然独树一帜。

ADI公司的首款20位SAR ADCAD4020采用了略有不同的路径。AD4020兼具低噪声和低功耗特性,力求使信号链更易于客户使用。1.8 MSPS的低噪声和低能量是传统的矢量。但是,有一些关键的附加功能有助于硬件设计人员更轻松地实现必要的性能。模拟前端采样安静的能力就是一个例子。转换器转换回采集时,输入端的充电/放电一直是一个难题。典型的连锁反应是需要更高速的驱动器放大器。AD4020现在可以采用相当于目标实际信号带宽的高阻态模式低功耗精密放大器,从而提高测量精度。将转换时间限制在350 ns可以延长采集时间,这也使得选择放大器更容易,并且在数字端,在串行接口上读取数据时允许使用较慢的串行数据时钟。在隔离应用中,较慢的串行时钟可降低隔离器的EMI效应和电流消耗。采用AD7980系列和AD40xx系列其他16至18位成员共用的10引脚MSOP或10引脚QFN外壳,意味着硬件设计人员可以轻松升级平台设计选择。该器件采用1.8 V供电,在1.8 MSPS时功耗仅为15 mW。这种低元件功耗与降低信号链中支撑模块电流消耗的特性相结合,意味着能够以尽可能低的散热实现卓越的性能。

LTC2378-20 和 AD4020 的采样速率分别为 1 MSPS 和 1.8 MSPS,为过采样提供了极大的可能性,尤其是在音频频段或更远频段方面。为此,必须在外部FPGA或DSP中实现定制的抽取滤波器。如前所述,如有必要,可以绕过后者以将延迟降至最低。使用这些初级采样速率值,并考虑0 kHz至25 kHz频段,各自的过采样因子约为16或32,处理增益为12 dB至18 dB,同时抗混叠低通滤波器在严格按照奈奎斯特定理进行常规操作方面进行了简化。

ADC 至 DSP 链路:一切都是串行的

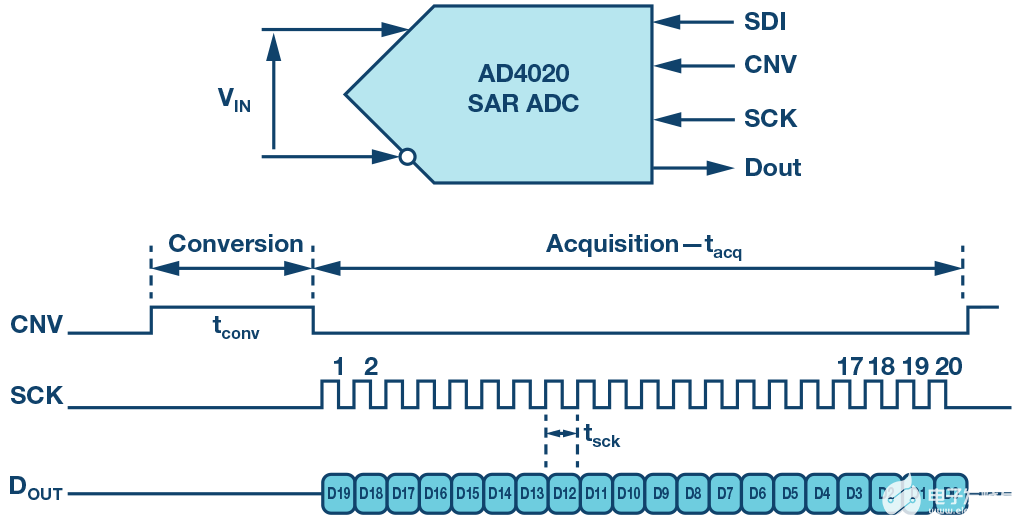

近年来,半导体行业及其设计师小圈子明显倾向于减小元件尺寸,导致外壳引脚真正放气,并以串行形式调节几乎所有数字输入或输出,这些输入或输出需要与SPI总线、同步串行端口等接口。这里所讨论的转换器没有留下用于提取样本和控制ADC各种功能选项的串行接口。这些串行接口符合与SPI或DSP串行端口兼容的条件,但实际上并非如此。充其量,它们隐藏了设置时钟信号节奏的移位寄存器,以便从设备中提取数据或在配置期间注入数据。与所有这些SAR ADC一样,LTC2378-20和AD4020对串行时钟(SCK)提出了频率要求,以标称采样速率恢复20位数据。由于数据读取的阶段严格限制在采集时间的持续时间(大约300 ns)内,因此在转换期间,外部访问上的数字活动必须减少到完全静音,并且时钟频率必须超过60 MHz才能在分配的时间内从采样中恢复所有位,同时遵守1 MSPS的采样速率。这是对负责从ADC收集数据的控制器接口的严格限制,既用于生成此类时钟频率,也涉及接收器端要实现的时间规格。LTC2378-20要求的最小SCK信号频率为64 MHz,这意味着它不能仅与任何通用微控制器或大多数具有同步串行端口(SPORT)的DSP接口,这些同步串行端口(SPORT)超过仅50 MHz的最大频率,但Blackfin系列的某些成员除外,例如ADSP-BF533或ADSP-BF561,它们可以达到90 Mbps。因此,人们担心使用与低抖动时钟生成电路相关的大型CPLD或FPGA至关重要。串行输出SAR ADC的大多数数字接口或多或少具有相同的时序和逻辑信号模式,如图4所示。至于SDI配置输入,除了级联模式外,它还以低得多的频率寻求。ADC采样周期的等效完整周期时间为®

从而定义最大采样频率,包括:

其本身受输出数据的读取速率的限制

图4.AD4020的时序图

幸运的是,AD4020的转换时间非常短,为325 ns,采样速率为1 MSPS,采集时间为675 ns,因此串行数据读取频率低于33 MHz;与DSP同步串行端口(如SHARC ADSP-21479)的频率相匹配的频率;能耗极低。®

LTC2512 和 LTC2500-32 过采样 SAR 允许用户在多个转换期间读出滤波输出寄存器的内容,从而降低了串行数据读取频率要求。宽带Σ-Δ型ADC在ADC转换期间不需要接口静默时间,从而进一步放宽了串行接口时钟时序。

超低功耗多通道采集系统

出于能耗、精度和工作模式选择灵活性的原因,以及出于商业原因,在这些领域不能考虑基于 FPGA 的解决方案。仅保留DSP浮点处理器来处理这些20位ADC的串行输出并实现优化的抽取滤波器。

如今,有许多数据采集系统能够在大量通道上同时采样。这意味着许多ADC并行运行,同时由同一控制器控制,该控制器还具有收集数据并将其存储在存储器中以供后续分析的任务。

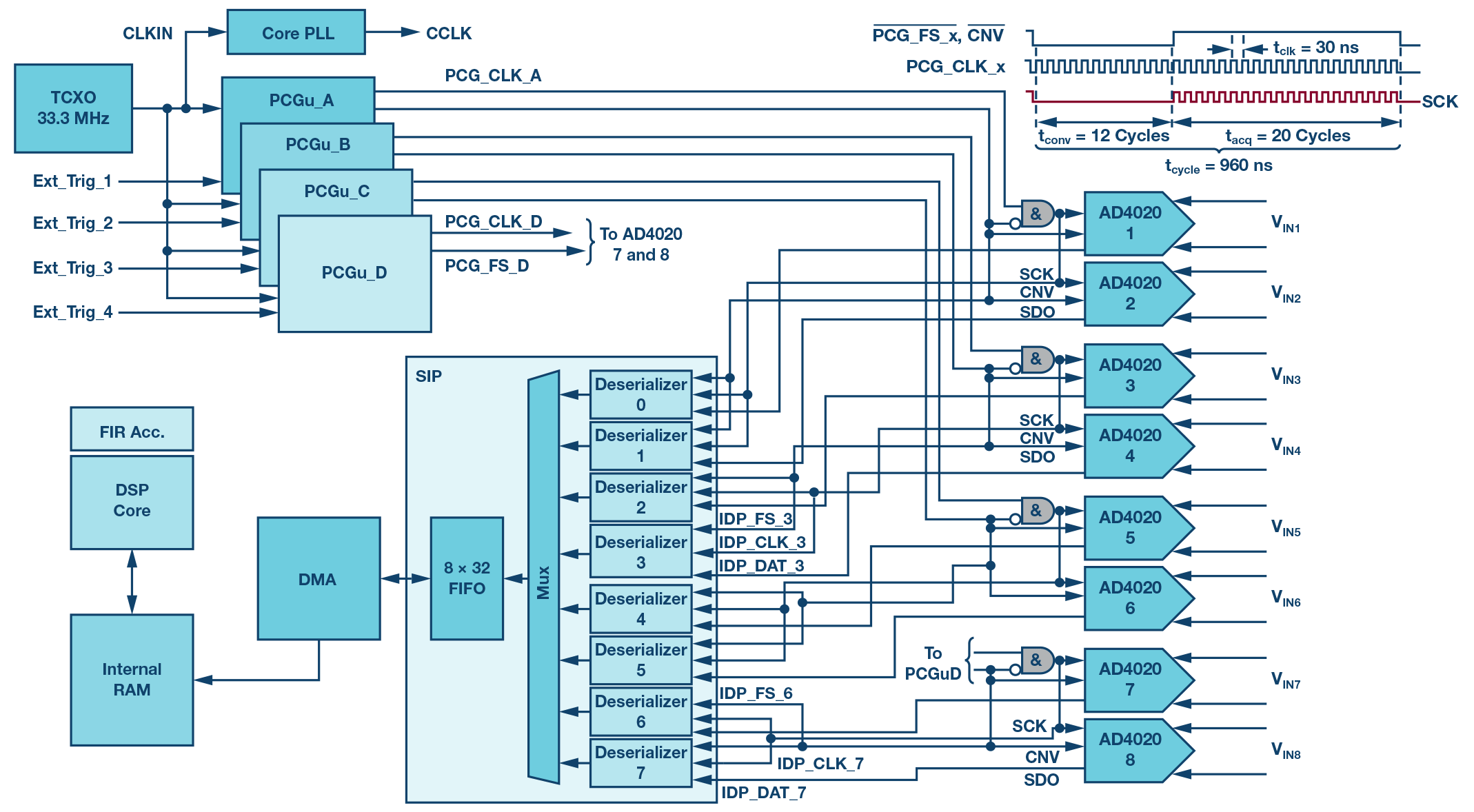

围绕SAR ADC构建的系统与SHARC ADSP-21479的功能相关,或者其快速ADSP-21469或ADSP-21489版本之一,时钟频率为450 MHz,不仅可以想象,而且在性能、开发时间、能耗和紧凑性方面是最相关的。这些处理器具有支持 8 个模数数字化通道所需的所有功能和外设,从同步串行接口到生成不同的时钟信号和触发转换。在所有SHARC处理器中,ADSP-21479是唯一采用低漏电、65 nm CMOS工艺制造的32位/40位浮点DSP,其优点是大大降低了泄漏或静态电流,结温的演变几乎呈指数级增长。动态电流是处理器及其外设的频率和活动的函数,也低于标准或快速CMOS制造工艺的动态电流。另一方面,与传统版本相比,最大CPU频率降低了约30%至40%,但在很大程度上足以满足此类应用程序的需求。

ADSP-21479具有许多外设,包括一个称为串行输入端口(SIP)的特殊模块,该模块能够同时接收来自8个外部串行端口发送器的流,与时钟和同步信号同步工作。事实上,可以将8个类似于AD4020的ADC直接连接到此接口,从而连接到处理器。如图5所示,8个通道有自己的IDP_SCK时钟,IDP_FS同步,IDP_DAT输入信号,其数据一旦解串,就会自动多路复用到32位、8字FIFO存储器中,然后通过64位DMA数据包或CPU执行的读取传输到SHARC内部RAM。在 DMA 传输操作中,SIP 由在自动乒乓模式下运行的双索引 DMA 通道提供服务。此外,ADSP-21479还具有四个精密时钟发生器(低抖动)或PCG,能够从内部或外部源(TCXO)生成独立的时钟和同步信号对。这些激励的频率、周期、脉冲宽度和相位通过编程20位内分频器获得。每个PCGx发生单元提供一对由AD4020转换器共享的CLK/FS信号,但在转换阶段时钟必须保持静音,这说明存在一个逻辑门,该逻辑门将IDP_FS和IDP_SCK信号组合在一起以创建SCK时钟。图5中的时间图显示,一旦转换时间tconv过去,必须尽快读取当前样本的20位,即以33.3 MHz的速率读取,以保持采样频率中的1 MSPS神奇屏障。大约600 ns后,数据被传输到其中一个SIP缓冲器,可以使用IDP_FS或CNV信号启动新的转换周期,以触发AD4020的新转换。后者的最大转换时间为325 ns,对应于CNV信号的脉冲宽度,即12 IDP_SCK时钟周期或360 ns。总之,如图5的时序图所示,一个完整的扫描周期需要32个IDP_SCK信号周期,即总共960 ns,最大采样速率为1.040 MSPS。

图 5.使用反序列化和 DMA 传输到 DSP 内部 RAM,将 8 个 20 位 1 MSPS SAR ADC 连接到 SHARC DSP。

同样,ADC LTC2378-20也可以与ADSP-21489相关联,因为它能够在高达50 MHz的更高外设时钟频率的时钟下工作,在这种情况下,采样速率为900 kSPS,如表1所示。不幸的是,静态电源电流(I丁特),或后者的泄漏远高于动态电流,这使得这种配置的总功耗超过可用瓦数,高得令人无法接受。

抽取滤波

假设这些转换器在过采样模式下使用,则有必要提供针对目标频段量身定制的抽取滤波器,满足上述性能要求,从而最大限度地减少对DSP在所需计算能力和能耗方面的影响。目前,改变采样率的过程已成为标准的数字信号处理操作,这些操作使用插值器和数字抽取器执行。出于相位响应线性的原因,低通抽取滤波器使用有限脉冲响应(FIR)拓扑,并且可以根据所寻求的效率程度使用不同的拓扑:

用于抽取的直接或优化的FIR滤波器

级联多速率FIR滤波器(半波段)

多相远红外滤波器

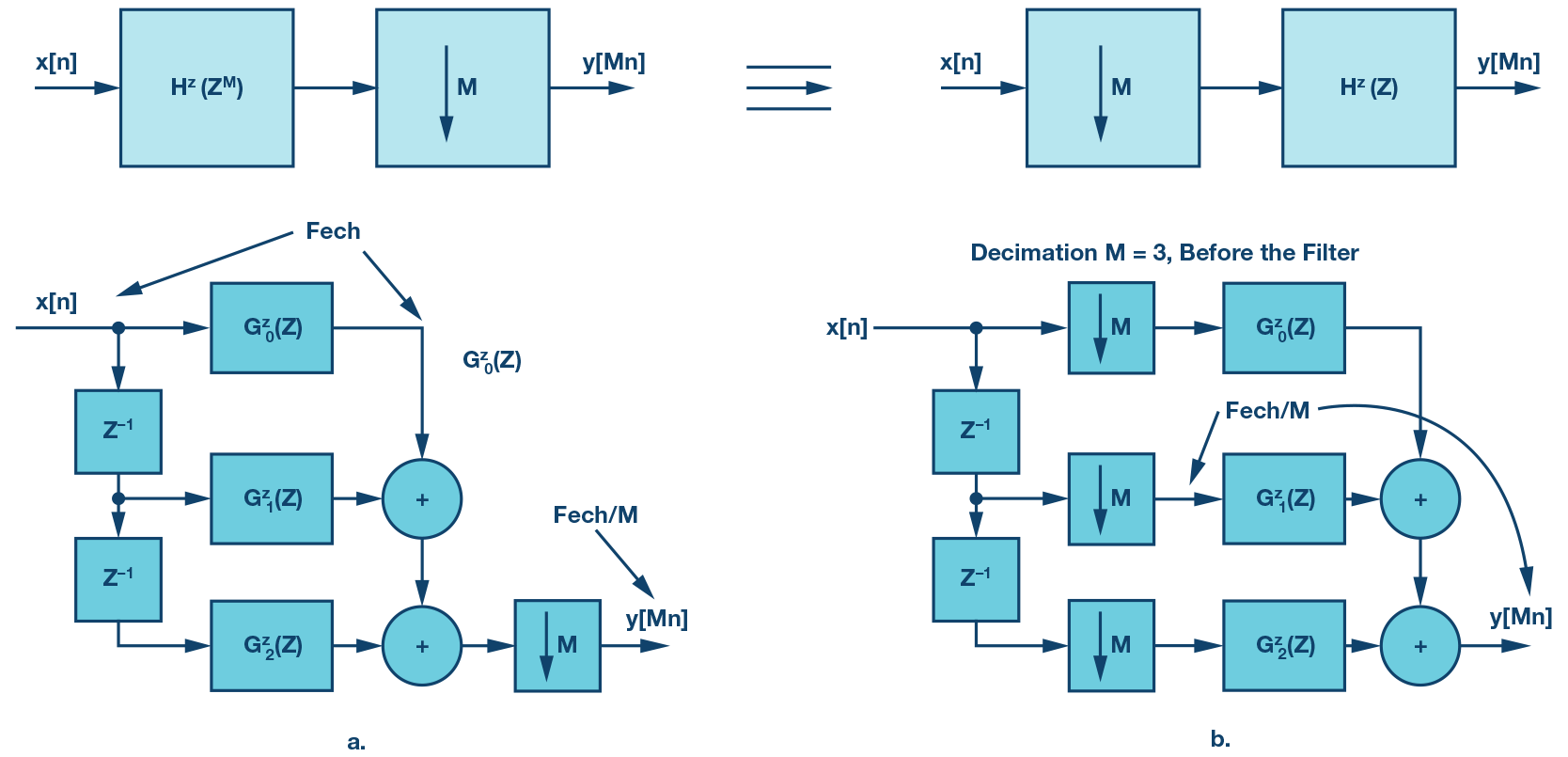

无论是FIR还是IIR类型的多相滤波器,都是抽取或插值滤波器最有效的实现之一。然而,数字处理的正统观念要求在抽取之前进行滤波。根据这一假设,1/M抽取滤波器由一个低通滤波器和一个采样频率降低级组成(图6a)。事先对信号进行滤波以避免频谱混叠,然后以M – 1的速率周期性地消除样本。然而,直接实现这些传统FIR或其他结构的抽取滤波器是浪费资源,因为因为拒绝的样本是由几十甚至数百个乘法累积(MAC)产生的。使用分解为几组滤波器或针对抽取优化的滤波器的多相滤波器,可以基于某些特性(如图6b所示)生产高效滤波器。

图6.传统的抽取滤波器和抽取滤波器采用多相方法。

SHARC ADSP-21479采用专用于FIR滤波的SIMD架构和硬件加速器,以及针对数字信号处理优化的指令集,特别适合实现这些类型的滤波器。每个SHARC处理元件都有一个32/40位乘法器累加器,能够以266 MHz的CPU频率每秒提供533个定点或浮点MAC。但是,对于某些具有明显延迟(房间均衡或声音效果)的应用,需要提高计算能力才能将内核从密集和持续的乘法运算中解放出来,例如 FIR、IIR 或 FFT 滤波,这些任务由专用硬件加速器执行。因此,用户将完全自由地利用CPU来计算更复杂的算法,这些算法需要完全复杂的指令集。专用于FIR滤波的加速器具有自己的本地存储器,用于存储数据和系数,并具有以下特征:

它支持 IEEE-754 定点或浮点 32 位算术格式

它有四个并行运行的乘法累加单元

它可以在单速率或多速率处理模式(抽取或插值)下运行

它可以在简单的迭代中处理多达 32 个 FIR 滤波器,总共 1024 个系数

ADSP-21479的加速器以系统时钟或PCLK外设的速率计时,是CPUCCLK时钟频率的一半;即 133 MHz。这导致总计算能力为每秒 533 个 MAC。加速器不要求执行指令;其操作由特定寄存器的配置决定,并且完全依赖于DMA传输在内部和/或外部存储器之间移动数据。

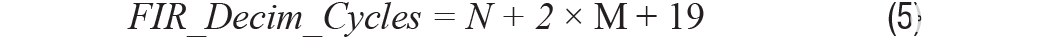

显然,该加速器将以优化的方式执行多速率滤波器(插值或抽取)的实现。由于简单的抽取滤波器仅为M输入信号提供一个输出结果,因此输出速率比输入速率低1/M倍。由于需要内存指针的数量,多相滤波器组的实施起来很复杂,无需诉诸复杂的多相滤波器组,这种优化的FIR滤波器组的实现只是利用了M-1个样本的输出来避免进行这些计算,并且只计算产生有用样本的数据。这消除了浪费,因此,操作数量以 M – 1 的比率(即本例中的 15 次)减少,从而大大节省了 CPU 周期。然而,对于这样的抽取比和较短的计算窗口,加速器不如具有两个计算单元的内核有效,并且会受到从一个滤波器到另一个滤波器的通道期间其DMA通道被重新编程的不利影响。在SISD模式下由单个计算单元实现时,这种滤波器在CCLK周期数方面的成本表示为:

N 是滤波器的系数数,M 是抽取比。

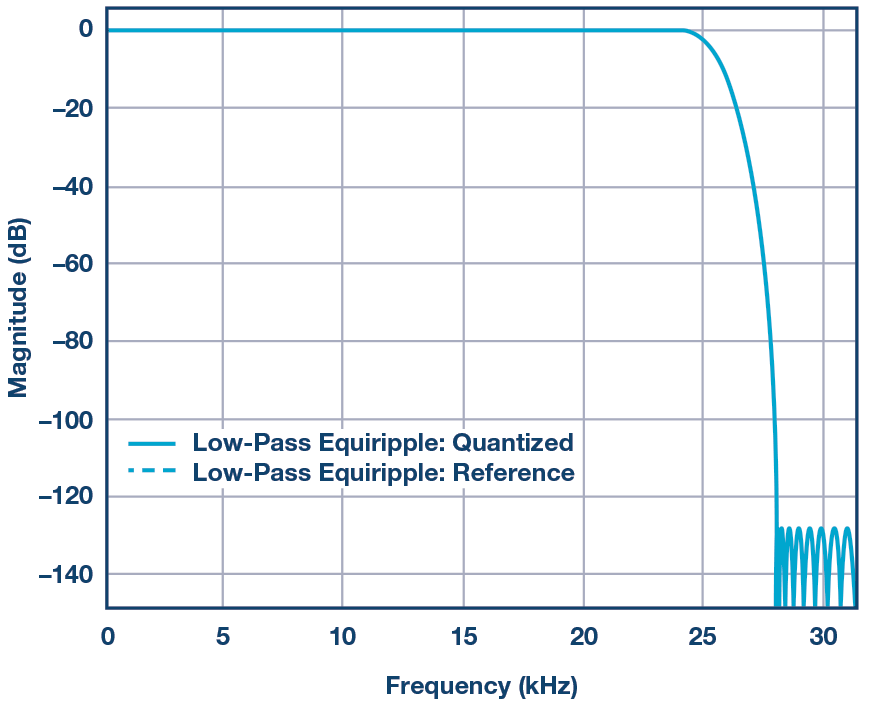

对于FIR滤波器(源到汇编器21k),对于FIR滤波器(源到汇编器21k)的实现相当于大约150个周期,对应于频带(0 kHz至24 kHz)中±0.00001 dB的纹波规格,对于62,500 SPS的采样率,带外衰减为–130 dB。该滤波器具有 97 个系数(以 32 位 FP IEEE-754 格式量化),其响应如图 7 所示,使用 MATLAB® 滤波器设计器。对于连接的SIP或ADC的每个活动通道,在DMA中断发生时,以此采样频率的速率重复此操作。

图7.抽取滤波器的滤波器响应。

对于实时和DSP负载,滤波操作以62.5 kSPS的频率重复,代表9,375,053个CCLK周期,而8个ADC转换通道的滤波操作略多于8倍,因为每个滤波器的存储器指针值都保存和恢复,存储在SHARC数据地址生成器中。这意味着每秒 8000 万个执行周期,或在 SISD 模式下 SHARC DSP 的执行周期为 80 MIPS,在 SIMD 模式下为一半,两个处理元素并行运行。根据上述模式,这八个抽取器FIR滤波器的执行占用了时钟频率为266 MHz的ADSP-21479,速率分别为30%和15%。

最后,能源消耗

虽然转换器的能耗可以根据其规格轻松准确地进行评估,但处理器的能耗更加困难,因为输入该消耗方程的参数数量以及根据实时约束和操作模式的巨大可变性。无需详细介绍,读者可以在与估算ADSP-214xx和ADSP-21479处理器各种组件的能耗相关的技术笔记中轻松找到,其中考虑了功能模块的活动、静态电流的结温、电源电压值、使用的输入输出引脚数量, 各种外部频率和容性负载。根据图5的功能描述,给出了DSP和ADC的几种组合,对应于此类抽取滤波应用的DSP活动的能量消耗。这些具有四个或八个ADC的相关DSP变体是根据功能容量、足够输入/输出的数量、处理器的计算能力以及ADC的整体性能建立的。由于静态电流非常低,围绕ADSP-21479及其8个SAR ADC集群构建的解决方案能耗最低,同时在滤波算法和其他数字功能选择方面提供了完全的自由度,整体性能充其量是出色的。

这个多通道数据采集系统(DAQ)示例还表明,使用FPGA并不是处理数字信号处理任务所必需的,浮点DSP更适合高精度SAR ADC,特别是当功耗是一个热点问题时。

| 参数 | AD4020和ADSP-21479 | LTC2378 和 ADSP-21489 | AD4020和ADSP-BF532 | LTC2378 和 ADSP-BF532 | LTC2512 -24 | LTC2500 -32 | AD7768 -1 中等模式 | AD7768 -1 快速模式 |

| 转换 A/N | 特区 | 特区 | 特区 | 特区 | 特区 | 特区 | WB-Σ-δ | WB-Σ-δ |

| 分辨率 | 20 | 20 | 20 | 20 | 24 | 32 | 24 | 24 |

| 过采样 | 是的 | 是的 | 是的 | 是的 | 是的 | 是的 | 是的 | 是的 |

| 带内纹波 (dB) | ±0.00001 | ±0.00001 | ±0.00001 | ±0.00001 | ±0.001 | ±0.001 | ±0.003可编程 | ±0.003可编程 |

| 阻带 (dB) | <–130 | <–130 | <–120 | <–120 | <–65 | <–65 | –110 可编程 | –110 可编程 |

| 抽取滤波器 | 选择远红外 | 选择远红外 | 选择远红外 | 选择远红外 | 冷杉 | 冷杉 | 冷杉 | 冷杉 |

| 采样频率 | 1 | 0.91 | 1.8 | 1 | 1.0 | 1 | 4 | 8 |

| 有效过采样率 | 16 | 16 | 32 | 16 | 16 | 16 | 128 | 256 |

| 第一个混叠区域 (MHz) | 1 | 1 | 2 | 1 | 1 | 1 | 8 | 16 |

| 抽取后频率 (kSPS) | 62.5 | 62.5 | 62.5 | 62.5 | 62.5 | 62.5 | 62.5 | 62.5 |

| 实现 –110 dB 混叠抑制所需的 AAF 阶数 | 5 | 5 | 4 | 5 | 5 | 5 | 3 | 3 |

| 滤波器阶数高于 (dB) 时的混叠抑制 | –123.4 | –123.4 | –123.4 | –123.4 | –123.4 | 62.5 | –130 | –147.5 |

| 3 kHz 时的信噪比,采用 5 V 基准电压源 (dBFS) | 112 | 116 | 115 | 116 | 114 | 116 | 113.7 | 116.9 |

| 2 kHz 时的 SFDR (dBc) | 122 | 128 | 122 | 128 | 120 | 128 | 128 | 128 |

| 20 kHz 时的 THD (dBfs) | 122 | 128 | 122 | 128 | 120 | 128 | –120 | –120 |

| 数字滤波器旁路 | 是的 | 是的 | 是的 | 是的 | 是的 | 是的 | 不 | 不 |

| 频率 SCK/SDO (MHz) | 33.3 | 50 | 61.5 | 64.1 | 1.5 | 1.5 | 1.5 | 1.5 |

| 模数转换器功耗(毫瓦) | 10.8 | 24.8 | 15 | 24.8 | 32 | 30 | 19.7 | 36.8 |

| 数字输出脉冲功耗(毫瓦) | 185 | 832 | 70 | 75 | ||||

| 通道数 | 8 | 8 | 4 | 4 | 1 | 1 | 1 | 1 |

|

总能耗(通常在 Tj = 55°C 时)( mW) |

272 | 1030 | 130 | 175 | ||||

| 每通道能耗 (mW) | 34 | 129 | 33 | 43 | 32 | 30 | 19.7 | 36.8 |

| 模数转换器工作温度范围(°C) | –40 至 +125 | –40 至 +85 | –40 至 +125 | –40 至 +85 | –40 至 +85 | –40 至 +85 | –40 至 +125 | –40 至 +125 |

-

关于设计抗混叠滤波器的三大注意事项2018-07-11 18429

-

抗混叠滤波器设计的3条指导原则2018-09-05 2690

-

AD9276BSVZ模数转换器2018-10-26 1406

-

SAR模数转换器AD7989-1和AD7989-52018-11-29 2427

-

高精度SAR模数转换器的抗混叠滤波考虑因素有哪些2021-01-11 1767

-

高精度数据采集中抗混叠滤波器的设计2010-12-09 734

-

精密SAR模数转换器的前端放大器和RC滤波器设计2016-01-07 1232

-

关于设计抗混叠滤波器容易忽视的三条建议2018-07-19 9376

-

多角度讲解高精度SAR ADC的抗混叠滤波考虑因素2018-11-02 6926

-

高精度SAR模数转换器的抗混叠滤波考虑因素2019-03-29 1103

-

多角度讲解高精度 SAR ADC的抗混叠滤波考虑因素2021-02-21 3473

-

设计抗混叠滤波器的三个指导原则是什么2021-11-10 1267

-

高精度 SAR ADC的抗混叠滤波考虑因素2022-12-21 1578

-

高精度SAR模数转换器抗混叠滤波的考虑因素2023-11-23 568

全部0条评论

快来发表一下你的评论吧 !