浅谈半导体技术的未来发展路线图

制造/封装

描述

在最近的超大规模集成电路国际研讨会上,台积电研发高级副总裁Y.J. Mii博士发表了题为“Semiconductor Innovations, from Device to System”的演讲。该演示文稿包含了对台积电未来研发计划的见解,超越了当前的路线图。还强调了正在研究的技术的相关挑战。本文总结了Mii博士的精彩演讲。

技术驱动

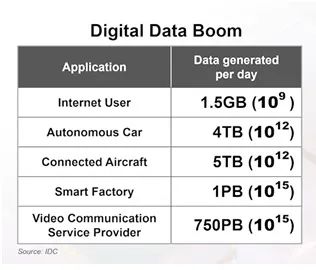

Mii博士首先对未来终端市场的增长进行了预测,强调了持续提高高性能计算吞吐量的必要性和对能效的关注。对于HPC的需求,他分享了一个“数据热潮”的预测,如下图所示。例如,“智能”工厂预计每天收集、监控和分析1 PB的数据。

数据热潮

机器学习(训练和推理)支持上述应用程序的作用也将扩大,对HPC吞吐量提出了进一步的要求。Mii博士评论说,这些HPC要求将继续推动研发工作,以提高半导体工艺路线图和先进(异构)封装技术中的逻辑密度。

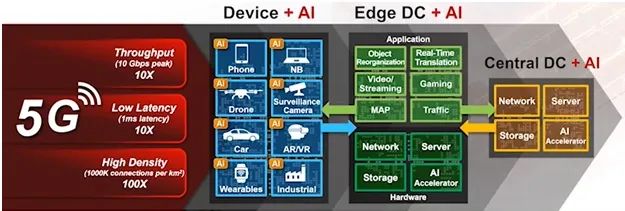

下图展示了对电源效率的密切关注。

上图所示架构不仅说明了5G(很快变成6G)将在我们使用的设备中普及的程度,而且还说明了“边缘数据中心”的运营。与HPC应用程序一样,机器学习算法的影响将无处不在,需要关注能效。

最近的技术创新

在介绍台积电的一些研发项目之前,Mii博士简要总结了最近的半导体工艺技术创新。

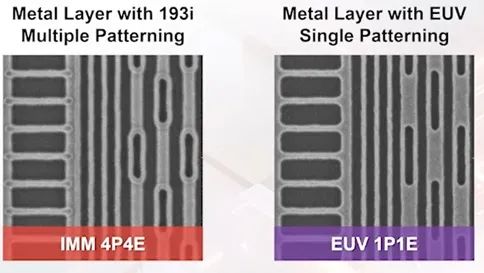

•在节点N7+引入EUV光刻

用于改善载波移动性的SiGe-pFET信道

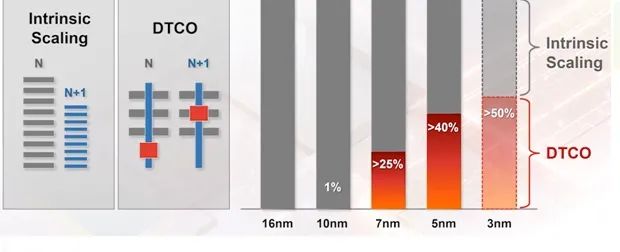

•设计技术协同优化(DTCO)

Mii博士强调了工艺技术开发如何演变为更加重视DTCO,评估工艺复杂性和设计改进之间的权衡已成为工艺开发的一个组成部分。他强调了最近采用的COAG(contact-over-active-gate)和SDB(single diffusion break)步骤作为示例。他补充说:“DTCO的工作不仅限于逻辑设计,存储器和模拟电路也是DTCO评估的关键方面。”

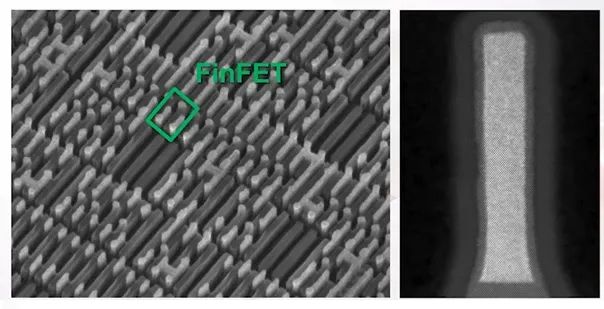

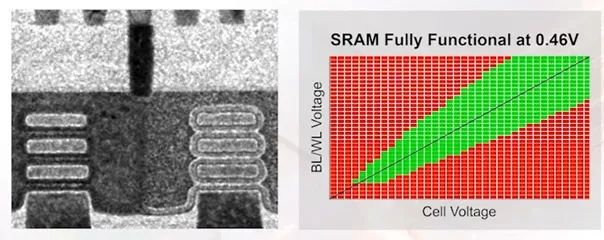

•纳米片(N2节点)

台积电将在N2工艺节点从FinFET过渡到纳米片拓扑结构。

未来半导体技术创新

Mii博士随后介绍了针对未来应用需求的几项半导体技术研发工作。

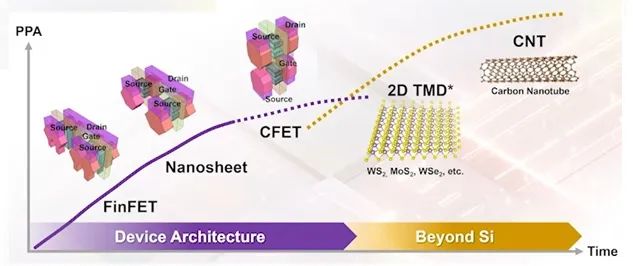

•CFET(和FET互补)

经过几十年的平面FET技术,FinFET也经历了相当长的寿命,从N16/N12到N7/N6到N5/N4再到N3/N3E。看看基于纳米片的工艺节点如何发展将会很有趣。在纳米片之后,Mii博士专注于CFET器件的引入。

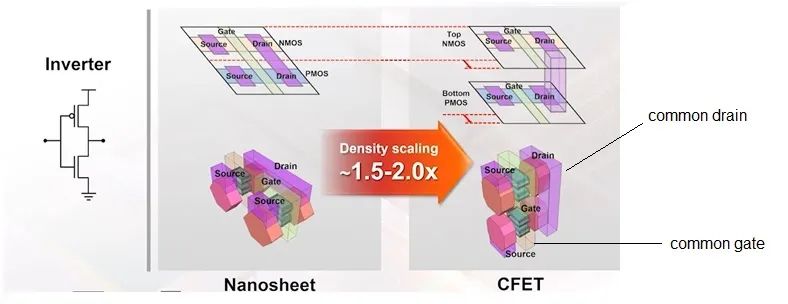

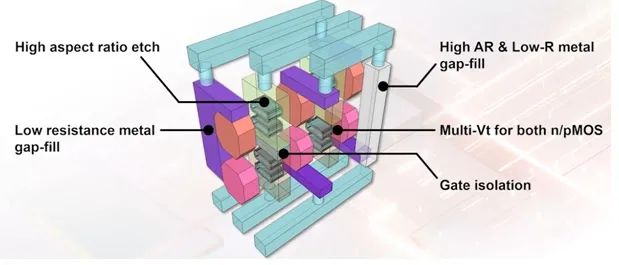

如下图所示,CFET保留了纳米片周围栅极的优点,但垂直制造了pFET和nFET 器件。(图中pFET在底部,nFET在顶部。)

在上述逆变器逻辑门的横截面中,突出显示了两个设备的公共门输入和common drain节点。

下图扩展了CFET器件堆叠所带来的工艺开发挑战,特别是对高纵横比蚀刻和相关金属沟槽填充的需求,以实现上面强调的垂直连接。

注意:研究CFET工艺开发的不同研究人员一直在寻求两条途径:一种“顺序”工艺,其中pFET和nFET器件使用用于顶部器件制造的上部薄基板来实现,该基板在底部器件制造后与起始基板结合,并具有中间介电层;一种“单片”工艺,其中有一组外延层用于基板上的所有器件。这两种方法在工艺复杂度和热预算、器件性能优化(顺序流中有多个基板材料)和成本方面存在权衡。虽然Mii博士没有具体说明,但有关高AR蚀刻和金属填充的评论表明,台积电研发的重点是单片CFET工艺技术。

•二维晶体管材料

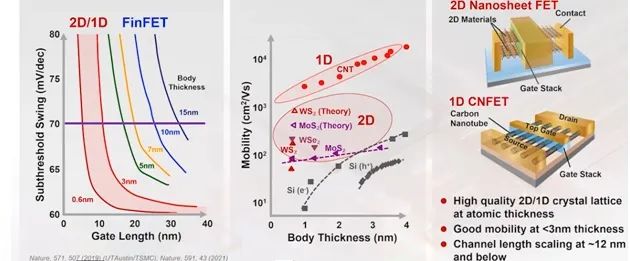

目前正在积极研究评估用于场效应晶体管通道的“后硅”材料。如下所示,随着器件栅极长度和沟道体厚度的减小,2D材料提供了改善载流子迁移率和亚阈值斜率的潜力(具有较低的泄漏电流和较低的VDD操作潜力)。

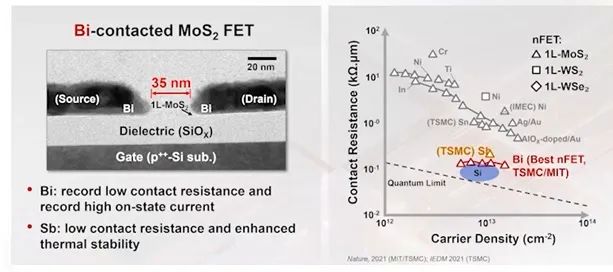

2D工艺开发的主要挑战之一是为器件source/drain节点提供低接触电阻连接。Mii博士分享了TSMC研究人员先前发布的结果,强调了对铋(Bi)和锑(Sb)的评估。与先前发布的研究相比,Rc降低了5倍,如下所示。

•BEOL互连架构

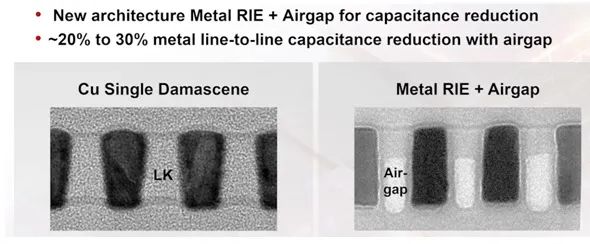

后端互连的扩展面临着现有(镶嵌)铜线效率较低的挑战。镶嵌沟槽中的Cu扩散阻挡层(例如,TaN)和粘附衬垫(例如,Ta)占据了按比例缩放的导线横截面的百分比增加。Cu沉积晶粒尺寸也受到限制,导致更大的电子散射和更高的电阻率。下图突出了台积电为引入一种新的(减法蚀刻)BEOL冶金技术所做的研发工作。

通过减法金属工艺,引入了制造导线间电介质的新机会——上图显示了相邻电介质内的“气隙”横截面。

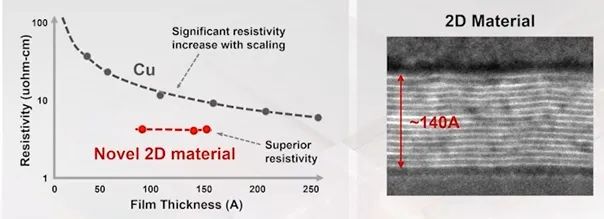

•2D导线

除了取代铜作为上述BEOL互连外,台积电研发部门正在研究2D导体的潜力。

上图显示了2D导体层的横截面,以及与类似铜线厚度相比产生的导电性优势。

(Mii博士没有详细说明正在评估的特定材料。例如,有许多过渡金属化合物在二维晶体拓扑中表现出高载流子迁移率,以及堆叠这些受范德华力约束的层的能力。)

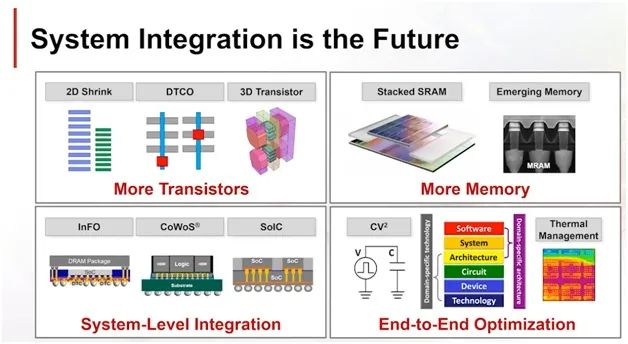

总结

Mii博士以上图所示的幻灯片结束了他的演讲。未来的系统设计将利用:

晶体管密度增加,如CFET器件(和以DTCO为中心的工艺开发)

新型互连材料

在高级封装中增加异构功能的集成,包括2.5D和3D配置中的芯片和HBM堆栈

系统设计分区、物理实现和电/热分析的新方法

无论是作为一名设计师还是一名工艺技术工程师,这都是行业中最激动人心的时刻。

编辑:黄飞

-

全球半导体技术发展新路线图发布2014-05-25 3484

-

嵌入式学习路线图2012-08-20 6463

-

嵌入式学习路线图分享2018-07-13 2924

-

新兴的半导体技术发展趋势2019-07-24 3104

-

未来的DSPIC是否有路线图?2019-08-13 2019

-

物联网学习路线图2020-04-20 3874

-

2007年国际半导体技术发展路线图摘要介绍2009-12-14 1034

-

美国半导体协会副总裁解读国际技术路线图2009-11-19 734

-

探析意法半导体未来功率GaN路线图2018-12-24 6724

-

意法半导体32位汽车单片机技术产品路线图资料合集免费下载2019-05-06 1322

-

IEEE发布半导体技术路线图,助力碳化硅和氮化镓材料发展2020-04-13 5991

-

未来10年传感器怎么发展?美国半导体协会发布最新MEMS路线图2023-11-15 1731

-

纳微半导体发布最新AI数据中心电源技术路线图2024-03-16 2123

-

美国公布3D半导体路线图2024-03-25 1840

-

未来10年智能传感器怎么发展?美国发布最新MEMS路线图2024-11-27 5085

全部0条评论

快来发表一下你的评论吧 !