电子时钟电路图汇总

描述

数字钟是一种用数字电路技术实现时、分、秒计时的钟表。与机械钟相比具有更高的准确性和直观性,具有更长的使用寿命,已得到广泛的使用。

本文介绍了七款数字时钟设计电路图。

1

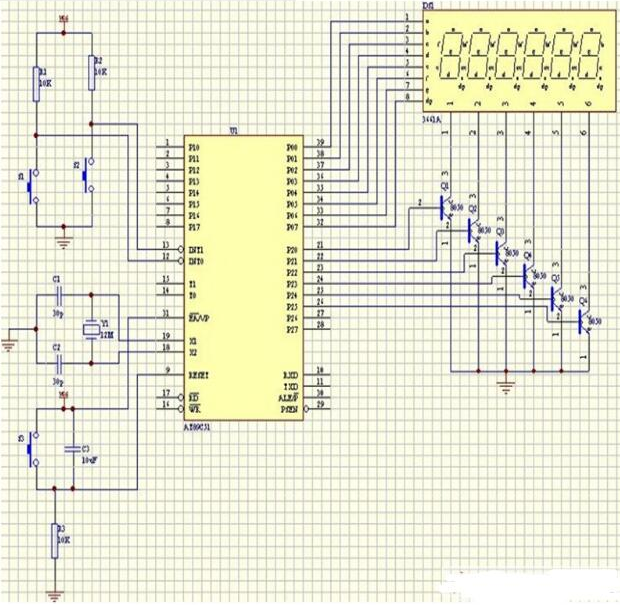

本设计主要采用中断的方式,采用INT0,INT1中断,分别由按键s1,s2触发。按键s1作为功能选择键,当按键s1按下时,可以在不同的功能之间进行切换。

按下s1,由时钟状态进入秒表状态,再按一下,秒表开始计时,再按s1,秒表停下,再按s1,进入调整时钟的状态,每按一次,可以用按键s2对相应的位进行调整。其中复位电路具有上电自动复位,和手动复位功能。由P2控制三极管驱动数码管,P0口做数据输出口。

2

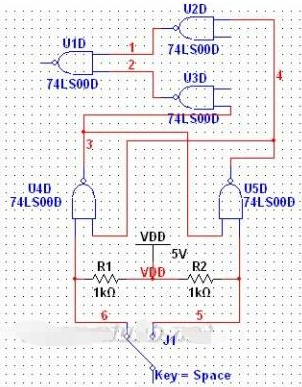

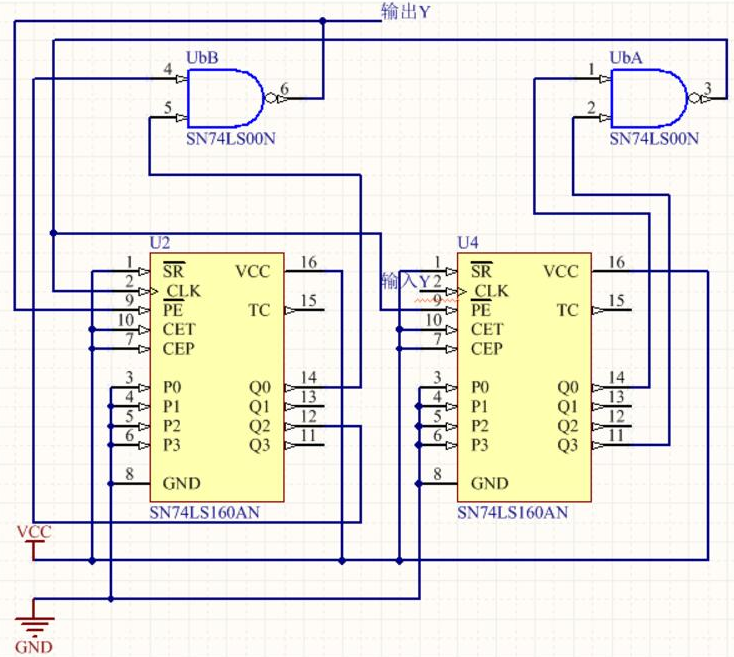

校“时”和校“分”的校准电路是相同的,现以校“分”电路来说明时间的校准。在正常计时时,与非门U2D的一个输入端为1,将它开通,使秒计数器输出的分脉冲加到U2D的另一输入端,并经U1D进入分计数器。而此时U3D由于一个输入端为0,因此被关断,校准用的秒脉冲进不去。

在校“分”时,按下开关J1,情况与上述情况适反。U2D被封闭,U3D打开,标准秒脉冲直接进入分计数器进行快速校“分”。同理,在校“时”时,按下开关,标准秒脉冲直接进入时计数器进行快速校“时”。可见U1D、U2D、U3D构成的是一个二选一电路。

3

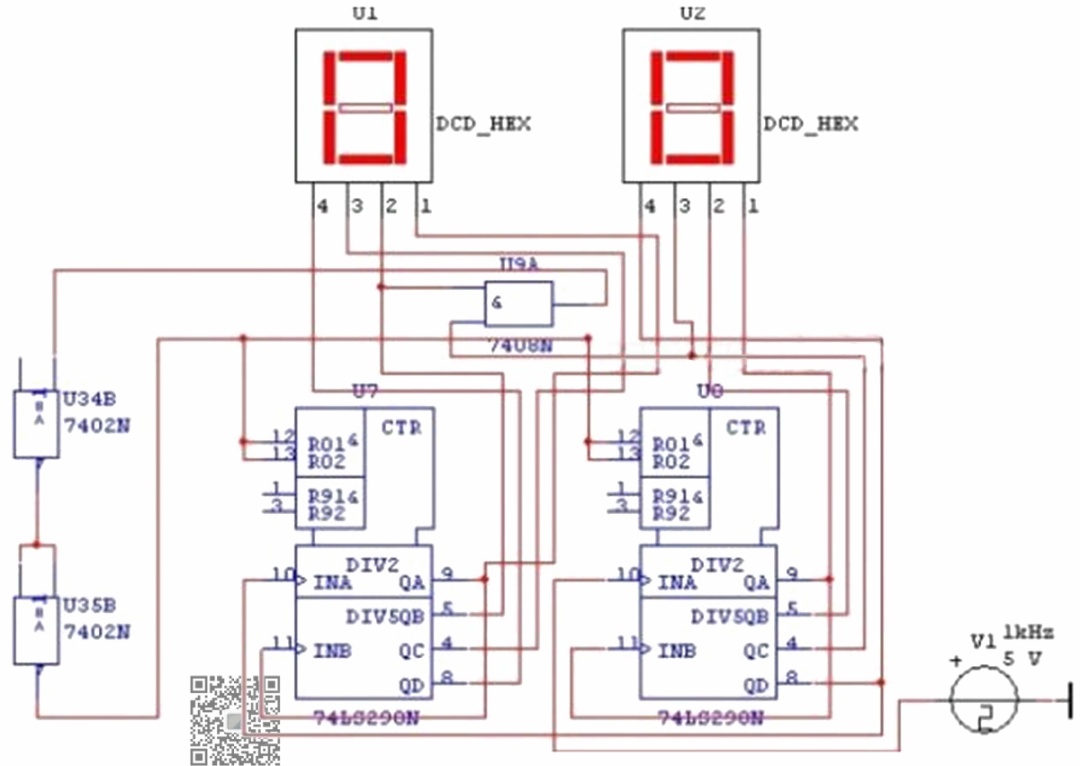

由图可以看出,当“时”个位U8计数输入端到第10个触发信号时,U8计数器复零,进位端QD向U7“时”十位计数器输出进位信号,当第24个“时”(来自“分”计数器输出的进位信号)脉冲到达时,U8计数器的状态为“0100”,U7计数器的状态为“0010”,此时“时”个位计数器的QC和“时”十位计数器的QB输出为“1”。把他们分别送入U7、U8计数器的清零端R01和R02,通过74LS290内部的R01和R02与非 13

4

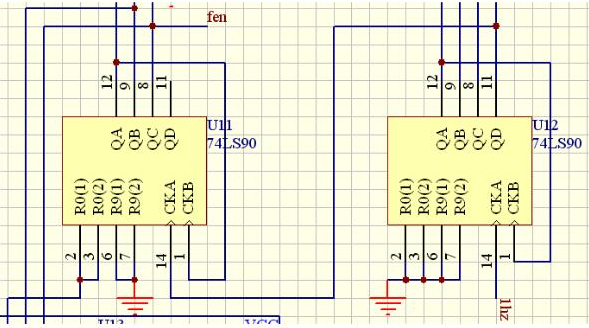

数字钟的计数电路是用两个六十进制计数电路和一个十二进制计数电路实现的,但是考虑到对74LS90比较熟悉,觉得用两个74LS90来分别控制秒和分的十位和个位。个位采用十进制,十位采用六进制就能完美解决六十进制的秒计数。然后再用74ls191和74ls74来分别控制时的个位和十位。

5

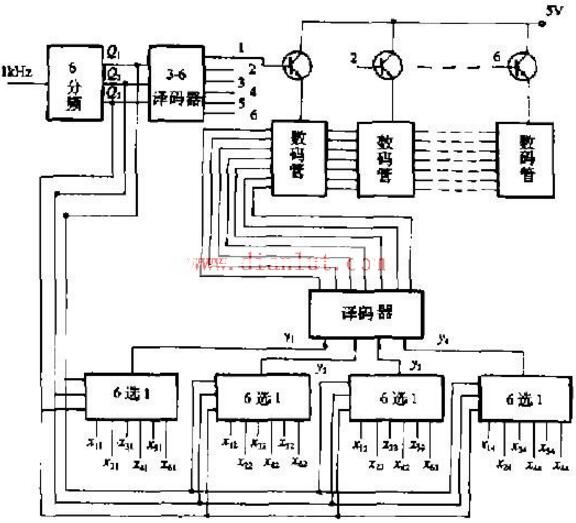

作原理:6个数码管的字型段输入端(a、b、c、d、e、f,g)全部并接到译码器相应的输出端。电源控制开关管分别接到3~6译码器的六个输出端。时钟六个计数器输出端均采用四位,分别为xl、xt£、mx⋯X2nx2z、x2hx2‘,⋯,x、xx、x相应的每一位都接到4个6选1的选择器上,选择器输出共4位接到译码器的输入端(y、y、y、Y上。数码管及与之对应要显示的计数器,由Q]、、的编码(BCD码)进行循环选择例如,当Q、、均为⋯0时,则3~6译码器的输出端1为高电平,第一个数码管加上电源,与此同时,六选一选择器对应的输出分别为Yy—yXs—xX—x。这时译码器的输出a,b,⋯⋯,g虽然接到所有数码管上,但由于只有第一个数码管加上电源,故只有该管点亮,显示第一个计数器的状态(x、x。、xX)。同理,当Q、QQ为001”时,第二个数码管点亮,显示第二个计数器的状态。依此类推,到第六个数码管断后,接着第一个又开始点亮。如此循环显示,循环周期为6ms,给人的感觉,就相当所有数码管都一直在同时加电,实际上每次只有一个,消耗的功率只有静态显示的六分之一。由于数码管电流很大,一般小型管各段全亮时,大约要150mA~200mA采用静电显示,此例中就要大于1A的电流。这对长期工作的时钟很不经济,对于大型数码管会更加严重。此外,采用动态显示,数码管的寿命与静态相比也相应延长Ⅳ倍(本例为6倍)。

6

闹钟由可调时、分显示器,4个74290芯片,3个4077芯片和两个7421芯片的电路构出时钟的多功能部分。其中,四个74290和四个显示器构成定时闹钟的显示部分(调时部分可以由开关3、4直接控制电路与振荡器的连接来实现);4077芯片的作用是比较实际时钟部分与闹钟部分的输出数据是否一致,再由两个7421芯片校验作最后校验,当全部输出对比为真时,则发光二极管亮起来,实现定时闹钟功能。具体电路如下图:

7

位到达9时,接着下一个脉冲来时,将进行秒到分的进位,分实行六十进制后,再进位到时。

审核编辑:汤梓红

-

常用的日常电路图汇总2021-12-06 4551

-

电子时钟电路的单片机代码及protues仿真图2020-12-14 1578

-

使用Protel 99SE实现电子时钟的电路图免费下载2020-11-02 1751

-

使用51单片机实现的电子时钟源代码和电路图及仿真资料合集免费下载2020-03-06 1986

-

电子时钟设计电子时钟程序相关资料下载2017-05-26 1779

-

可调闹钟电子时钟2017-03-05 1616

-

DS1302电子时钟2017-02-15 1246

-

电子时钟设计202016-05-10 980

-

电子时钟设计2016-04-19 1145

-

带闹钟和日历的电子时钟电路图2016-03-09 1335

-

电子时钟2013-05-31 12000

-

带有整点报时和调整时间的电子时钟(新手)2012-11-28 17404

-

求数字电子时钟设计 纯硬件的2011-10-25 5749

-

at89c51电子时钟电路图和程序2007-12-27 14025

全部0条评论

快来发表一下你的评论吧 !