详细讲解一下MaxViaStack DRC的规则

电子说

描述

介绍:

max via stack就是design rule对可以上下堆叠的via(多层via的cut有overlap)的数量有限制,不能超过要求,否则就会报MaxViaStack的DRC。

简单举个例子:比如Tech LEF/tf文件要求是4,那么v1-v2-v3-v4-v5在同一位置overlap就会报DRC。

下面以tech LEF为例详细讲解一下。

LEF里面的约束:

PROPERTYDEFINITIONS

LIBRARY LEF58_MAXVIASTACK STRING

"MAXVIASTACK maxStack [NOSINGLE] [RANGE bottomLayer topLayer] ;" ;

END PROPERTYDEFINITIONS

详细解释:

MAXSTACK指定的是single cut via允许连续堆叠的最大数目,如果超过它就是DRC违反(不考虑multi cut via);

RANGE指定的是检查的最低和最高层,如果不做约束的话默认检查的所有绕线层;

NOSINGLE(可选项),前面的MAXSTACK指定的是single cut via允许连续堆叠的最大数目,是不考虑multi cut的,因此遇到multi cut via的话会认为中间是断开的,而如果指定NOSINGLE的话则认为multi cut via没有打断堆叠,还会算在内。

举例:

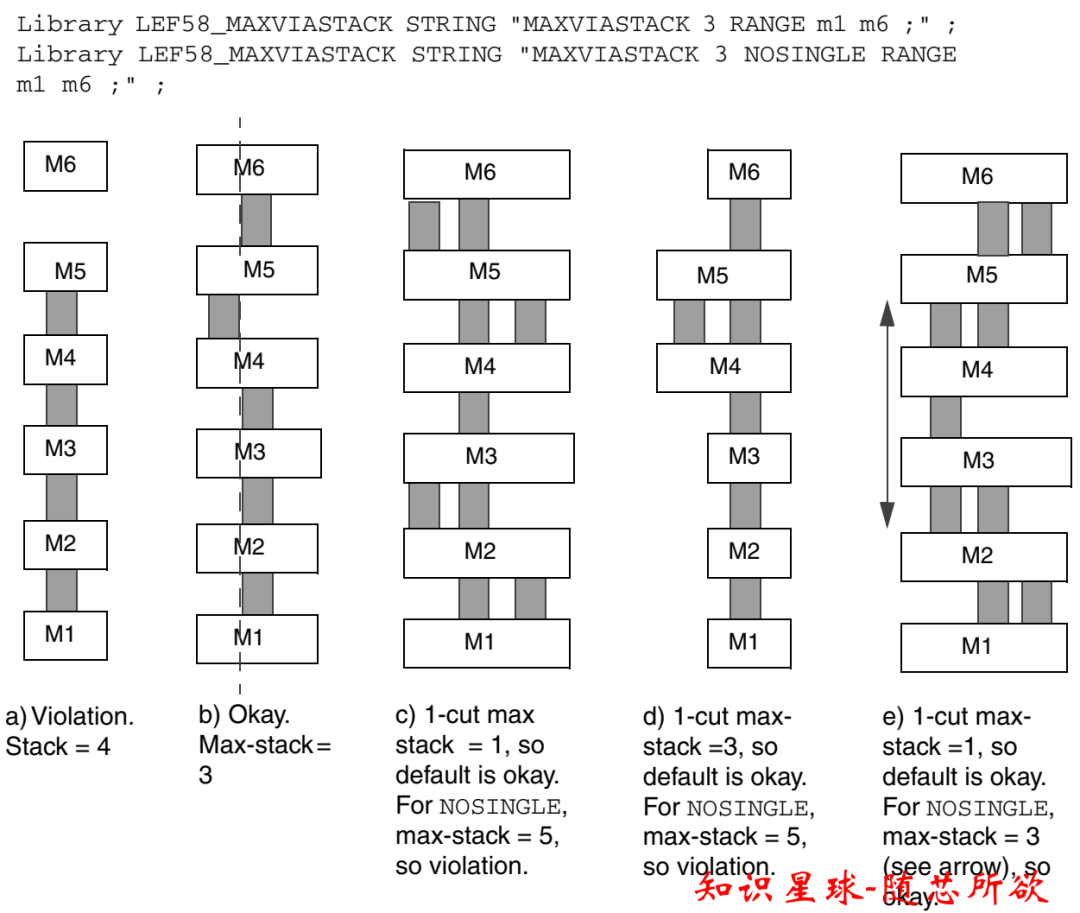

如上图所示,a和b都是只有single via堆叠,a从m1-m5堆叠了4层via,超过了第一行MAXSTACK 3 RANGE m1 m6的约束,b的话只有m1-m3,堆叠了3层via,没有超过要求,所以没有DRC违反。

c, d, e都是有multi cut via的情况,c的话如果只看signle via的话没有超过下面tech LEF第一行的要求,如果同时考虑multi cut via的话,那么M1-M6的via都是有堆叠的,堆叠了5层via,所以违反了第二行MAXSTACK NOSINGLE 3 RANGE m1 m6的要求,会报DRC违反。

后边的d e也是类似。

问题的修复:

知道上面的规则之后,要想解这类问题就非常简单了,只要随便把中间或者某层via错开一段距离,让它们之间没有overlap就可以了。注意检查错开之后堆叠的via的数量是否满足要求。不要出现这种情况:比如DRC要求只允许堆叠3层,现在堆叠了v1-v5,你想修这个问题结果你挪动了v5,那么还是解不了这个DRC的。

审核编辑:刘清

- 相关推荐

- 热点推荐

- DRC

-

和Dr Peter一起学KiCad 4.8:设计规则检查(DRC)2024-12-25 3545

-

芯片后端设计的DRC是什么?2023-12-04 5056

-

DRC规则是指什么?怎样使用DRC规则减少PCB改版次数呢?2023-11-17 11537

-

详细的讲解一下I/O模式下的程序与MM模式下的程序调试2022-02-24 971

-

详细讲解一下农业气象仪器的组成部分2021-08-12 767

-

【直流电机驱动器项目】板框的设置及电气规则的设置详细讲解(第八集)2021-07-01 1722

-

电气设计规则检查工具HyperLynx DRC2019-10-08 14104

-

PCB设计电气规则检查器解决DRC问题2019-05-21 7852

-

求大神讲解一下labview程序2019-05-12 1215

-

Altium显示DRC错误的检查方法2018-09-23 35014

-

能详细讲解一下电阻与电容并联的作用吗?2017-11-15 28544

-

AltiumDesigner的DRC规则参考2016-09-19 1435

-

DRC步骤2016-06-08 1573

-

有没有哪位大神给详细讲解一下5509A的USB固件编程,一直找...2013-08-12 2425

全部0条评论

快来发表一下你的评论吧 !