иҝҗж”ҫз”өи·ҜеҸҢеҸҚйҰҲRisoзЁіе®ҡжҖ§иЎҘеҒҝж–№жі•

жҸҸиҝ°

В В В В В В В В еңЁеүҚйқўжҲ‘们讨и®әдәҶпјҢ第дёҖз§ҚдҪҝз”Ёйҡ”зҰ»з”өйҳ»жқҘиЎҘеҒҝе®№жҖ§иҙҹиҪҪзҡ„ж–№жі•гҖӮиҷҪ然Risoз”өи·Ҝи®ҫи®Ўе’ҢдҪҝз”ЁйғҪиҫғз®ҖеҚ•пјҢдҪҶе®ғеңЁзІҫеҜҶз”өи·ҜйҮҢжңүдёҖеӨ§зјәзӮ№пјҢRisoдёҠзҡ„еҺӢйҷҚдёҺиҫ“еҮәз”өжөҒжҲ–иҫ“еҮәиҙҹиҪҪжңүе…іпјҢ并且RisoйҖ жҲҗзҡ„еҺӢйҷҚеҸҜиғҪеҪұе“Қиҫ“еҮәдҝЎеҸ·зҡ„еҮҶзЎ®еәҰпјҢеҰӮеҸіеӣҫжүҖзӨәеҜ№дәҺдёҖдёӘ10mVзҡ„иҫ“еҮәдҝЎеҸ·з”ұдәҺ250О©зҡ„иҫ“еҮәиҙҹиҪҪпјҢиҖҢдә§з”ҹи¶…иҝҮ3mVзҡ„еҺӢйҷҚд№ҹе°ұжҳҜдјҡеёҰжқҘ30%зҡ„иҜҜе·®гҖӮ

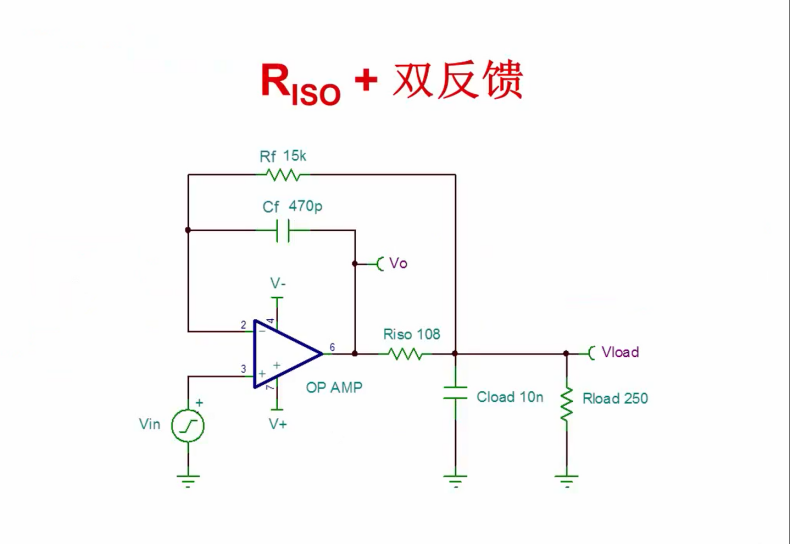

дёәдәҶи§ЈжұәRisoдә§з”ҹеҺӢйҷҚзҡ„й—®йўҳпјҢжҲ‘们еҸҜд»ҘдҪҝз”ЁиҝҷйҮҢжүҖеұ•зӨәзҡ„Riso+еҸҢеҸҚйҰҲзҡ„з”өи·ҜгҖӮ

В В В В В В В В Riso+еҸҢеҸҚйҰҲзҡ„е·ҘдҪңеҺҹзҗҶпјҢеҸҜд»Ҙз”ЁDCе’ҢACзӯүж•Ҳз”өи·ҜжқҘеҲҶжһҗгҖӮеңЁDCж—¶пјҢеҸҚйҰҲз”өе®№CfжҳҜејҖи·Ҝзҡ„пјҢ并且Rfй—ӯеҗҲдәҶеҢ…еҗ«Risoзҡ„еҸҚйҰҲзҺҜи·ҜгҖӮеӣ дёәзҺ°еңЁRisoжҳҜеңЁиҝҗж”ҫзҡ„еҸҚйҰҲзҺҜи·ҜйҮҢйқўзҡ„пјҢиҝҗж”ҫиҫ“еҮәдјҡеўһеӨ§жқҘиЎҘеҒҝRisoзҡ„еҺӢйҷҚпјҢжүҖд»ҘиҙҹиҪҪз”өеҺӢVloadдјҡзӯүдәҺVinгҖӮ

В В В В В В В В еңЁACйў‘зҺҮж—¶CfжҳҜзҹӯи·Ҝзҡ„пјҢеҪ“иҝҷдёӘеҸ‘з”ҹж—¶RfеҸҜд»Ҙиў«и®ӨдёәжҳҜејҖи·Ҝзҡ„пјҢеӣ дёәCfзҡ„йҳ»жҠ—Zcfдјҡиҝңиҝңе°ҸдәҺRfзҡ„йҳ»жҠ—пјҢеӣ жӯӨеңЁACж—¶пјҢиҝҷдёӘз”өи·ҜзңӢиө·жқҘдјҡе’Ңж ҮеҮҶзҡ„Risoз”өи·ҜдёҖж ·гҖӮ

В В В В В В В В иҝҷдёӘз”өи·Ҝзҡ„第дёҖдёӘи®ҫи®ЎжӯҘйӘӨпјҢжҳҜйҖүжӢ©RisoпјҢйҖүжӢ©ж–№жі•дёҺжҲ‘们д№ӢеүҚжүҖиҜҙзҡ„ж–№жі•1пјҢRisoдёӯйҖүжӢ©Risoзҡ„ж–№жі•зӣёеҗҢгҖӮдҪҝеҫ—AolжӣІзәҝдёҠзӯүдәҺ20dBзҡ„йў‘зҺҮзӮ№дёҠдә§з”ҹдёҖдёӘйӣ¶зӮ№гҖӮ然еҗҺRfеҸҜд»ҘйҖүжӢ©дёәд»»ж„ҸдёҖдёӘеӨ§дәҺ100*Risoзҡ„еҖјпјҢд»ҘйҳІжӯўе…¶дёҺRisoзӣёдә’дҪңз”ЁгҖӮжңҖеҗҺдёҖжӯҘжҳҜеңЁеӣҫзүҮе·ҰдёӢж–№жүҖзӨәзҡ„пјҢиҢғеӣҙеҶ…йҖүжӢ©Cfзҡ„еҖјпјҢдҪҝз”ЁиҝҷдёӘиҢғеӣҙеҶ…зҡ„еҖјпјҢеҸҜд»ҘдҝқиҜҒдёӨдёӘеҸҚйҰҲи·Ҝеҫ„Rfе’ҢCfж°ёиҝңдёҚдјҡдә§з”ҹи°җжҢҜиҖҢеҜјиҮҙдёҚзЁіе®ҡгҖӮжӣҙе°Ҹзҡ„CfеҖјдјҡжңүжӣҙеҝ«зҡ„е»әз«Ӣж—¶й—ҙsettlingtimeпјҢдҪҶд»ҘдёҖе®ҡиҙҹиҪҪиҢғеӣҙеҶ…зҡ„иҝҮеҶІдёәд»Јд»·гҖӮ

В В В В В В В В д»Һз»“жһңеҸҜи§ҒпјҢиҝҗж”ҫиҫ“еҮәе’ҢиҙҹиҪҪз”өеҺӢеҲ°иҫҫзЁіе®ҡеҖјпјҢиҖҢжІЎжңүиҝҮеӨ§зҡ„иҝҮеҶІдёҺжҢҜй“ғпјҢиҜҙжҳҺиҝҷжҳҜдёҖдёӘзЁіе®ҡзҡ„зі»з»ҹпјҢдёәе…ӢжңҚRisoеҺӢйҷҚиҖҢеўһеӨ§зҡ„VoеңЁиҝҷйҮҢд№ҹеҸҜд»Ҙжё…жҘҡең°зңӢеҲ°гҖӮ

В В В В В В В В еҪ“Riso+еҸҢеҸҚйҰҲз”өи·Ҝи§ЈеҶіRisoз”өи·ҜDCзІҫеәҰй—®йўҳзҡ„еҗҢж—¶пјҢе®ғд№ҹеёҰжқҘдёҖдәӣзјәзӮ№гҖӮеҰӮиҝҷйҮҢжүҖзӨәпјҢдёҖдёӘRisoз”өи·ҜеңЁеҗҲзҗҶзҡ„еӨ§иҢғеӣҙе®№жҖ§иҙҹиҪҪзҡ„зһ¬жҖҒе“Қеә”еҸҳеҢ–дёӢпјҢйҖҡеёёдјҡдҝқжҢҒзЁіе®ҡгҖӮRiso+еҸҢеҸҚйҰҲз”өи·ҜеҜ№иҫ“еҮәз”өе®№зҡ„еҸҳеҢ–е®№еҝҚеәҰжІЎжңүйӮЈд№ҲеӨ§пјҢз”өи·Ҝжҳ“еҸ—еҲ°е®№жҖ§иҙҹиҪҪзҡ„еҸҳеҢ–иҖҢеҸҳеҫ—дёҚзЁіе®ҡгҖӮеӣ жӯӨRiso+еҸҢеҸҚйҰҲз”өи·ҜйҖӮз”ЁдәҺиҫ“еҮәз”өе®№зЎ®е®ҡпјҢ并且дёҚдјҡжҳҫи‘—еҸҳеҢ–зҡ„еңәеҗҲгҖӮRiso+еҸҢеҸҚйҰҲж–№жі•йҖҡеёёдјҡеҜјиҮҙе»әз«Ӣж—¶й—ҙжҜ”Risoз”өи·Ҝжӣҙж…ўгҖӮ

В В В В В В В В еҪ“Riso+еҸҢеҸҚйҰҲз”өи·Ҝи§ЈеҶіRisoз”өи·ҜDCзІҫеәҰй—®йўҳзҡ„еҗҢж—¶пјҢе®ғд№ҹеёҰжқҘдёҖдәӣзјәзӮ№гҖӮеҰӮиҝҷйҮҢжүҖзӨәпјҢдёҖдёӘRisoз”өи·ҜеңЁеҗҲзҗҶзҡ„еӨ§иҢғеӣҙе®№жҖ§иҙҹиҪҪзҡ„зһ¬жҖҒе“Қеә”еҸҳеҢ–дёӢпјҢйҖҡеёёдјҡдҝқжҢҒзЁіе®ҡгҖӮRiso+еҸҢеҸҚйҰҲз”өи·ҜеҜ№иҫ“еҮәз”өе®№зҡ„еҸҳеҢ–е®№еҝҚеәҰжІЎжңүйӮЈд№ҲеӨ§пјҢз”өи·Ҝжҳ“еҸ—еҲ°е®№жҖ§иҙҹиҪҪзҡ„еҸҳеҢ–иҖҢеҸҳеҫ—дёҚзЁіе®ҡгҖӮеӣ жӯӨRiso+еҸҢеҸҚйҰҲз”өи·ҜйҖӮз”ЁдәҺиҫ“еҮәз”өе®№зЎ®е®ҡпјҢ并且дёҚдјҡжҳҫи‘—еҸҳеҢ–зҡ„еңәеҗҲгҖӮRiso+еҸҢеҸҚйҰҲж–№жі•йҖҡеёёдјҡеҜјиҮҙе»әз«Ӣж—¶й—ҙжҜ”Risoз”өи·Ҝжӣҙж…ўгҖӮ

еҺҹж–Үж Үйўҳпјҡиҝҗж”ҫз”өи·ҜеҸҢеҸҚйҰҲRisoзЁіе®ҡжҖ§иЎҘеҒҝж–№жі•

ж–Үз« еҮәеӨ„пјҡгҖҗеҫ®дҝЎе…¬дј—еҸ·пјҡ硬件дёүдәәиЎҢгҖ‘ж¬ўиҝҺж·»еҠ е…іжіЁпјҒж–Үз« иҪ¬иҪҪиҜ·жіЁжҳҺеҮәеӨ„гҖӮ

- зӣёе…іжҺЁиҚҗ

- зғӯзӮ№жҺЁиҚҗ

- з

-

иҝҗж”ҫзЁіе®ҡжҖ§зҡ„еҲӨж–ӯеҺҹзҗҶзҡ„иЎҘеҒҝеҺҹзҗҶпјҹ2024-05-06 2044

-

иҝҗж”ҫз”өи·Ҝй—ӯзҺҜзЁіе®ҡжҖ§зҡ„еҲӨж–ӯж–№жі•2023-11-06 3367

-

иҝҗж”ҫзі»з»ҹзЁіе®ҡжҖ§еҺҹзҗҶ иҝҗж”ҫзҡ„йў‘зҺҮиЎҘеҒҝ2023-10-25 2149

-

гҖҠиҝҗж”ҫз”өи·ҜзҺҜи·ҜзЁіе®ҡжҖ§и®ҫи®Ў еҺҹзҗҶеҲҶжһҗгҖҒд»ҝзңҹи®Ўз®—гҖҒж ·жңәжөӢиҜ•гҖӢ+зҗҶи®әдёҺе®һйҷ…з»“еҗҲеҠ ж·ұзҗҶи§Је’Ңе®һжҲҳиҝҗз”Ё2023-05-22 1636

-

иҝҗж”ҫз”өи·ҜеҚ•еҸҚйҰҲRiso зЁіе®ҡжҖ§иЎҘеҒҝж–№жі•2022-12-27 3477

-

иҝҗж”ҫз”өи·Ҝзҡ„зЁіе®ҡжҖ§еҸ—е“Әз§Қиҫ“е…Ҙз”өе®№зҡ„еҪұе“Қ2021-11-19 4274

-

еҰӮдҪ•еҲ©з”ЁRISOеҸҠCLиЎҘеҒҝзЁіе®ҡй©ұеҠЁе®№жҖ§иҙҹиҪҪзҡ„иҝҗз®—ж”ҫеӨ§еҷЁпјҹ2021-04-13 2322

-

иҝҗж”ҫз”өи·Ҝзҡ„зЁіе®ҡжҖ§еҲҶжһҗ2021-04-06 2235

-

еҒҡеҲ°иҝҷдёүжӯҘпјҢиҪ»жқҫе®һзҺ°иҝҗж”ҫз”өи·ҜзЁіе®ҡжҖ§2020-10-09 3174

-

иө„ж·ұе·ҘзЁӢеёҲж•ҷдҪ пјҢиҪ»жқҫе®һзҺ°иҝҗж”ҫиҙҹеҸҚйҰҲз”өи·ҜзЁіе®ҡжҖ§2020-10-03 3271

-

еҒҡеҲ°иҝҷдёүжӯҘпјҢе®һзҺ°иҝҗж”ҫз”өи·ҜзЁіе®ҡжҖ§дёҚжҳҜйҡҫйўҳ2020-04-07 4985

-

иҝҗж”ҫз”өи·ҜзЁіе®ҡжҖ§пјҢиҝҷзҜҮз»ҷдҪ и®Іе…ЁдәҶпјҒ2020-03-12 8177

-

иҙҹеҸҚйҰҲж”ҫеӨ§з”өи·ҜзЁіе®ҡжҖ§зҡ„д»Ӣз»Қ2017-11-22 1276

е…ЁйғЁ0жқЎиҜ„и®ә

еҝ«жқҘеҸ‘иЎЁдёҖдёӢдҪ зҡ„иҜ„и®әеҗ§ !