最新电源转换拓扑中的SiC FET

电子说

描述

(来源:UnitedSiC(现为 Qorvo))

从历史上看,存在从 AC 到 DC 和 DC 到 DC 的首选电源转换方法。这些都是由随着时间演变的各种限制条件设定的。例如,有一天,“功率因数校正”仅在交流配电中实施,交流/直流电源的 PF 可以达到 0.6 甚至更低。法定限制于 1982 年左右在欧洲出现。因此,某些设备(例如额定功率超过 75W 的电源,但在照明等某些应用中较低)需要“电源谐波抑制”(更准确地说)。这实际上涉及到为每个 AC/DC 添加另一个“升压”功率转换级,这让制造商感到懊恼,尽管它确实启用了其他功能,例如通用输入和长穿越时间。第一个电路涉及输入电感器、开关和整流二极管,效率不高。同样,超过 100W 左右的 AC/DC 中的 DC/DC 转换级开始时是半桥或全桥形式的简单正向转换器——相对容易理解和实施,但由于可用的半导体技术和拓扑的“硬切换”性质。

性能规范,例如 2004 年左右的80 PLUS™ 认证计划,已经使这些基本的 PFC 和 DC/DC 转换拓扑无法满足所需的效率水平:例如,最高的“钛”级需要在 50 时达到 96% 的效率230VAC 设备的负载百分比。因此,新技术得到了发展,如今,一种流行的组合(可高达几千瓦)用于实现高功率密度和效率,是“图腾柱 PFC”(TPPFC) 级后接谐振“CLLC”转换器。

图腾柱 PFC 阶段

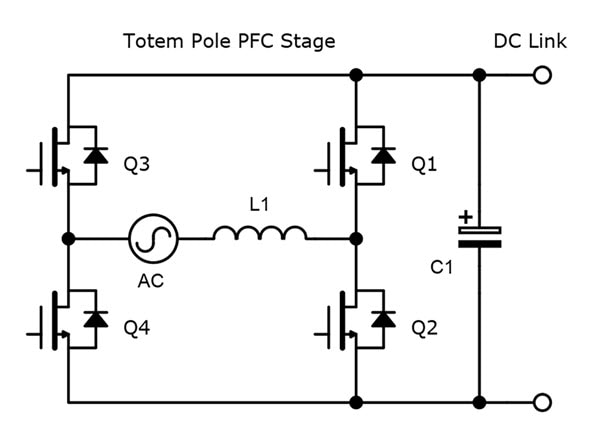

TPPFC 通过使用半导体开关作为同步整流器,有效地消除了 AC/DC 前端中的输入桥式整流器(图 1)。在中高功率下,电路以“连续导通模式”运行,以保持峰值电流可控,从而实现“硬开关”。

图 1:该图说明了“图腾柱 PFC”阶段。(来源:UnitedSiC)

在一个电源极性上,Q1 充当二极管,Q2 充当高频升压开关,在另一个极性上,功能互换。Q3 和 Q4 充当同步二极管,为交流线路电流提供返回电源的路径,并且可以是成本较低的分立二极管。很明显,电源路径中只有开关,此处显示为 SiC FET,因此传导损耗仅由器件导通电阻设置。如果将 Si-MOSFET 用于 Q1 和 Q2,则其体二极管的反向恢复(在死区时间内导通)将限制可实现的效率。然而,在这些位置使用SiC FET,例如最新的750V Gen 4 18mΩUnitedSiC(现为 Qorvo)的部件,在 6.6kW 输出下可实现 99.3% 的半导体效率,开关频率为 75kHz,Q1 和 Q2 各损失 8.3W。这是由于它们市场领先的导通电阻和极低的恢复损耗。

CLLC DC/DC 转换器

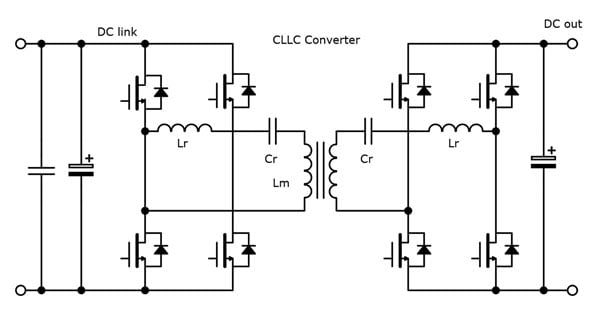

以 96% 的总体效率为目标,TPPFC 阶段是一个良好的开端。对于主 DC/DC 隔离级,可以利用流行的“CLLC”类型的谐振转换器的优势(图 2)。

图 2:该图说明了 CLLC 转换器。(来源:UnitedSiC)

CLLC 是一个可变频率转换器,每个开关具有 50% 的占空比驱动并且是对称的,因此它可以用于双向转换。该拓扑是谐振的,因此可以实现初级零电压开关和次级零电流零电压开关。在谐振转换器中,开关损耗非常低并且体二极管恢复不是问题,因此可以提高频率以最小化磁性尺寸。然而,受器件输出电容的影响,这有一个限制,它决定了最小“死区”时间和工作范围。同样,SiC FET 是一个理想的选择,它具有市场上高温和低温下特定输出电容和导通电阻的最佳品质因数,以及非常低的体二极管正向压降,从而产生出色的效率。例如,在 300kHz、6.6kW 下,与示例 PFC 级中使用的相同 UnitedSiC Gen 4 部件可产生 99.8% 的半导体效率。SiC FET 的另一个好处是它们易于进行 0-12V 栅极驱动。

UnitedSiC 开发了一系列具有可选封装和导通电阻的 750V Gen 4 SiC FET 部件,因此设计人员可以根据自己的性能目标和预算进行广泛的选择。可以使用公司的在线 FET-Jet Calculator™ 探索所有选项,该计算器提供 SiC FET 在广泛的可选拓扑结构(包括 TPPFC 和 CLLC)中的瞬时性能结果。显示功耗、温升和组件应力水平,用户能够指定电气和热操作条件以及并联多个部件的影响。

我们现在有最终的拓扑结构和开关吗?现在阶段效率与 100% 的差距只有百分之几,我们已经非常接近了。

审核编辑:汤梓红

-

充分挖掘SiC FET的性能2023-12-07 881

-

UnitedSiC SiC FET用户指南2023-12-06 1122

-

SiC FET神应用,在各种领域提高功率转换效率2023-11-30 862

-

还没使用SiC FET?快来看看本文,秒懂SiC FET性能和优势!2023-11-29 1357

-

联合SiC的FET-Jet计算器 — — 从SIC FET选择中得出猜算结果2023-09-27 1163

-

充分挖掘 SiC FET 的性能2023-02-08 1006

-

OBC 充电器中的 SiC FET2022-12-28 1802

-

SiC FET性能和优势及起源和发展介绍2022-11-11 2331

-

SiC FET器件的特征2022-10-31 1567

-

UnitedSiC推出业界最佳6mΩ SiC FET2021-09-14 1062

-

UnitedSiC SiC FET用户手册2021-09-07 629

-

SiC MOSFET在电源转换器设计中的优化方案2021-03-25 2893

-

开关电源转换器中如何充分利用SiC器件的性能优势?2021-02-22 1563

-

GaN FET重新定义电源电路设计2017-05-03 5023

全部0条评论

快来发表一下你的评论吧 !