如何利用ZedBoard+AD9361的硬件板卡套装产生点频信号呢

描述

Matlab操作ZedBoard+AD9361产生信号

之前我们基于matlab板级支持包在matlab的控制下,利用ZedBoard+AD9361的硬件板卡套装产生了点频信号。

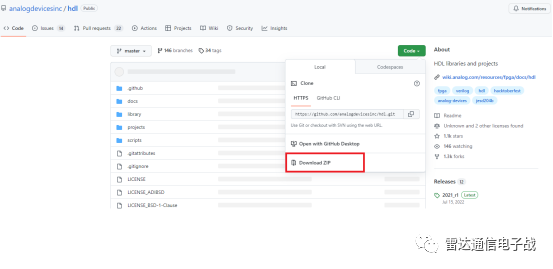

今天我们使用ADI在github上提供的HDL源码来构建zedboard+AD9361的vivado工程。

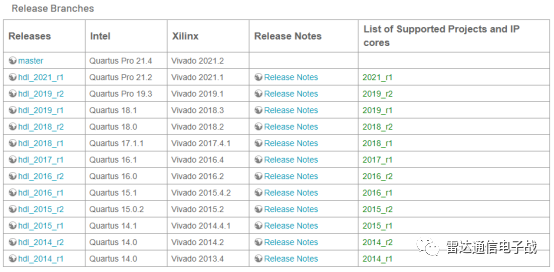

根据你vivado的版本选择对应的内容下载,我们使用的是vivado2021.2,直接下载master即可。

解压所下载的文件,使用“.../hdl-master/projects/fmcomms2/zed”文件路径下的system_project.tcl文件来构建工程。

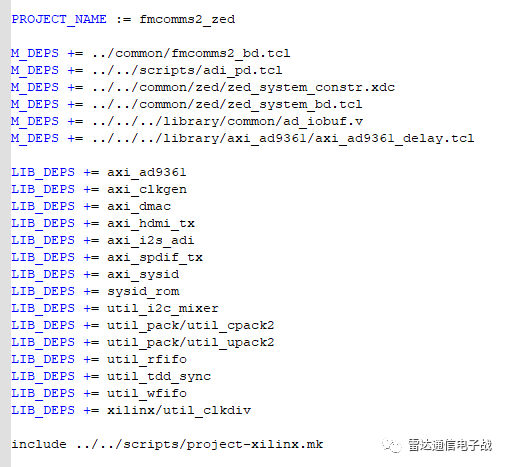

但是在构建工程之前,需要先编译库文件,具体需要编译哪些库可以通过打开该路径下的Makefile查看:

打开vivado,在tcl命令框内输入cd d:/hdl-master/library/axi_ad9361,然后再运行 source ./axi_ad9361_ip.tcl,或者点击“tools”->“run tcl script”找到axi_ad9361_ip.tcl进行编译库文件,等待编译完成。 接着继续用同样的方法编译Makefile中列出的其他IP,所有IP编译完成后执行: cd d:/hdl-master/projects/fmcomms2/zed, 然后运行source ./system_project.tcl开始编译生成vivado工程。

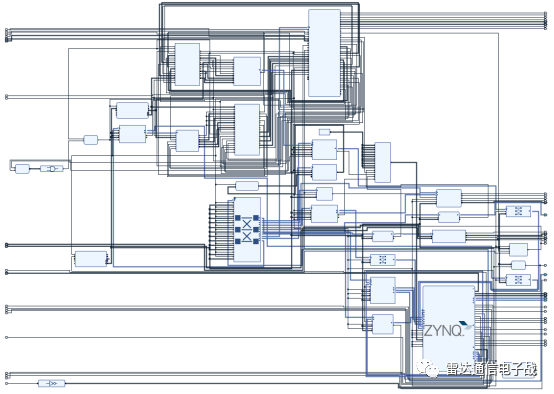

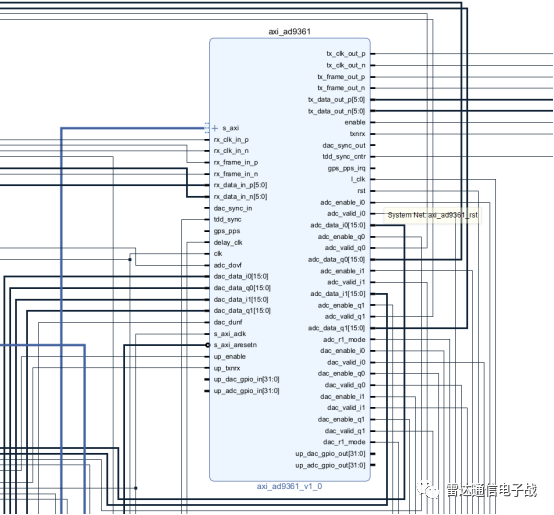

放大看一下AD9361核的连线:

在构建工程的过程中需要注意的地方:

1,HDL源码下载的版本需要与你安装的vivado版本一致。

2,其中用到的路径需要和你放文件的路径一致,并且需要注意路径中斜杠的方向,与电脑复制的路径斜杠方向不一样;

3,若在构建时报错,可以查看log看那里出错,很大可能是还有哪些IP没有编译。

4,若你想生成更高版本的vivado工程,可以先构建完成后再升版本。

审核编辑:刘清

-

扫频信号 DAQ 4431板卡2016-12-12 2845

-

proteus能产生双频信号或者多频信号吗?2017-05-20 2174

-

[AD9361][Zedboard]如何透過matlab讀寫AD9361的Register Value?2018-08-29 2690

-

AD9361发射单频信号接收到的信号存在明显的谐波2018-09-04 5294

-

AD9361射频FMC板卡2018-09-11 8400

-

AD9361无发射信号2018-09-25 3830

-

AD9910产生点频信号锁相环不能锁定2018-11-07 2557

-

怎么产生的高频信号?2018-11-08 6278

-

AD9361发送调试没有找到1M正弦波的信号?2019-01-11 3179

-

AD9361信号输出的问题2019-07-31 8065

-

AD9361 BIST模式2019-11-17 9946

-

利用定时/计数器产生音频信号的方法2021-12-03 1371

-

自动产生点和划的电码练习振荡器电路图2009-03-21 1365

-

基于Zedboard FPGA的VGA图像信号采集系统的设计2017-11-18 2657

-

为什么高频信号不能直接通过电阻的分压来实现信号的衰减呢?2023-10-20 4553

全部0条评论

快来发表一下你的评论吧 !