如何突破EDA封锁 卷起来的阈值电压

EDA/IC设计

描述

2022年,集成电路半导体行业最热的头条是“EDA被全面封锁”。如何突破EDA封锁,成为行业发展的关键词,也是群体焦虑。在全球市场,有人比喻EDA是“芯片之母”,如果没有了芯片,工业发展和社会进步将处处受制,EDA的重要性也上升到了战略性高度。尽管国际封锁形势严峻,但睿智的中国科技人擅于把危机化为机会,从《加快自动研发应用,让工业软件不再卡脖子》,到《破解科技卡脖子要打好三张牌》,即一要打好“基础牌”,提升基础创新能力;二要打好“应用牌”,加强对高精尖国货的应用;三是要打好“人才牌”,让人才留得住、用得上、有发展……,各种政策、举措和实际行动,处处彰显了我们中国科技的发展韧性。

上次我们回顾了器件在“亚阈值”的行为。关于阈值电压本身,有一个非常重要的行为叫做 Vt roll-off。

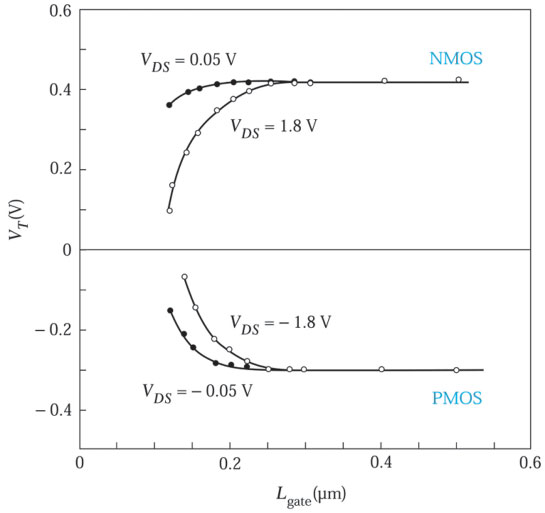

图:Vt roll-off 示意图。引自S.Sze Semiconductor Devices Physics and Technology

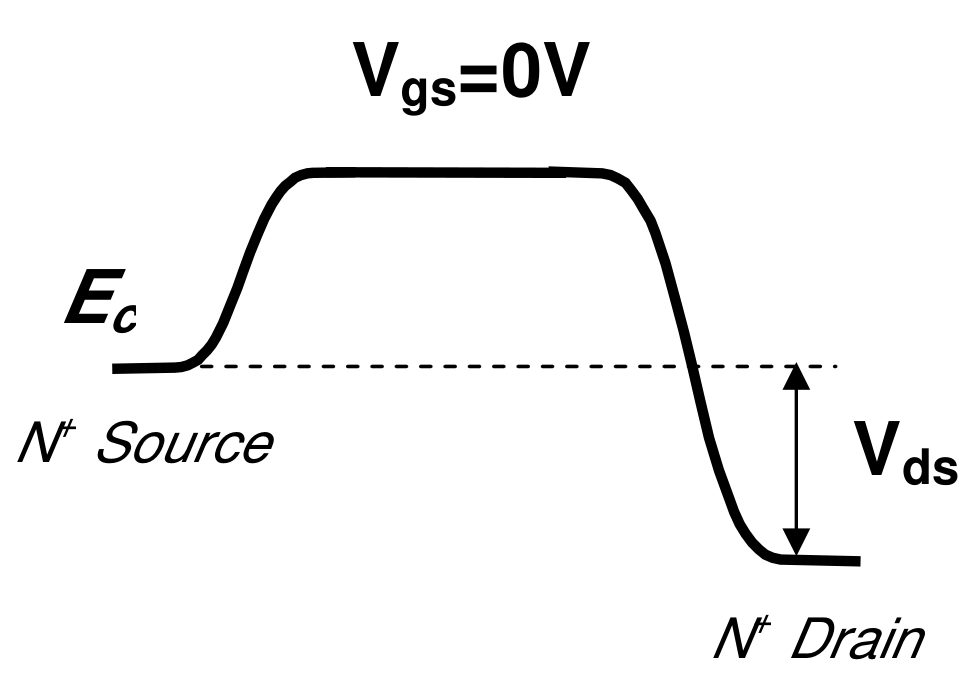

Vt roll-off核心是(同一个工艺节点下面)阈值电压与栅长之间的关系。当沟道长度比较长的时候,Vt值是比较稳定的。随着沟道长度的减小,阈值电压会下降(对于PMOS而言是绝对值的下降)。结合上周我们讨论的,由于Swing的限制,当阈值电压不够高时。Ion与Ioff比将会变得不可接受。 至于要探究为何阈值电压会随着沟道长度的变化而变化,这就需要请出我们第一篇介绍的能带结构。 如下图所示,这是一个长沟道器件的导带底示意图。左端是源极,右端是漏极,中间是沟道。

长沟道器件栅压为零时导带示意

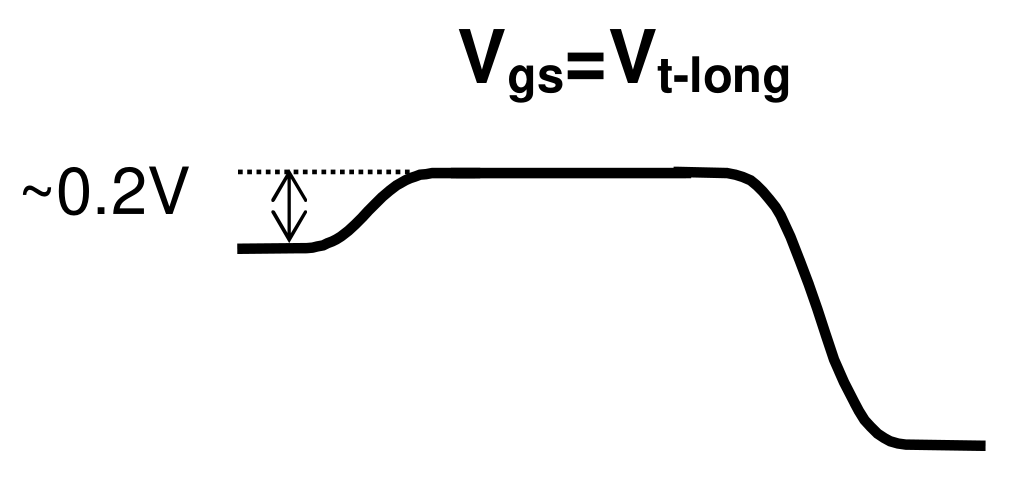

尽管漏极的位置更低,但由于沟道势垒的存在,在源极的电子没有办法自然流到漏极中去。而被拦在沟道之外。 而当栅极施加的电压达到阈值电压时,沟道与源极之间的势垒大大降低了,这使得相当一部分在源极的电子可以跃上这个势垒,并且顺势流到沟道处。这便是我们看到的MOS管开始导通。

长沟道器件栅压在Vt时导带示意

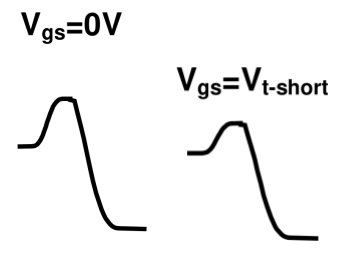

事实上,漏极处电势的“斜坡”会影响到沟道区。当沟道比较长的时候,有足够的缓冲区来容纳这个“斜坡”,最终过度到自然的能带位置 。而当沟道比较短时,还不足以释放漏极的效应,便又遇到了源极。这样带来的结果便是,短沟道器件的沟道势垒要比长沟道的低。

短沟道器件导带示意 自然而然地,在栅极上施加一个小得多的电压,便足以让电子流到漏极。表现在roll-off曲线上,就是从某个临界点开始,沟道越短,Vt越低。 从物理的角度来看,Vt Roll-off是不可避免的,因为这是MOS结构本身的特征,但是从器件特性的角度,必须要认识,控制Vt Roll-off以保证器件可以达到设计的性能。

出于这个目的,我们可以进一步地分解器件结构。

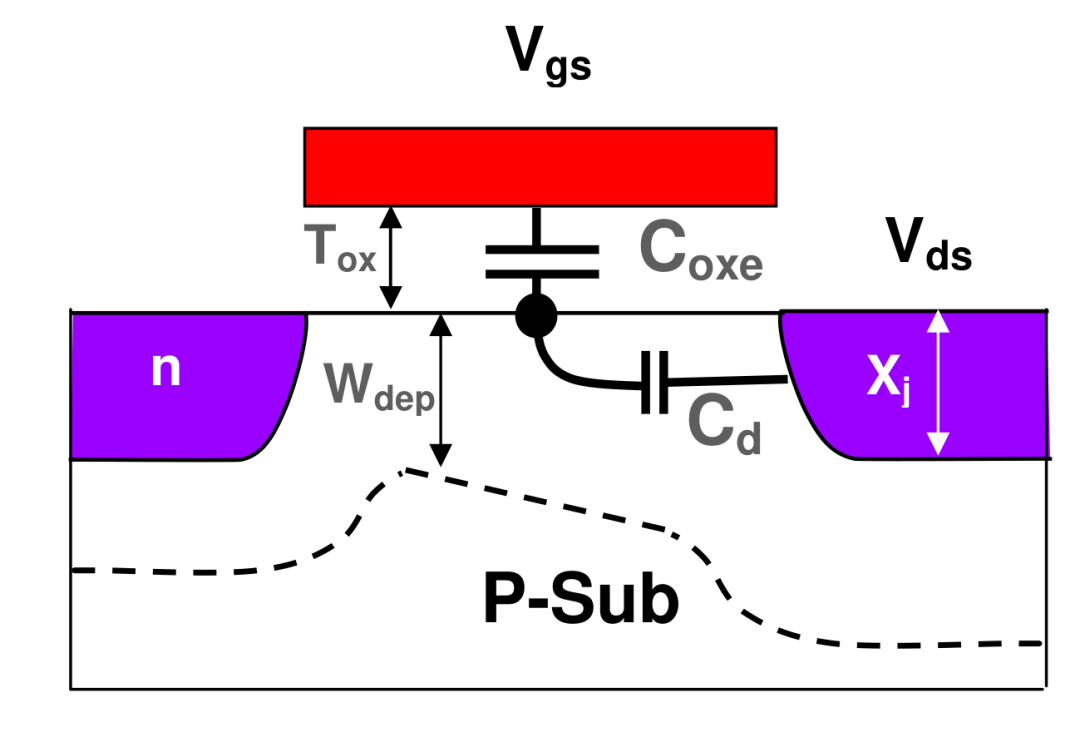

图:MOS器件Vt影响示意图。引自 Chenming Hu Modern Semiconductor Device for Integrated Circuits

在上图当中,核心参数是两个电压:漏极电压Vds,栅极电压Vgs。和两个电容:栅介质电容Coxe,沟道与漏极等效综合电容Cd。

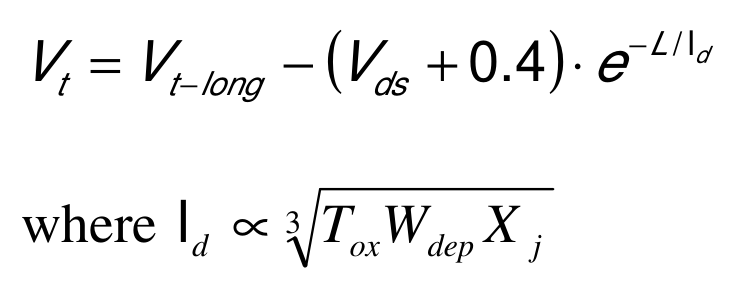

可以明显看出在这个电容串联结构当中,沟道处的电势是由两个电压两个电容共同决定的。当沟道很长时,Cd很小,Vds对于沟道电势的影响很小。而随着沟道尺寸减小,漏极越来越近。Cd越来越大,Vds则会明显干涉到沟道处的电势。即更小的Vgs也足以打开沟道的反型层开关,即阈值电压减小。 经过一系列近似和推导,我们可以得到以下关系:

当L远远大于Id时,减号后面的一项趋于零。即是岁月静好的长沟道模型。阈值电压表示静静地躺平。当L与Id可以比拟时,阈值电压开始“卷”了起来。而当L比Id还要小时,阈值电压失控,整个晶体管无法关断,失去功能。 从器件设计的角度,我们必须要保证L大于几倍的Id,才能得到可以使用的晶体管。而对Id进行分解,它与栅介质厚度,耗尽层宽度和结深正相关。因此当设计更高密度的器件时,我们不仅要把横向的沟道长度缩短,在纵向上,还需要更小的栅介质层和更浅的结深。

编辑:黄飞

-

MOSFET栅极阈值电压Vth2025-12-16 213

-

MOS管的阈值电压是什么2024-10-29 8572

-

MOSFET阈值电压是什么?影响MOSFET阈值电压的因素有哪些?2024-07-23 26108

-

浅谈影响MOSFET阈值电压的因素2024-05-30 7285

-

什么是MOS管亚阈值电压?MOSFET中的阈值电压是如何产生的?2024-03-27 8011

-

IGBT中的MOS器件电压、电流与阈值电压之间的关系2023-11-29 5502

-

影响MOSFET阈值电压的因素2023-09-17 17333

-

NMOS晶体管的阈值电压公式 nmos晶体管的阈值电压与哪些因素有关2023-02-11 19412

-

EDA探索之控制阈值电压2023-02-09 2554

-

三星的OLED柔性屏曝光可以像幕布一样卷起来2019-01-07 3319

-

MOS管阈值电压的问题2018-11-15 14193

-

解答74HC14中正向阈值电压和负向阈值电压是什么/电压为多少2018-10-24 19696

-

阈值电压的计算2017-11-27 75268

-

上达电子李晓华:“卷起来的手机”指日可待2017-10-25 1010

全部0条评论

快来发表一下你的评论吧 !