基于CORDIC算法的实现方法

可编程逻辑

描述

基于LUT的DDS的设计

DDS(Direct Digital Synthesis)直接数字频率合成技术由USA J.Tierncy首先提出。它是一种以数字信号处理理论为基础,从相位概念出发直接合成所需波形的一种新的全数字技术的频率合成方法。DDS主要出现在数字混频系统中。在数字混频中,通过DDS产生正交的本地振荡信号即正、余弦信号与输入信号相乘实现频谱搬移,如通信系统的调制、解调。目前FPGA实现DDS有三种途径:基于IIR滤波器的实现方法、基于查找表LUT的实现方法以及基于CORDIC算法的实现方法。其中采用LUT的方法较为通用且比较容易实现。

1 基于LUT的DDS理论

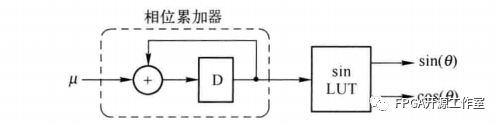

一个典型的基于LUT的DDS系统由相位累加器和波形存储器两部分构成,如图1所示。图中相位累加器的位宽为nbit,步进值为μ,LUT的深度N为2n,宽度为Lbit。LUT中依相位顺序存储一个周期的波形数据。

图1 基于LUT的DDS架构

2 matlab 仿真

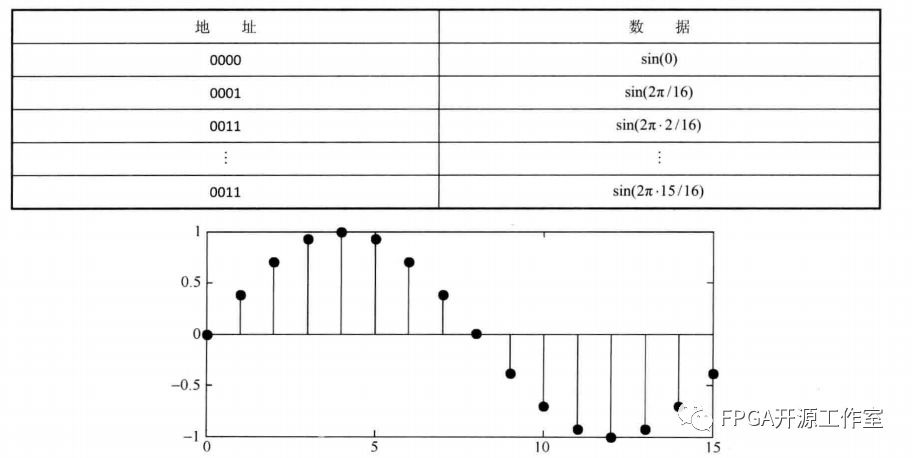

图2 相位累加器位宽为4bit时LUT地址与存储数据的对应关系

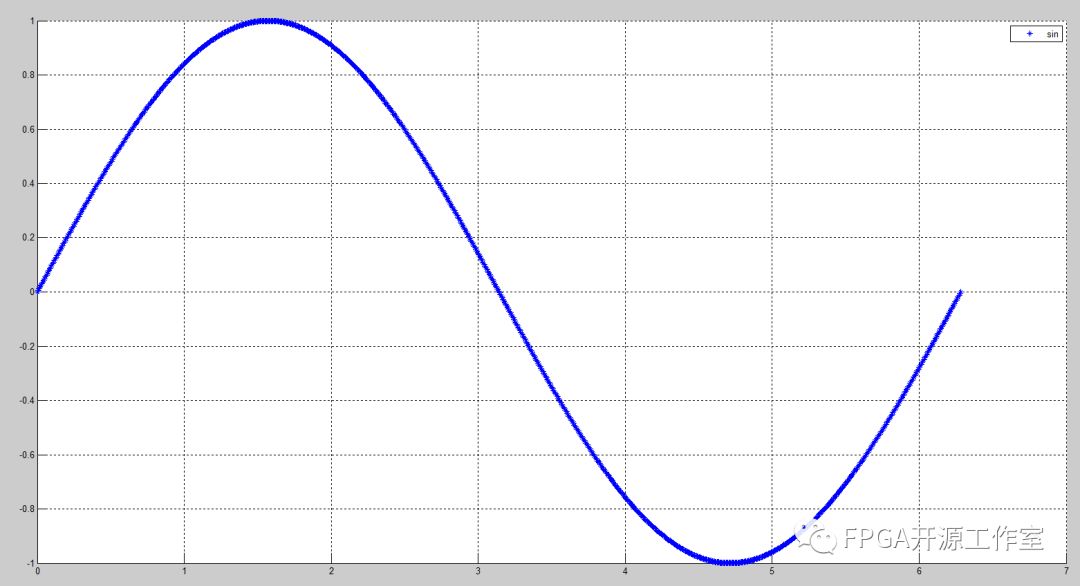

如图2所示,我们要制作地址位宽为10bit数据位宽为32bit的LUT查找表。Matlab源码如下:

clear all

close all

clc

FS = 44100;%采样率

fc = 1000;

N = 1024;%1024点一个正玄周期

t =0:2*pi/(N-1):2*pi;

sin_dds = sin(t);

figure,

hold on

plot(t,sin_dds,'*');

legend('sin');

grid;

hold off

图3 matlab 1024点1个周期的正玄波

3 FPGA仿真

整个仿真结构如图1所示,由相位累加控制器和sin波形存储器组成。仿真生成采样率为44.1KHZ @1KHZ正玄波和余弦波(相位相差90度)。

tb_dds源码:

1. `timescale 1ns / 1ps

2. `define NULL 0

3. module tb_dds();

4.

5. parameter KHZ1 =44;

6. parameter KHZ2 =22;

7. parameter KHZ4 =11;

8. reg clk;

9. initial begin

10. clk = 0;

11. #313333 clk = 0;

12. forever #11.072 clk = ~clk;

13. end//45.1584MHZ

14.

15. reg reset_n;

16. initial begin

17. reset_n = 1;

18. #10000 reset_n = 0;

19. #100000 reset_n = 1;

20. end

21.

22. reg [9:0] addr;

23. reg [9:0] cnt;

24. reg [31:0] k;

25. integer fb;

26.

27. wire signed [31:0] sin;

28. wire signed [31:0] cos;

29.

30. //Phase accumulation controller

31. always @(posedge clk or negedge reset_n) begin

32. if(!reset_n) begin

33. addr <= 0;

34. cnt <= 0;

35. end

36. else if(cnt == KHZ1-1) begin

37. cnt <= 0;

38. addr <= addr +10'd1;

39. end

40. else begin

41. cnt <= cnt + 1;

42. addr <= addr;

43. end

44. end

45.

46. //reg [8:0] i;//88.2khz

47. reg [9:0] i;//44.1khz Sample rate

48. reg signed [31:0] sin_slow;

49. reg signed [31:0] cos_slow;

50.

51. always @(posedge clk or negedge reset_n) begin

52. if(!reset_n) begin

53. i <= 0;

54. sin_slow <= 0;

55. cos_slow <= 0;

56. k <=0;

57. fb = $fopen("sin.dat","w");

58. if(fb == `NULL) begin

59. $display("Can not open sin.dat");

60. $finish;

61. end

62. end

63. else begin

64. i <= i+1;

65. if(i == 0) begin

66. sin_slow <= sin;

67. cos_slow <= cos;

68. k <= k +1;

69. $display("time=[%d],%d",$realtime,sin);

70. $fwrite(fb,"%d ",sin);

71. if(k == 4096) begin

72. $fclose(fb);

73. $stop;

74. end

75. end

76. end

77. end

78.

79.

80.

81. dds_rom U_dds_rom(

82. .clk(clk),

83. .addr(addr),//0-1023 1T

84. .sin(sin),

85. .cos(cos)

86. );

87. endmodule

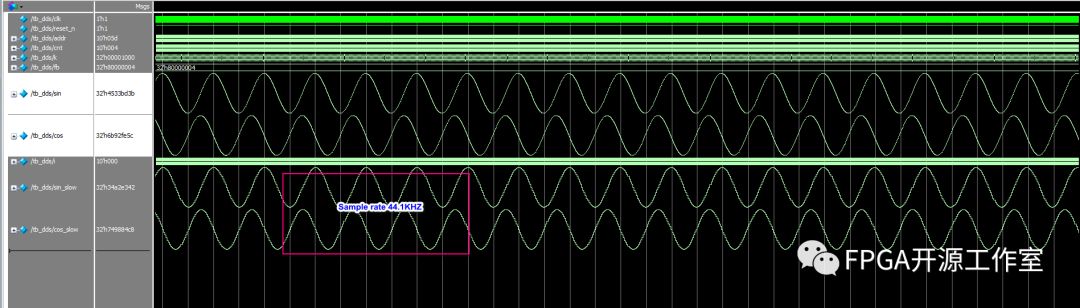

仿真结果:

生成Sample rate 44.1KHZ@1KHZ的正玄和余弦波相位相差90°。

图4 modelsim 仿真结果

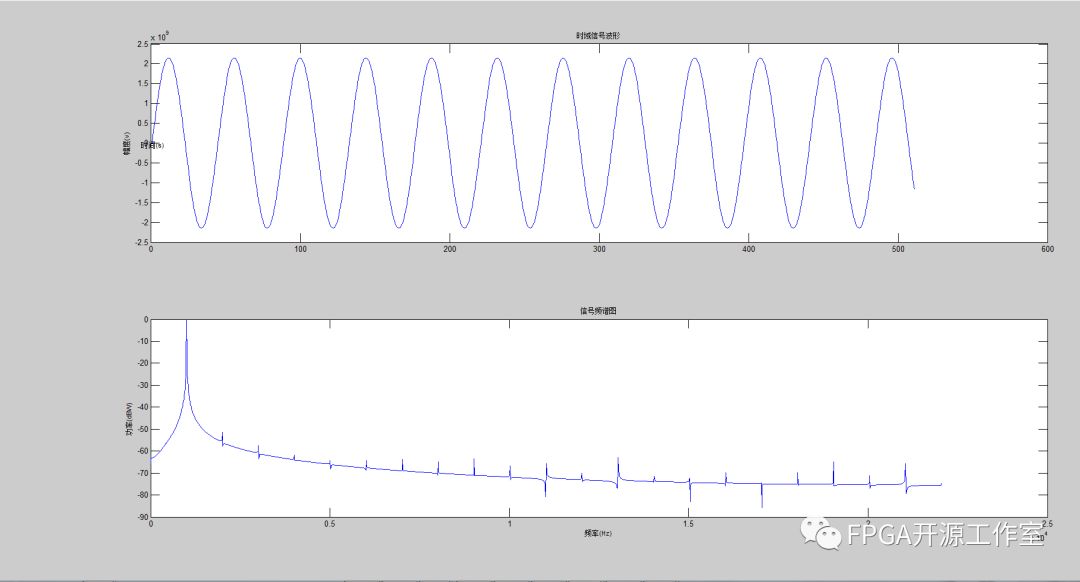

Matlab FFT分析:

图5 FFT分析结果

由图5可知产生的正玄波频率为1KHZ。基于LUT的DDS设计完成,此节将是后期基于FPGA数字信号处理的基础和关键。

编辑:黄飞

-

深度解析CORDIC算法原理2024-04-29 5334

-

使用Verilog HDL设计实现Cordic算法2021-08-16 3394

-

如何使用FPGA实现CORDIC算法在跟踪环中的应用2021-01-22 1264

-

FPGA设计中必须掌握的Cordic算法2019-09-19 6356

-

基于CORDIC的高速Sobel算法实现2018-10-05 4323

-

基于FPGA的Cordic算法实现的设计与验证2018-07-03 3513

-

高速低功耗CORDIC算法的研究与实现2017-11-16 1193

-

cordic算法verilog实现(简单版)2017-02-11 3606

-

CORDIC算法求助2015-07-11 4698

-

基于改进的CORDIC算法的FFT复乘及其FPGA实现2011-07-11 4586

-

双模式CORDIC算法的FPGA实现2011-06-27 1273

-

基于CORDIC算法的载波同步锁相环设计2010-12-15 853

-

利用CORDIC算法在FPGA中实现可参数化的FFT2010-08-09 979

-

高性能HPOR CORDIC算法及实现2009-12-15 801

全部0条评论

快来发表一下你的评论吧 !