加速电容在电路中如何选型?

描述

大家好,我是硬件花园,一名乐于分享的硬件工程师。关注我,了解更多精彩内容!

1 前言

加速电容一般应用于高速场合,在相同容值的情况下优先使用高频特性好的瓷片电容,如果驱动电路中要求加速电容承受负压则必须选择无极性电容如瓷片电容。下文主要从电容的大小来分析阻容负载驱动电路和晶体管驱动电路中加速电容的选型。

2 加速电容选型

2.1 阻容负载驱动电路加速电容大小选择

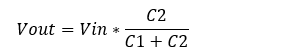

当阶跃开始瞬间t=0时输出电压为:

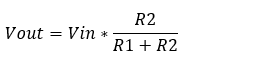

当负载电容充电完成,阶跃稳定t=∞时输出电压为:

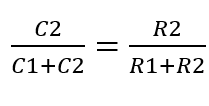

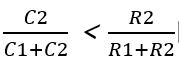

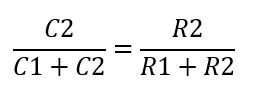

从上面的分析可以看出在整个阶跃响应过程中输出电压分为两个阶段,电压突变开始时输出电压值由电容分压决定,当负载电容完成充电后输出电压值由电阻分压决定。所以如果

,输出电压会有拐点。

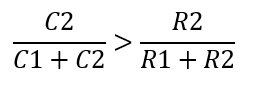

当

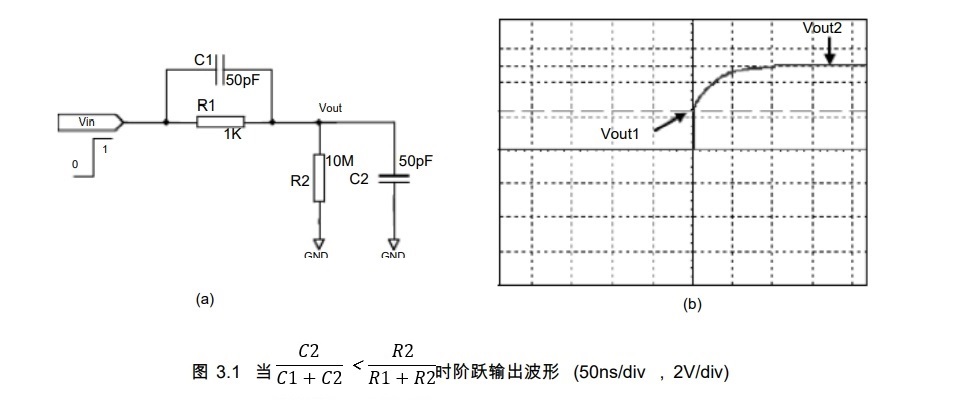

时,如图3.1所示C1=50pF,C2=50pF,R1=1K,R2=10M,输入5V阶跃的输出波形。

上图中,Vout1=2.50V,Vout2=4.99V,输出电压首先迅速上升到Vout1再缓慢上升到Vout2,出现了明显的上升拐点。 当

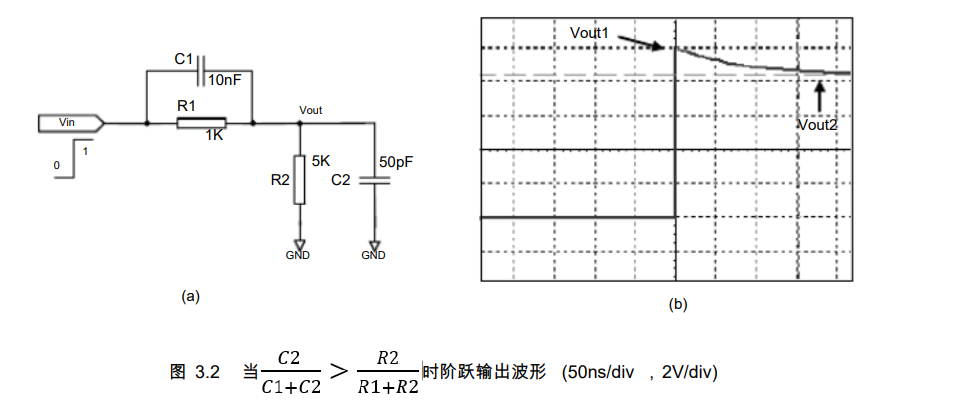

时,如图3.2所示C1=10nF,C2=50pF,R1=1K,R2=5K。输入5V阶跃的输出波形。

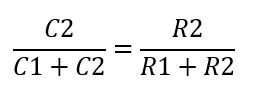

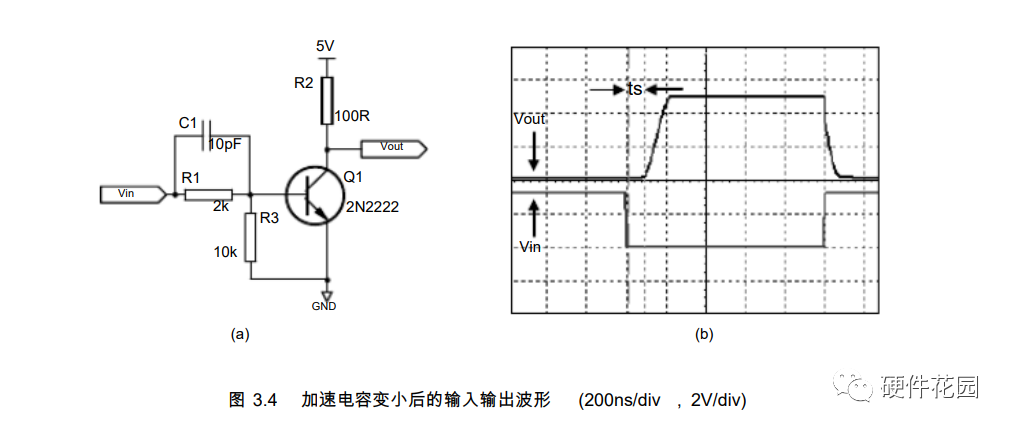

上图中,Vout1=4.97V,Vout2=4.17V,输出波形电压首先迅速上升到Vout1再缓慢下降到Vou2出现明显的过冲现象。 为了取得理想的输出波形,加速电容C1应该满足

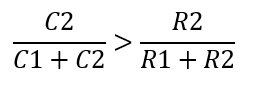

比例关系,但是电容取值有限,很难做到。 实际应用中只要使得二者取值接近就可以了。 以图3.2中的驱动电路为例,负载电阻R2=5K,负载电容C2=50pF,驱动电阻R1=1K,根据

可以求得理想的加速电容值为250pF,但是250pF不是通用的电容取值,可以使用通用的270pF来代替,虽然

但是二者取值已经非常接近。可以满足一般的应用要求。如图3.3所示为加速电容C1=270pF时的输出波形,Vout1=4.21V,Vout2=4.16V。

2.2 晶体管驱动电路加速电容大小选择

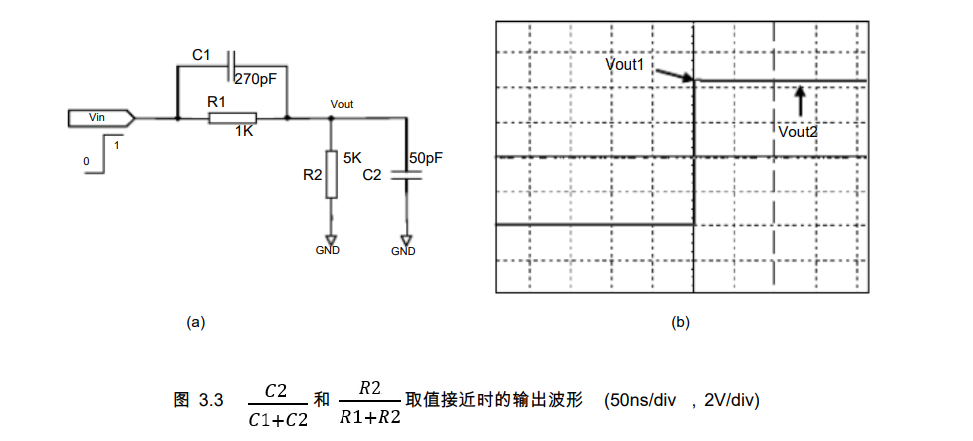

将在《加速电容在电路中的妙用》中提到的图2.4电路中的加速电容从1nF换成10pF,在相同的测试条件下使用Multisim仿真输入和输出波形如图3.4所示。

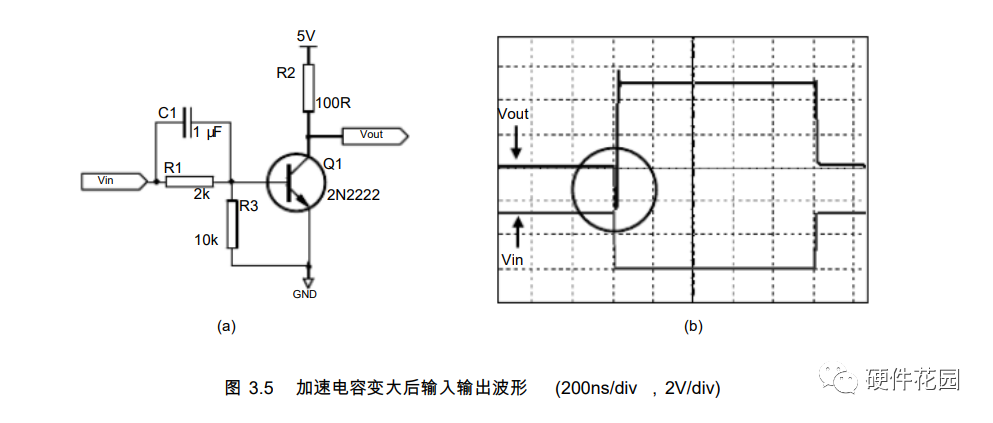

从上图看出,输入和输出波形仍然会有存储时间ts=90ns,加速电容变小后其存储的电荷减少了,不能完全中和掉基区的过量电荷,剩余的电荷通过电阻缓慢释放,所以输入输出仍然存在延迟。通过实际测试,加速电容越大存储时间越小,但并不是电容越大越好。将图2.4电路中的加速电容从1nF换成1uF,在相同的测试条件下使用Multisim仿真输入和输出波形如图3.5所示。

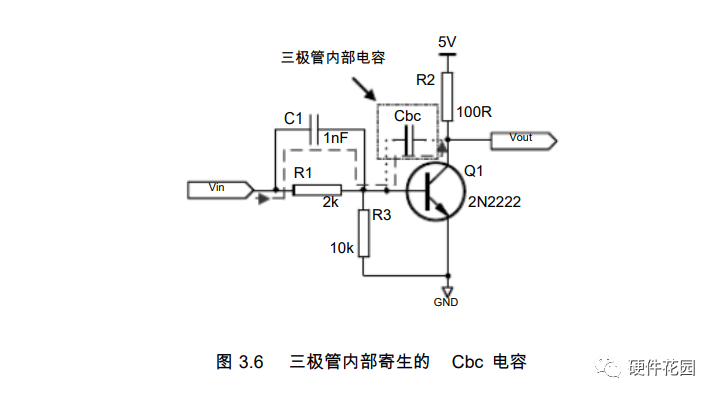

从上图看出,电容加大后存储时间基本消除了,但是输出波形存在严重的下冲现象达到了-2.2V。三极管的集电极和基极之间存在一个寄生电容Cbc如图3.6所示,不同的三极管Cbc大小存在差异,2N2222内部的Cbc为10pF,输入高电平时加速电容充电,最终在C1两端产生(Vin-0.7)V的电压差,当从高电平降到低电平的瞬间,由于C1两端电压不能突变在基极产生一个放电电压,同时Cbc电容两端电压也不能突变,基极的放电电压会通过Cbc影响集电极的输出电压。

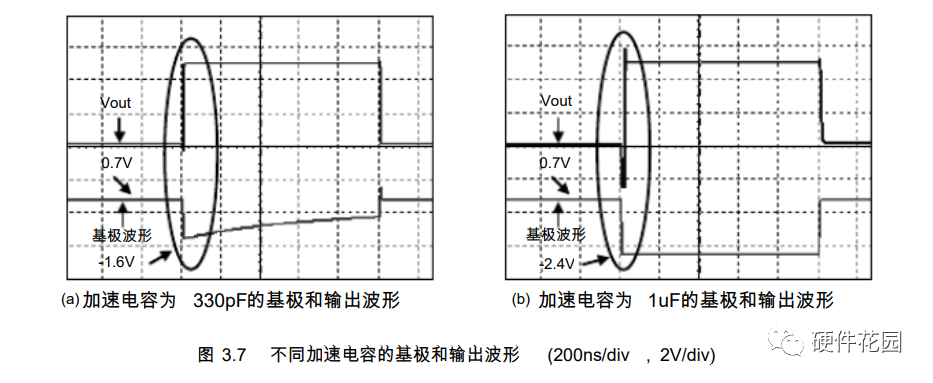

C1电容大小会影响基极的放电电压。如图3.7所示,C1电容变小时,其存储的电荷减少了,在基极产生的放电电压幅值变小,输出电压基本无过冲,C1电容变大后,存储电荷增多了,在基极产生的放电电压幅值变大,输出电压出现明显过冲。

根据上述分析,在晶体管驱动电路中,加速电容如果选择过小仍然会有延迟时间,如果过大则会造成输出波形出现过冲,所以电容值应该通过实测具体电路的输出波形来选择。

审核编辑:汤梓红

-

schhqq

2023-09-25

0 回复 举报一看公式还不对, 收起回复

schhqq

2023-09-25

0 回复 举报一看公式还不对, 收起回复

-

jf_55498201

2023-06-08

0 回复 举报写的初始公式与例题的不对应, 收起回复

jf_55498201

2023-06-08

0 回复 举报写的初始公式与例题的不对应, 收起回复

-

关于加速电容电路的基础知识详解2024-01-30 4077

-

一文搞懂加速电容工作原理、如何选型及应用2023-02-13 6088

-

加速电容应用案例、如何选型和工作原理2023-01-09 1943

-

加速电容在电路中的应用2023-01-05 1759

-

加速电容在电路中的妙用2022-12-27 1810

-

使用加速电容实现何为加速电容2021-11-06 7651

-

电容在电路中的27中应用,你学会了吗?2019-09-16 2268

-

三极管做开关加速电容时是否会被高电平引起的大电流烧坏?2019-08-01 5042

-

加速电容电路工作原理分析2019-05-09 2110

-

电容在电路中的作用及电容滤波原理2018-12-30 5587

-

加速电容_工程技术笔记2015-12-18 718

-

浅谈不同电容器在医疗电子中的选型及应用2012-12-16 4119

-

加速电路及其波形2009-09-22 2070

全部0条评论

快来发表一下你的评论吧 !