高速转换器技术的进步使下一代无线通信系统设计成为可能

描述

作者:Yi Zhang and Michelle Viani

随着消费者对增强数据服务和更多带宽使用的需求不断增加,无线通信网络正在迅速发展。新一代无线通信系统需要更高的数据吞吐量、更低的功耗和更高的可靠性。这些要求经常相互冲突。满足这些需求需要高采样率、高信号带宽和高能效数模转换器(DAC)解决方案。新一代高速DAC产品具有GSPS采样率和输入数据速率,为多频段、多标准无线电基站提供多载波GSM兼容性能,同时降低系统总功耗和散热密度。本文讨论高速转换器如何通过提供更高的采样速率、更大的数据带宽和更低的功耗来帮助系统设计人员推进无线通信系统设计的创新前沿。

高带宽下的系统挑战

现代移动基站的传输带宽超过300 MHz的情况并不少见。支持更宽的日期带宽和数字预失真技术的要求提高了高速DAC产品可用信号带宽和动态性能的标准。实现更高系统带宽的挑战有三个方面。

首先,更高的信号带宽需要更快的DAC采样速率。奈奎斯特-香农采样定理要求转换器采样速率至少是要合成信号的两倍。因此,在不考虑其他设计约束的情况下,DAC采样速率需要以信号带宽速率的2倍增加。模拟重建滤波是系统设计中推动更快DAC采样速率的另一个主要因素。在无线发射器中内置砖墙模拟滤波器既不可行也不高效。实际上,系统要求DAC采样速率在合成信号带宽上具有一定的过采样比,以便在所需信号和需要抑制的高频DAC采样镜像之间建立滤波器过渡带。例如,如果要合成的信号在150 MHz的中心频率周围传播±50 MHz,则DAC输出信号的高端为200 MHz,而当信号以300 MHz为中心,带宽为±150 MHz时,则为450 MHz。可以看出,第二种情况需要具有更高采样率的DAC。

其次,更高的信号带宽需要更快、更可靠的转换器日期接口。所需的信号带宽与传输日期吞吐量成比例增加。为了使用I/Q调制实现300 MHz系统带宽,双通道DAC(I和Q)的组合输入数据速率为750 MSPS,考虑0.2的滤波器滚降因子。这意味着输入日期周期为1.33 ns,这给系统设计人员带来了很大的压力,要求他们最大限度地减少数据总线上的位间时序失调,以满足建立和保持时序要求。对于传统的并行数据接口方案,如LVDS和CMOS,这是非常具有挑战性的。新型JESD204B高速串行接口为迁移到更高的数据速率提供了可靠且可扩展的解决方案。

第三,集成电路(IC)器件不是理想的元件。DAC也不例外。较高的输出带宽要求DAC器件具有更好的动态性能,原因有两个。动态范围通常随着DAC输出频率的增加而减小。此外,当带宽较大时,更多的杂散内容往往会落在带内。但是,系统杂散要求不会随信号带宽而扩展或放松。无论支持的信号带宽如何,移动基站仍然需要满足受监管的发射模板要求。具有卓越动态性能的DAC简化了系统的频率规划和滤波。

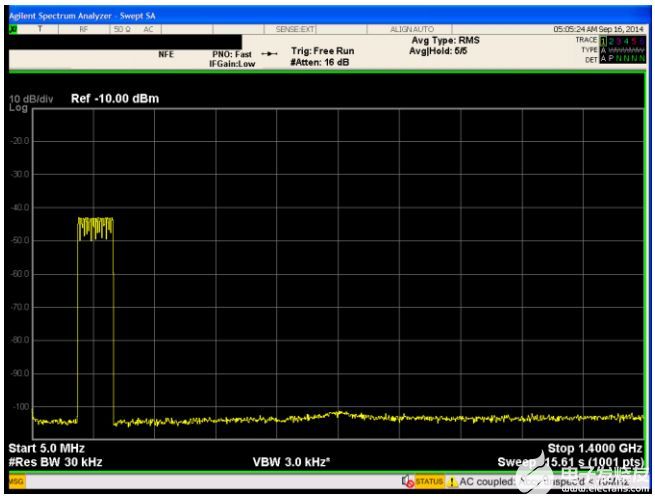

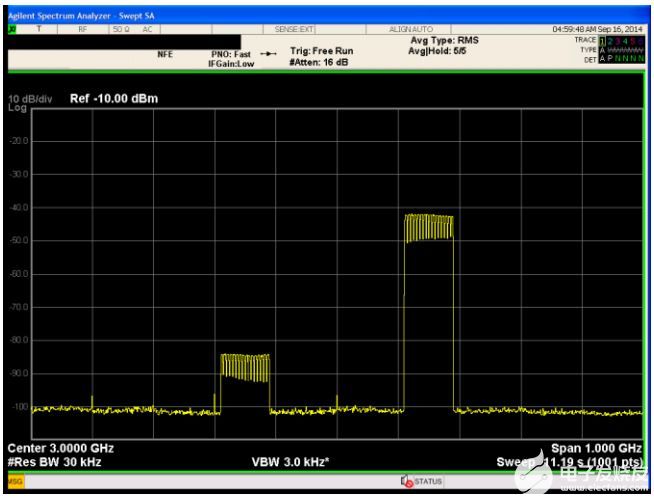

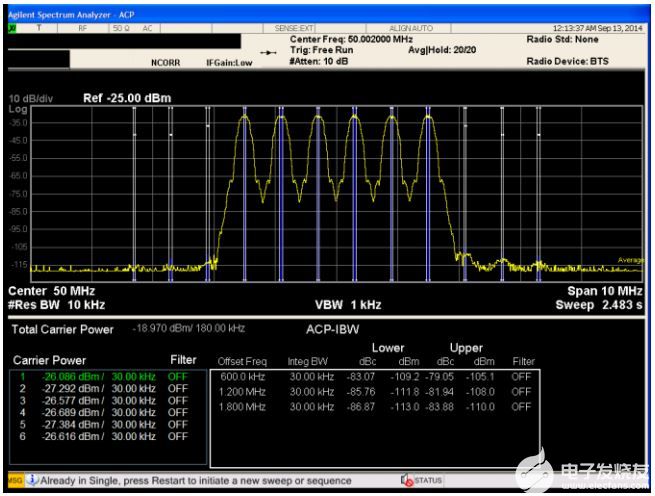

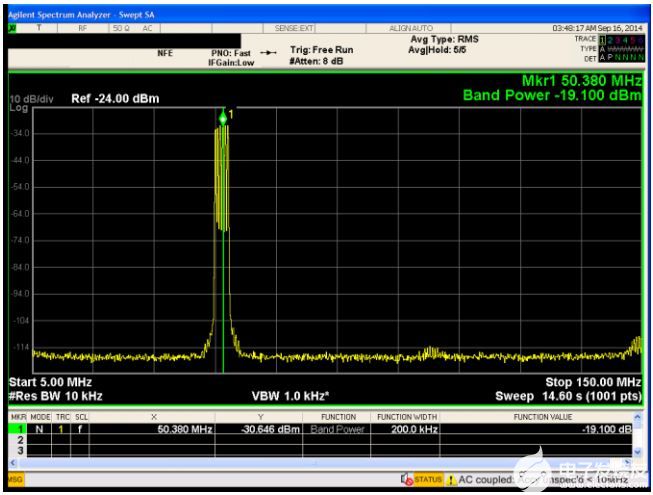

图1和图2显示了AD9144 DAC以2800 MSPS的DAC采样速率合成80 MHz信号(16载波W-CDMA)的实测频谱性能。

图1.测量的AD9144 DAC的宽带性能(高达奈奎斯特频率) 合成16载波W-CDMA信号,f代数转换器= 2800 MSPS。

图2.在ADRF6720下测得的宽带性能1QMOD输出为3 GHz RF频率,AD9144 DAC输出(如图1所示)驱动QMOD。

低功耗和高可靠性的系统挑战

系统设计人员在增加传输带宽和数据容量方面还面临着其他挑战。这些挑战包括功耗、散热和系统可靠性。这些维度通常与更高系统带宽的目标正交,有时甚至冲突。因此,系统设计人员需要一种新的DAC产品,该产品能够在同一封装中提供更高水平的功能集成、更低的功耗、更低的工作热密度和更宽的带宽。

近年来,高速DAC产品发展迅速,DAC产品中集成了更多的数字和模拟功能。两个明显的例子是DAC片上时钟乘法器PLL和通信专用信号处理功能。这些功能过去在系统的其他位置实现,例如高速时钟合成器和基带ASIC/FPGA。具有这些功能的DAC不仅可以降低整体BOM成本,还可以为更简单、更可靠的设计提供途径。利用DAC中的时钟倍频器,系统只需为器件提供一个低频参考时钟。时钟乘法器锁定至外部参考时钟,并在内部为DAC生成高速采样时钟。这意味着无需担心PCB上的高速时钟耦合和走线阻抗匹配。功率检测和保护等新的数字功能为射频链提供了额外的保护层,防止超量程信号或异常系统行为损坏。尽管功能集成度更高,但与上一代产品相比,DAC器件的功耗基本保持不变,甚至有所下降。高速DAC技术在更精细的硅工艺节点上的进步在应对系统挑战方面发挥着重要作用。

除了消耗更少的功率和更小的碳排放足迹外,降低组件功耗的另一个重要好处是更低的热密度。无线通信系统通常被限制在防水金属机箱内。尺寸和重量限制通常不允许主动冷却。IC元件产生的热量通过机箱散发。机箱内部的型腔和PCB温度可能非常高,以至于开始影响系统的长期可靠性。积聚的热量可能会影响PCB的机械特性、元件和电路板之间的焊点,并加速IC元件电气规格的长期老化变化。系统中的热量分布/散发不均匀。贡献主要来自信号处理丰富的几个来源。高速DAC就是其中之一。因此,功能丰富且功耗低的DAC对系统设计人员非常有吸引力。

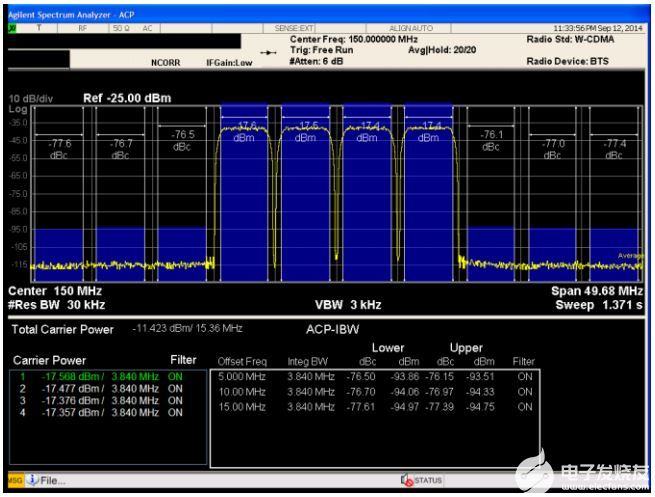

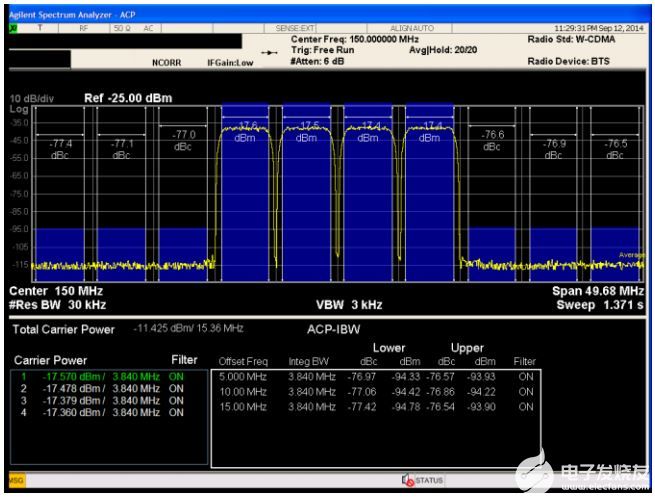

图3和图4显示了AD9144在DAC采样速率为1966 MSPS时合成4载波W-CDMA信号的实测性能,片内DAC时钟乘法器分别打开和关闭。

图3.在启用片内时钟乘法器的情况下,在150 MHz输出频率下测得的AD9144的4载波W-CDMA ACLR性能,f裁判= 245.76兆赫,f代数转换器= 1966 MSPS。

图4.在禁用片内时钟乘法器的情况下,在150 MHz输出频率下测得的4载波W-CDMA ACLR性能AD9144,f代数转换器= 1966 MSPS。

通用平台设计中的系统挑战

在要求覆盖范围更广、带宽更高的同时,消费者对日期服务需求的快速扩张也要求多标准无线电 (MSR) 基站。不同的无线电技术和不断增加的频率分配使控制网络和降低成本变得更加复杂。满足这些需求需要一种高效且相对便宜的解决方案来解决构建MSR基站的问题,这是一种通用的平台设计。DAC技术的进步支持基站设计的这种演变。多载波GSM(MC-GSM)通常被认为是具有最严格动态范围要求的空气标准。MC-GSM测试通常用于判断DAC产品是否支持通用平台设计。

图5和图6显示了AD9144以1966 MSPS的DAC采样速率合成6 C-GSM信号的实测性能。

图5.在50 MHz DAC输出频率下测得AD9144的6C-GSM IMD性能,f代数转换器= 1966 MSPS。

图6.在50 MHz DAC输出频率下测得AD9144的6 C-GSM宽带性能,f代数转换器= 1966 MSPS。

总结

现代无线通信网络正在不断发展,以提供更多的日期服务和更多的带宽使用。为了支持这一趋势,新一代无线通信系统需要具有更高的数据吞吐量、更低的功耗和更高的可靠性。高速DAC技术的进步,如ADI公司的AD9144,实现了下一代多标准无线电设计,并帮助系统设计人员在多个关键技术维度上实现了突破性创新。

审核编辑:郭婷

-

【wigig是什么意思?比wifi更高速的新一代通信技术】2013-04-27 5357

-

高速转换器的创新从三个方面改变世界2018-10-11 1421

-

射频转换器为下一代无线基站提供高效的多波段无线电2018-12-13 3955

-

5G时代下的无线通信系统展望2019-07-11 3071

-

为什么说RF转换器技术的进步使得新型数据采集系统和宽带无线电成为了可能?2019-07-31 2086

-

无线通信与下一代技术齐头并进2022-03-08 7963

-

下一代无线通信技术对卫星通信系统的影响2011-03-20 853

-

下一代宽带无线通信网络信令体系结构2011-05-24 1308

-

高速转换器技术的进步对下一代无线通信系统设计的支持2017-11-16 1052

-

下一代无线技术是VR下一代发展的缺失环节2019-08-11 1112

-

基于FPGA的无线通信系统设计与实现2021-06-16 1673

-

下一代无线通信的氮化镓功率放大器2022-12-22 949

-

基于nRF24L01的无线通信系统设计2023-10-26 642

-

RF转换器为下一代无线基站提供多频段无线电2023-11-23 477

全部0条评论

快来发表一下你的评论吧 !