低噪声、精密运算放大器驱动高分辨率SAR ADC

描述

作者:Kris Lokere and Erjon Qirko

LT6018 是一款超低噪声 (1kHz 时为 1.2nV/√Hz) 运算放大器,具有超低失真 (1kHz 时为 –115dB)。该器件的增益带宽积为 15MHz,最大失调电压为 50μV,最大失调电压漂移为 0.5μV/°C。 这种特性组合使其适合驱动各种高分辨率模数转换器(ADC)。本设计笔记介绍了在使用 LT6018 驱动高速 18 位和 20 位逐次逼近寄存器 (SAR) ADC 时实现最佳信噪比 (SNR) 和总谐波失真 (THD) 的电路和优化策略。

超线性 20 位 ADC

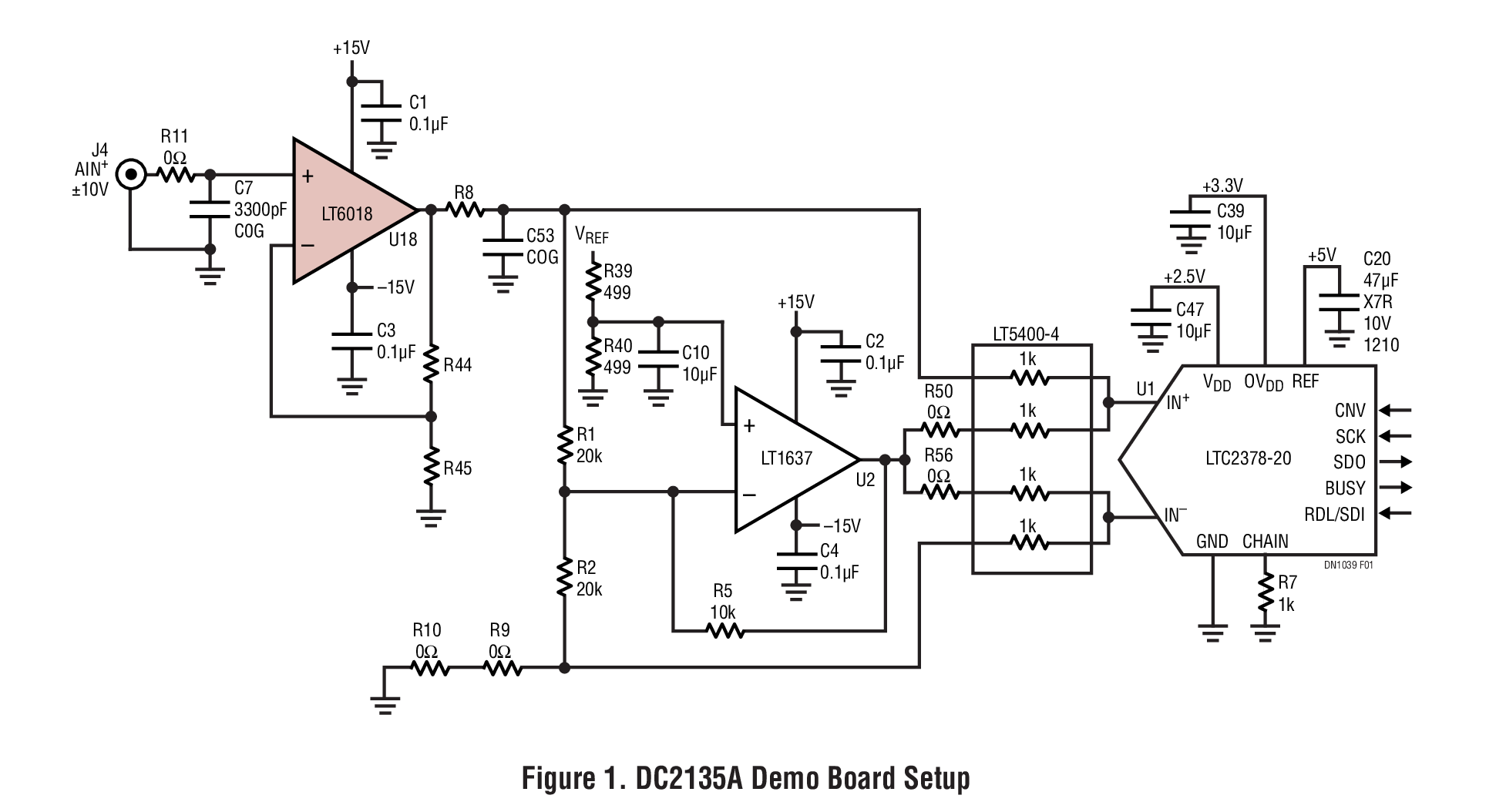

图 1 示出了 DC2135A 演示电路的修改,其中 LT6018 (取代 LT1468) 驱动 LTC2378-20 20 位 SAR ADC。LTC2378-20 以其无与伦比的 2ppm 线性度性能而著称。在保持线性度的同时产生差分信号的最佳方法是使用本演示板中使用的LT5400中的精准匹配电阻器。图 1 所示电路的详细工作原理出现在设计笔记 1032 (其中 LT1468 驱动 LTC2377-20)。

为了测量电路的线性度,将超纯正弦波馈入输入端,并在输出端计算FFT。由此产生的THD测量值可代表电路的INL(积分非线性)性能。在800kHz的ADC采样速率下,我们使用约100Hz的输入频率(略微调整以确保相干采样,减轻FFT数值限制)。

原始演示电路包括一个RC低通滤波器,直接位于运算放大器之后,用于滤除多余的高频噪声。即使在高频下,LT6018 的噪声密度也保持相对较低,因此移除此滤波器对总噪声的影响可以忽略不计。在没有滤波器的情况下,线性度 (由 THD 测量) 显著提高,因为单端至差分转换现在完全由 LT5400 中精确匹配的电阻器控制,不受任何匹配不良的分立组件的破坏。

LT6018 的低噪声密度使其适合于需要增益的电路。配置为增益为10时,信号强度增加20dB,而SNR相对于满量程降低2dB。如果输入信号很小,这种布置可将有效信噪比提高18dB。正如预期的那样,线性度的降低幅度与放大器环路增益相同,即约20dB。

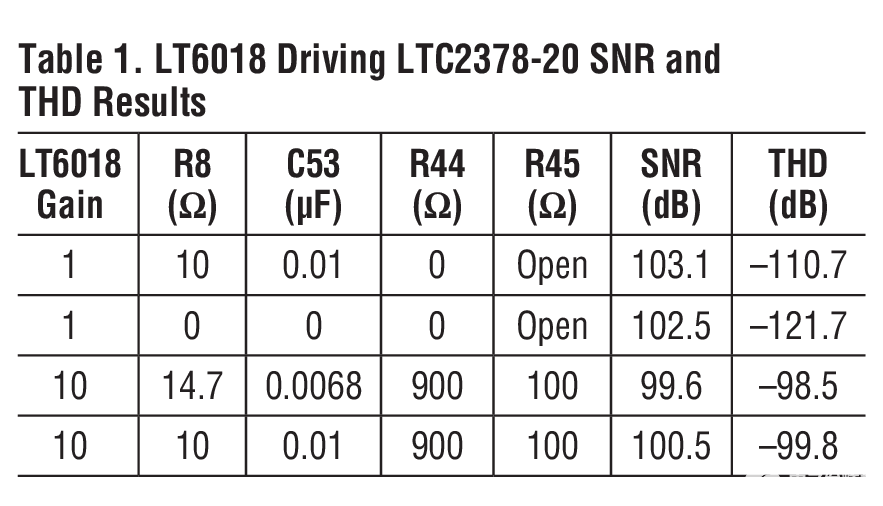

结果总结在表1中。

驱动高速18位ADC

LTC®2387-18 是一款 18 位 SAR ADC,其采样速率高达 15Msps。在此采样速率下,ADC的内部采样电容连接到放大器输出的时间不到30ns(“采集时间”)。在此期间,放大器(和滤波器)电路必须从电荷反冲中恢复并补充采样电容的电荷,以便ADC可以在下一个转换周期测量正确的输入电压。需要仔细优化放大器和滤波器网络。

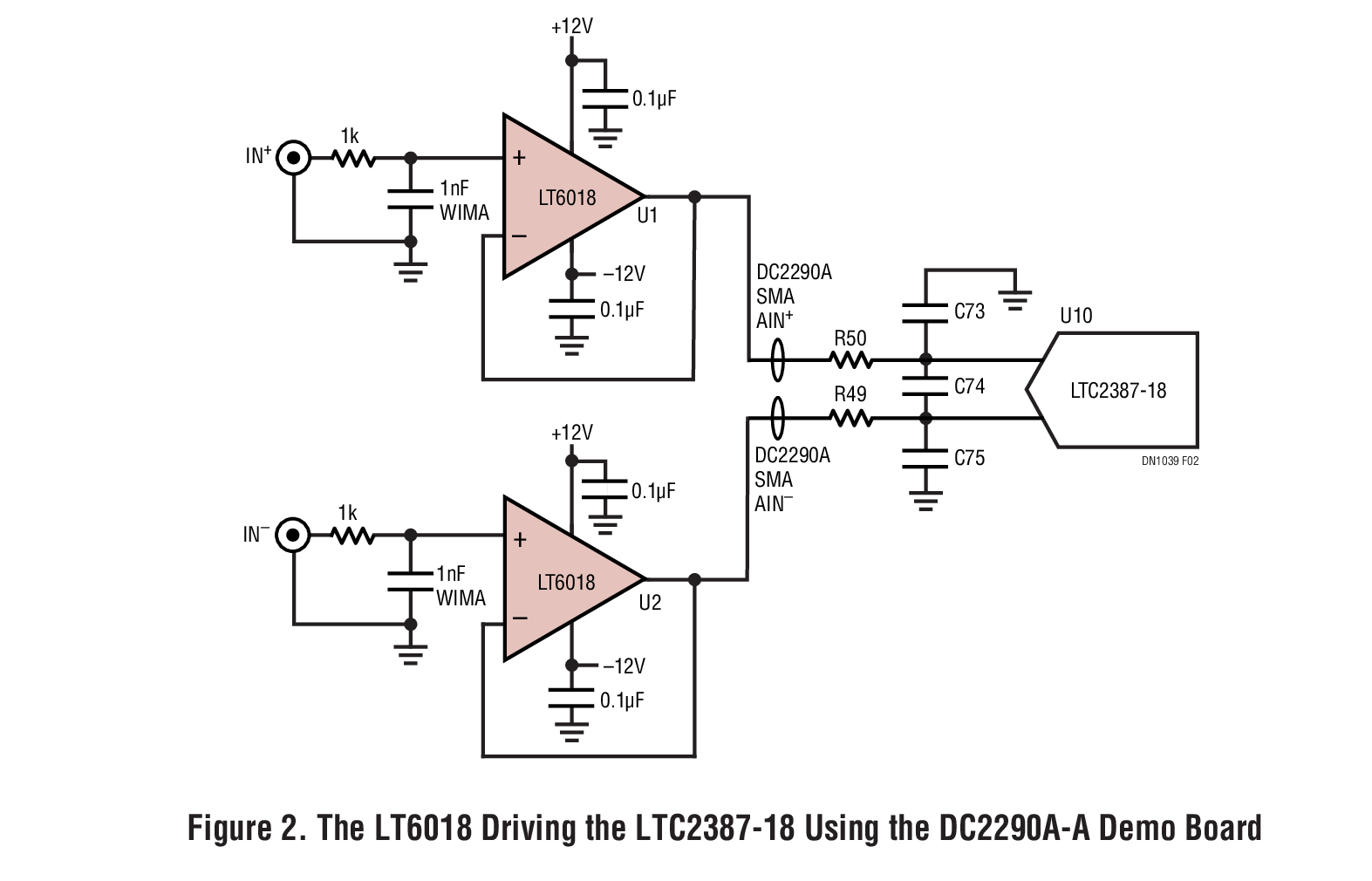

在图 2 中,两个 LT6018 配置为单位增益跟随器,并连接到 LTC2387-18 演示板,该演示板在 ADC 输入端提供了滤波电阻器和电容器。

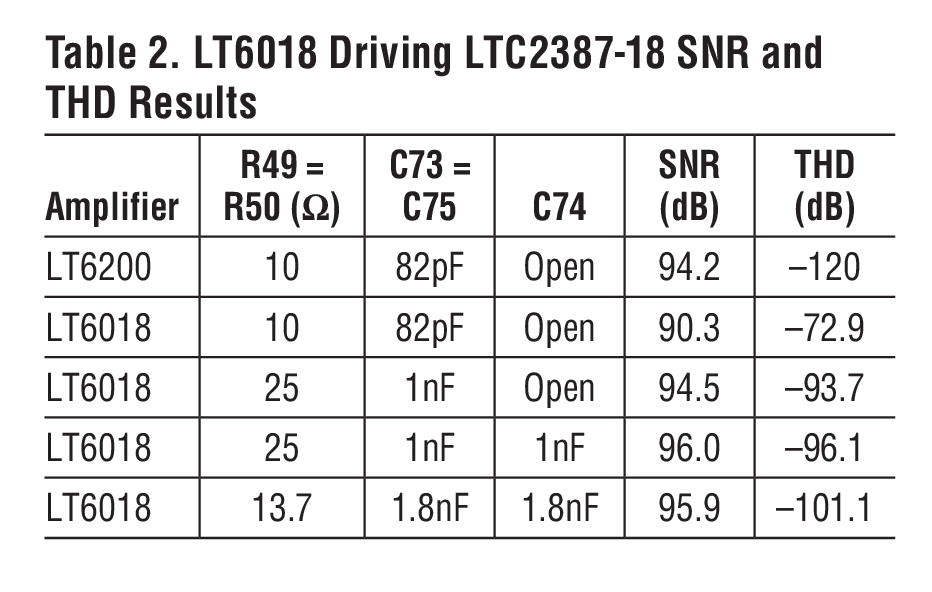

表2显示了在输入端以1.008kHz纯正弦波测得的SNR和THD结果,以及相干14.680Msps的ADC采样。第一个表条目显示了LT6200放大器(一款非常高速度、低噪声的运放)的结果。滤波器配置为演示板默认带宽约200MHz。这允许ADC电荷反冲完全建立,从而实现–120dB的出色THD。但是,SNR比ADC的96dB能力低2dB。

LT6018 具有比 LT6200 更低的带宽,但 DC 准确度 (失调和漂移)要好得多。然而,将 LT6018 插入与 LT6200 相同的配置会显著降低 SNR 和 THD。SNR会降低,因为放大器噪声密度可能高于其带宽高于低于带宽,如果不进行滤波,该噪声将混叠到ADC中。THD之所以会降低,是因为速度较慢的放大器(当被全ADC电荷反冲击中时)不能正确建立,并留下非线性残余供ADC数字化。

我们可以通过增加电阻和电容的值,并在两个ADC输入之间加入差分电容来滤除宽带放大器噪声。这样做可以将SNR一直提高到该ADC的理论最大值96dB,这意味着集成放大器噪声可以忽略不计。此外,通过将滤波器配置偏向较小的串联电阻和较大的电容,电荷反冲的初始效应会衰减,从而改善THD性能,远低于–100dB。

结论

现代SAR ADC集低噪声、高线性度和精确的直流失调精度于一身。实现这些规格需要具有类似良好直流规格、低噪声和足够带宽的放大器,例如LT6018。利用中速 ADC (例如 1Msps 20 位 LTC2378-20),LT6018 与精准匹配的 LT5400 电阻器相结合,可产生一个差分输入信号,而无需额外的滤波。利用超快SAR ADC (例如18位15MspsLTC2387-18),仔细优化运算放大器和ADC之间的RC滤波器网络可实现出色的噪声和线性度性能。

审核编辑:郭婷

-

RS8661/2/4系列高压精密低噪声运算放大器简介2024-08-26 1714

-

低噪声、高精度运算放大器驱动高分辨率SAR/ADC2021-05-27 1022

-

低噪声精密运算放大器驱动高分辨率 SAR ADC2021-01-21 1202

-

低噪声零漂移运算放大高分辨率数据采集2020-07-23 2943

-

低噪声高速精密的运算放大器2020-06-19 2574

-

单个200MHz低噪声精密运算放大器2020-06-05 2551

-

一款驱动高分辨率的SAR ADC器件分析2019-08-14 4610

-

高分辨率精密ADC的杂散产生原因是什么?2019-08-12 4011

-

为什么高分辨率 Δ-Σ 模数转换器中会有噪声?2019-08-08 2327

-

ADC的噪声、ENOB及有效分辨率2018-11-26 2888

-

驱动高分辨率 SAR ADC2018-06-07 5421

-

基于LT6018最佳驱动高分辨率SAR ADC设计2017-11-29 856

-

使运算放大器的噪声性能与ADC相匹配2009-11-21 8687

全部0条评论

快来发表一下你的评论吧 !