LTspice:仿真SAR ADC模拟输入

描述

作者:Kris Lokere and Gabino Alonso

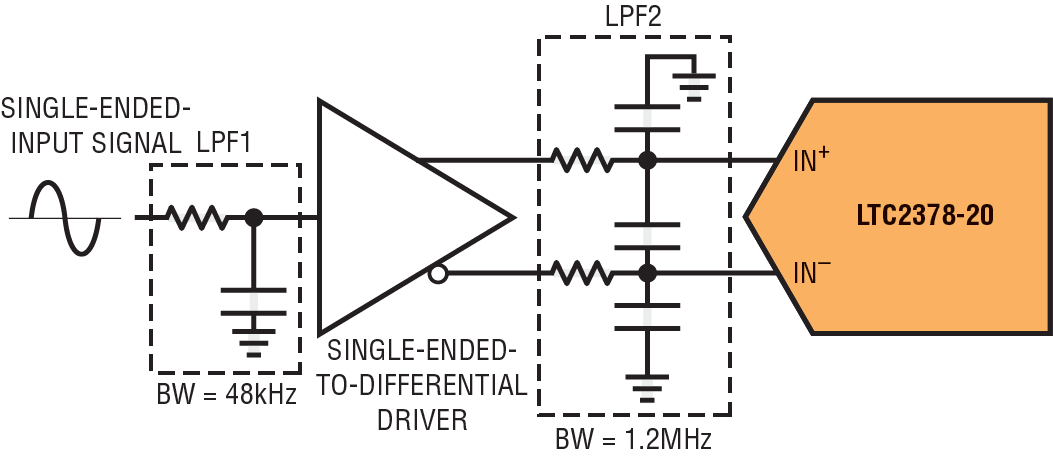

随着ADC分辨率和采样速率的不断提高,模拟输入的驱动器电路(而不是ADC本身)日益成为决定整体电路精度的限制因素。除了用于噪声输入信号的简单1极点RC低通滤波器(LPF1)(图1)之外,缓冲器和ADC输入之间通常使用耦合RC滤波器网络(LPF2),以最大程度地减少ADC采样瞬变反射到缓冲器的干扰。模拟输入端的长RC时间常数会减慢这些干扰的建立速度。因此,LPF2 通常需要比 LPF1 更宽的带宽。该滤波器还有助于最大限度地减少缓冲器的噪声贡献。

图1.仿真放大器和ADC之间的接口有助于确定噪声和建立时间之间的权衡。

仿真放大器和ADC之间的接口,在建立时间和噪声性能之间提出了一些有趣的权衡。对此类仿真进行实验有助于直观地了解滤波器设计如何影响这些性能方面。

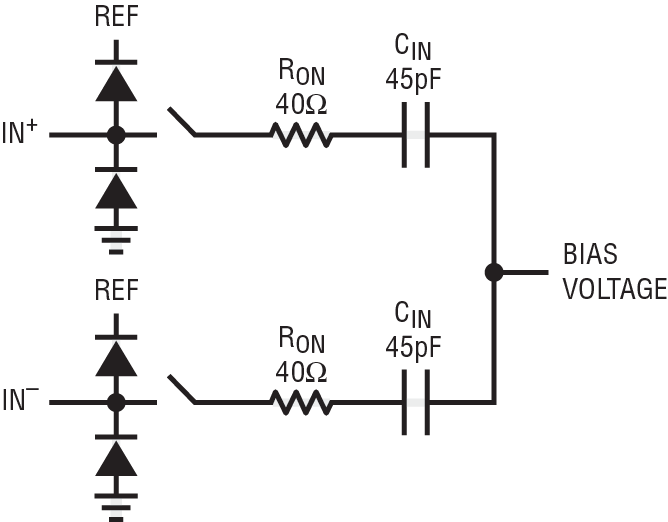

全差分SAR ADC的模拟输入可以建模为驱动电路上的开关电容负载,如图2所示。所示值来自 LTC2378-20 20 位、1Msps、低功率 SAR ADC,但可轻松修改以表示其他 ADC。在采集阶段,每个输入从采样CDAC获得约45pF (CIN),从采样开关的导通电阻看到40Ω (RON)。输入在此相位为 CIN 电容器充电时会吸收电流尖峰。在随后的转换阶段,模拟输入仅吸收很小的漏电流,电容完全放电。这种 ADC 模拟输入建模突出了将放大器耦合到 SAR ADC(如 LTC2378-20)的最大挑战之一;处理每个采集阶段开始时ADC输入端消耗的电流尖峰。

图2.SAR ADC模拟输入的等效电路。

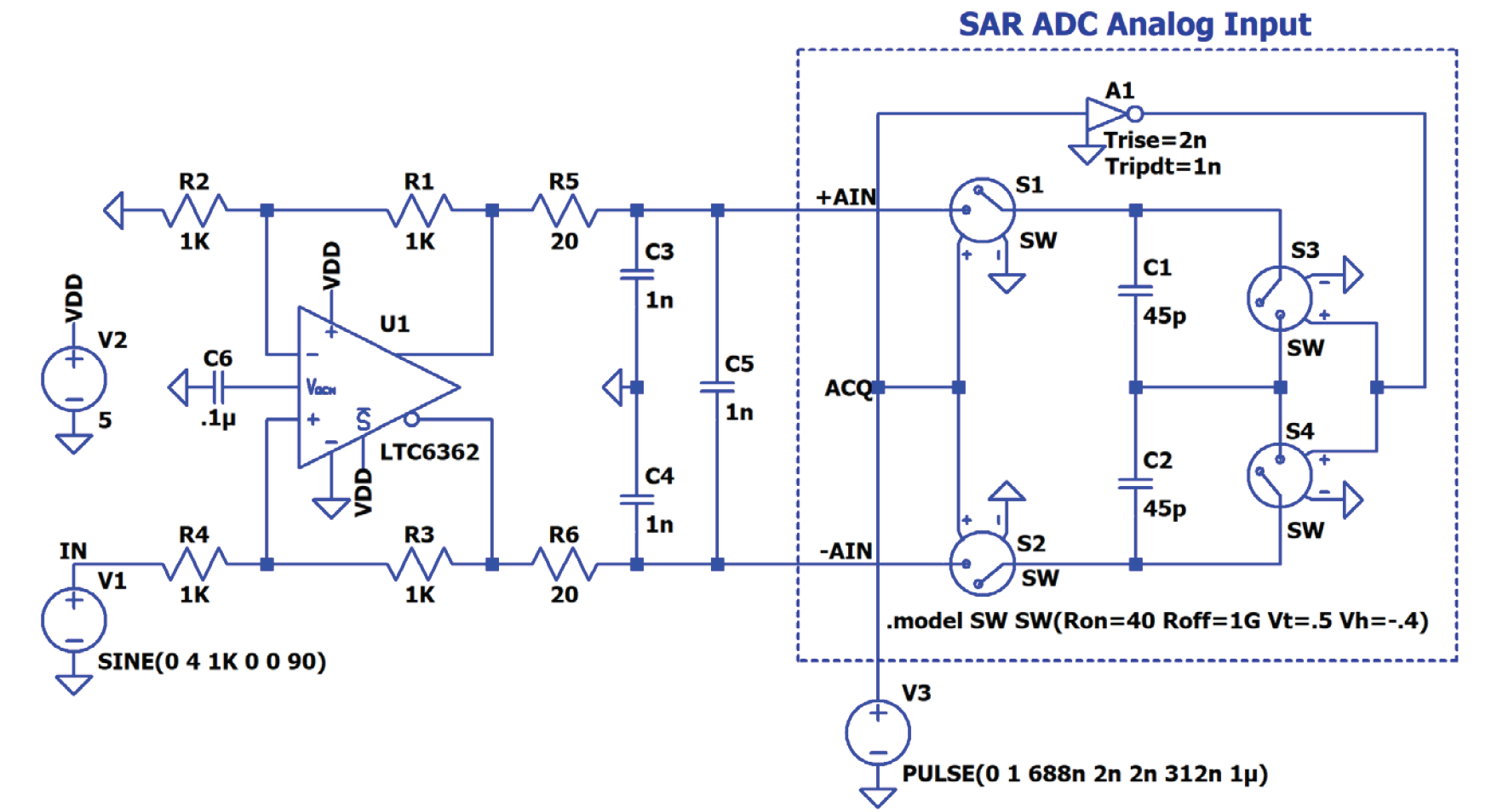

该等效电路的仿真原理图如图3所示。低功率差分运放 LTC6362 配置为将一个单端输入信号转换为一个全差分输出以驱动 LTC2378-20。为了简化仿真,不包括输入ESD保护二极管。两个45pF输入电容(C1和C2)通过稳压开关(S1和S2)充电,这些开关由导通电阻为40Ω的SW模型语句定义。这些开关由一个持续时间为 312ns 和周期为 1μs 的脉冲电压源驱动,以模拟 LTC2378-20 SAR ADC 在 1Msps 时的采集时间。为了使采样电容为下一个采集阶段做好准备,使用理想化行为逆变器(A1)来打开对电容放电的第二组开关(S3和S4)。

图3.SAR ADC模拟输入等效电路仿真原理图。

放大器和ADC之间的RC滤波器网络有多种用途。首先,滤波器网络减少进入ADC的宽带噪声量。其次,电容用作电荷储存器,吸收来自ADC内部采样电容的电荷反冲。在每个转换周期之后,放电的采样电容(45pF)重新连接到放大器电路。通过在ADC输入端放置一个大得多的储能电容,可以减少这些采样电容引起的电压偏移。然而,在宽带噪声和建立时间性能之间需要权衡取舍。当采样电容连接到放大器电路(采集时间)时,RC网络应完全建立到ADC的分辨率范围内。在滤波器网络中使用过多的储能电容会使建立时间超出可接受的限值。

审核编辑:郭婷

-

探索不同的SAR ADC模拟输入架构2023-01-08 2807

-

SAR ADC 的输入注意事项2022-11-04 825

-

如何使用LTspice模拟 SAR ADC 模拟输入?2022-04-12 52364

-

SAR ADC的采样过程和模拟输入结构2022-01-28 4433

-

模拟基础知识:处理SAR ADC输入驱动难题2021-11-05 3415

-

SAR ADC输入类型2021-04-22 949

-

SAR ADC模拟输入架构怎么选?2021-03-08 1558

-

使用sar adc时的模拟路由错误该怎么办?2019-10-30 1909

-

如何使用LTspice仿真SAR ADC的输入2019-08-07 9417

-

如何利用SAR ADC数据手册建立TINA SPICE仿真模型2019-04-12 5244

-

SAR ADC模拟输入架构2018-10-18 3375

-

不同的SAR ADC模拟输入架构研究2018-10-17 1864

-

探索不同的SAR ADC 模拟输入架构2018-09-15 3886

-

SAR与ADC不同输入类型2018-09-11 3132

全部0条评论

快来发表一下你的评论吧 !