用于高分辨率1Msps ADC的μModule隔离解决方案

描述

模数转换器(ADC)的理想隔离器是不可见的。它管理所有控制和数据信号,最大限度地提高采样率,并将抖动对SNR性能的影响降至最低。LTM2893 μModule 隔离器实现了具有 SPI 接口的 ADC 的这些目标(范围为 1Msps),并支持 6000V有效值隔离等级。

通过数字隔离器从高分辨率逐次逼近寄存器(SAR)模数转换器读取数据受到限制,而传统隔离器则受到限制 选项。当从串行外设接口(SPI)读取数据时,大多数高速数字隔离器的最大频率为25MHz,少数专用器件的工作频率高达40MHz。LTM2893 读取高达 100MHz 的数据,具有灵活性,可处理多个 ADC,从而解决了与 SAR ADC 接口的标准数字隔离器的时序问题和限制。

隔离ADC的原因

隔离栅允许ADC浮动至输入信号的共模,并吸收恶劣条件和瞬变。即使是不需要隔离的应用程序也可以从中受益。LTM2893 使得添加隔离层变得特别容易,从而提高了系统安全性。例如,过程和测试设备需要隔离以保护输入免受意外错误连接或过压事件造成的损坏,而隔离器也可以用作高压电平转换器,以扩展共模范围或降低接地噪声。LTM2893 利用一个低电容隔离栅和全差分数据通信来忽略高达 50kV/μs 的共模瞬态事件。

以前的通用数字隔离器不足

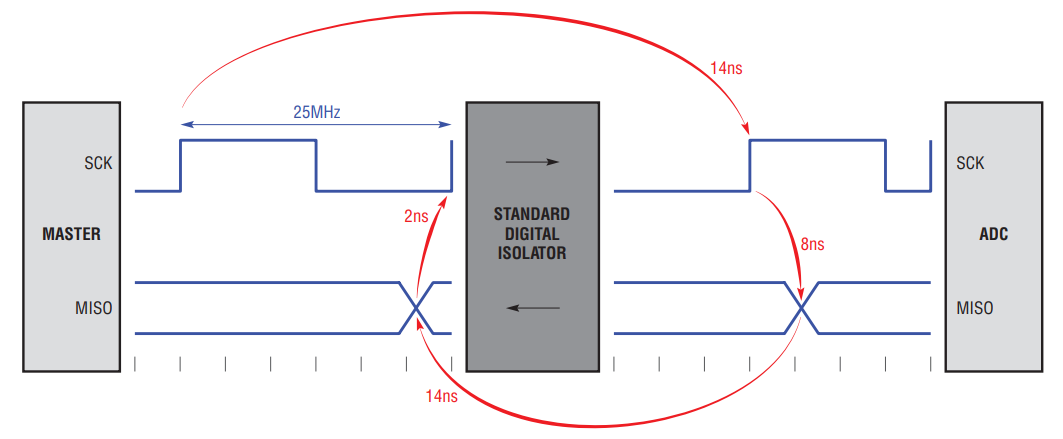

通用数字隔离器和专用SPI隔离器可用于隔离ADC,但除了3线或4线SPI端口外,此类解决方案还使用多个数字隔离器来支持转换启动或忙线状态信号等信号。标准数字隔离器在将SCK信号发送到隔离式SPI端口并等待MISO(SDO)数据返回时受到信号传播延迟的限制,然后才能出现SCK信号的下一个锁存边沿,如图2所示。除了来自ADC SPI端口的响应延迟外,这还增加了传播延迟。将所有延迟加起来,读取可能需要长达38ns的时间,而最初看起来很有吸引力 150Mbps数字隔离器。这会将有效SCK频率降低到25MHz或更低。

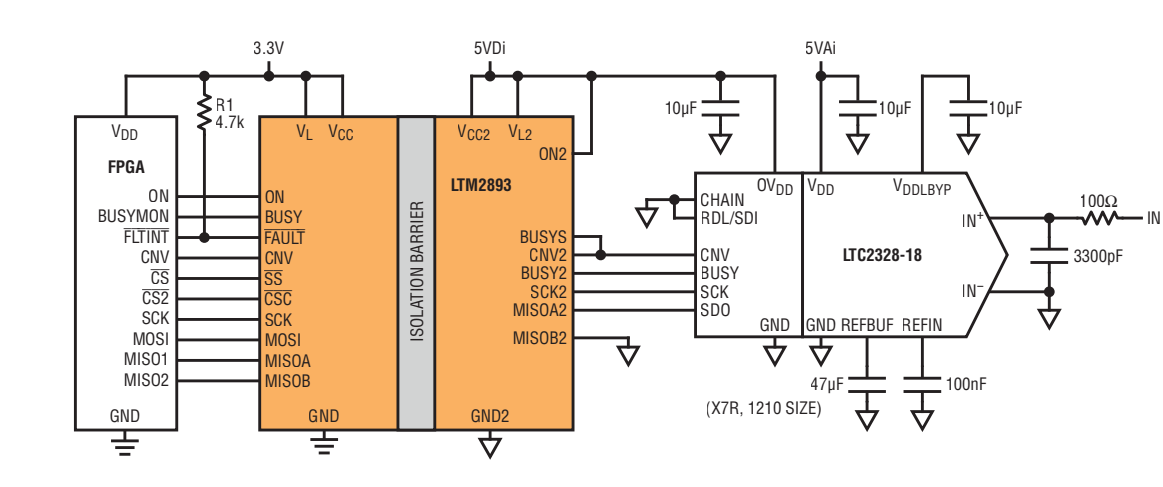

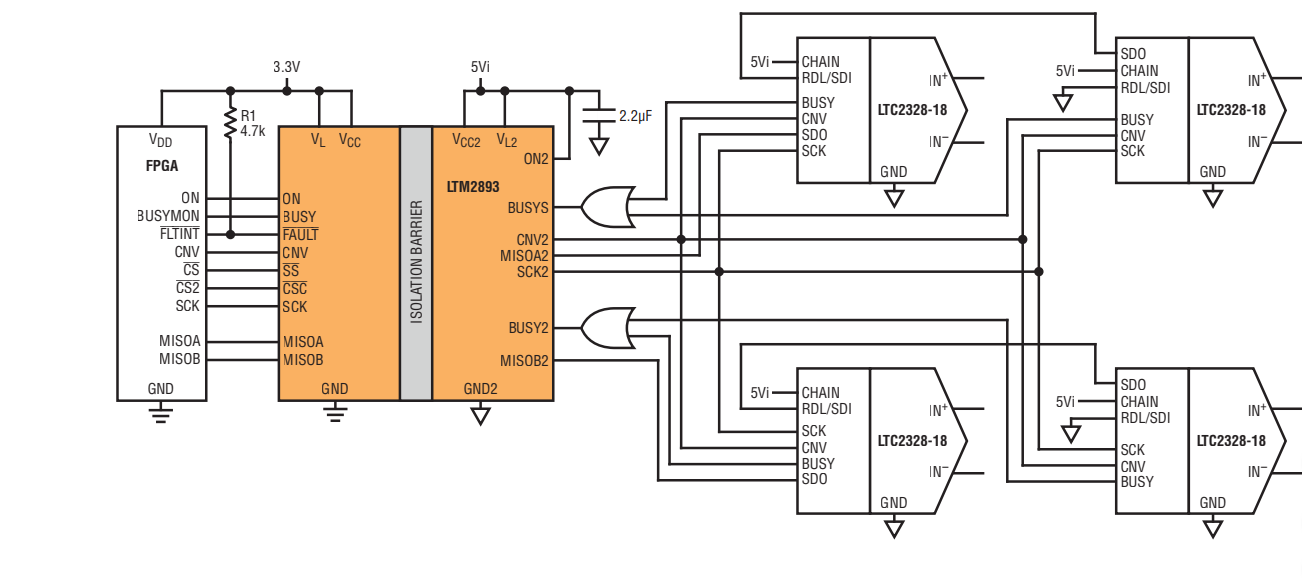

图1.典型应用。

图2.标准数字隔离器SPI读取延迟加起来可达38ns,从而将有效SCK频率降低至约25MHz。

流隔离器

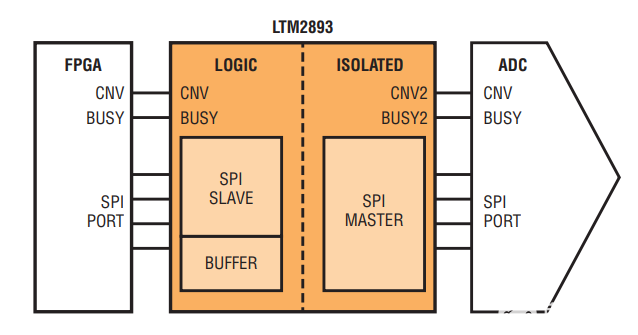

LTM2893 专为与 ADC 通信而设计,ADC 在隔离侧具有专用主 SPI 功能,在逻辑侧具有专用从功能(带缓冲器),如图 3 所示。

图3.ADC流隔离器可以有效地读取100MHz的ADC。

隔离式侧主控SPI引擎监控来自ADC的状态信号,并在繁忙信号变低后获取数据。此函数在转换开始后无需逻辑端交互即可启动。

逻辑侧从属SPI引擎包含一个缓冲寄存器,用于通过隔离栅从隔离侧接收数据。在ADC转换操作期间, 当缓冲寄存器从隔离侧SPI主机接收数据时,逻辑侧BUSY 信号变为低电平,指示SPI从端口已准备好读取。

LTM2893 具有用于获取和缓冲数据的逻辑功能,以最大限度地减少隔离栅上的数据交互。当两个ADC以100MHz读取时,数据在内部以200Mbps的速度流式传输。

SAR ADC 特定信号隔离

典型的SAR ADC具有转换开始(CNV)信号,用于启动将输入信号解析为数字结果,以及一个BUSY 信号,用于指示何时转换 正在进行中。LTM2893 专为 SAR ADC 量身定制,包括一个转换启动 (CNV) 和繁忙 (BUSY) 信号来管理与 ADC 的通信。转换开始信号通过 LTM2893 从 CNV 输入传输到上升沿的 CNV2 输出。

转换开始信号通过隔离器的传输具有低抖动,以最大程度地减少ADC采样孔径抖动的衰减。在CNV输入的上升沿之后,BUSY 信号保持高电平,当从隔离侧接收到本地SPI缓冲器中的数据时,BUSY 信号将变为低电平。一旦忙音信号变低,就可以读取本地SPI端口了。不带转换启动和忙音信号的 ADC 通过将 CNV2 和 BUSY2 引脚连接在一起,也与 LTM2893 兼容。

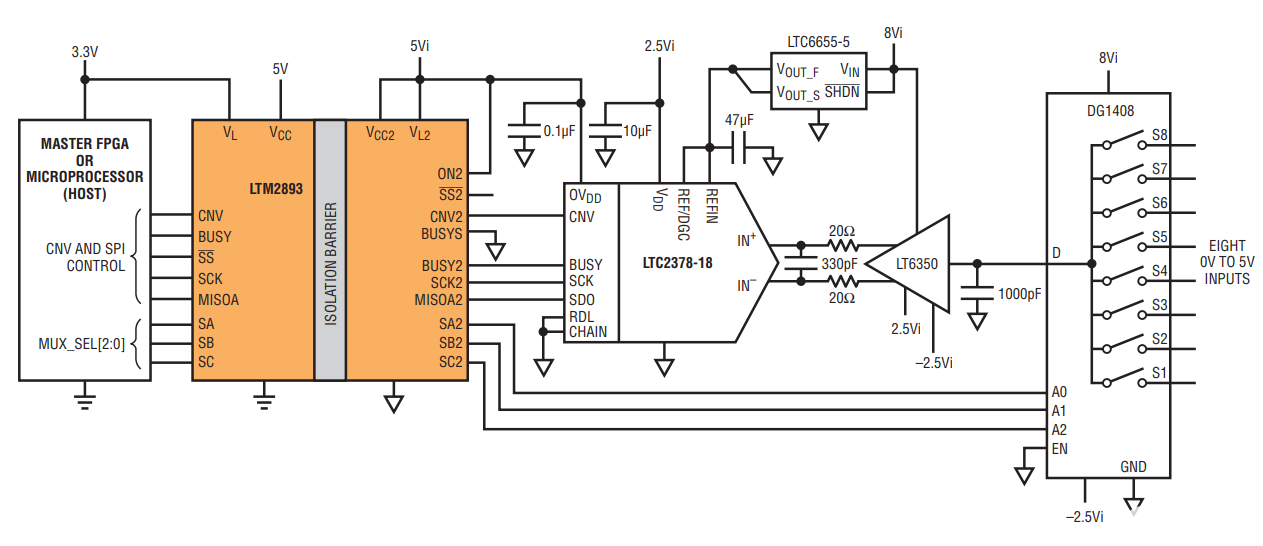

多路复用器控制信号的辅助通道

LTM2893 提供了三个信号,用于控制隔离栅沿任一方向的功能。这些信号非常适合控制模拟多路复用器(图 4)、可编程增益放大器等设备或 ADC 上的控制信号(如关断或复位)。选择信号不能在转换开始时或转换期间使用,但非常适合在开始转换之前更改设置或进行选择。配置寄存器允许沿三个选择信号的方向进行单独调整。

图4.LTM2893 选择控制一个模拟多路复用器的信号。

灵活性

工厂将 LTM2893 SPI 端口设定为 100MHz 的 SCK2 频率、一个 24 位数据字长和单个字数,该字数被选为可直接与 LTC2338、LTC2328 和 LTC2378 ADC 配合使用。SCK2频率设置是用于从ADC读取数据的串行时钟频率。逻辑侧SPI端口可在低至SCK2频率设置的1/128下工作。第二个片选择 (CSC) 支持写入 LTM2893 中的两个配置寄存器,从而选择 SPI 时钟速度、字长和字数。

SCK2频率在配置寄存器中有8个选项,支持100MHz至6.25MHz的ADC SPI端口。

24位数据字长设置适用于我们的许多通用SAR ADC,具有16位至24位结果和1Msps性能。此字长 设置定义隔离侧SPI主机从ADC检索并存储在逻辑侧缓冲器中的位数。从逻辑端SPI读取数据 端口不需要读取完整的字长。可以在配置寄存器中针对ADC的参数优化字长,以减少采样 通过从 32 位到 8 位的 8 种设置对时间进行计时或降低功耗。字数统计设置选择在单个转换周期中读取多个单词的数量。

隔离多个ADC

LTM2893 具有一个双通道读取端口 (MISOA、MISOB),因而能够同时读取两个 ADC 结果。两个 ADC 可连接至 LTM2893 的隔离侧,并共享 CNV2 和 SCK2 信号;BUSYS 和 BUSY2 信号独立连接到每个 ADC,而 ADC 的 SDO 输出分别连接 MISOA 和 MISOB。

| LTM2893 | LTM2893-1 | LTM2895 | |

| 功能 | SAR 模数转换器接口 | 带配置的 SAR ADC 接口 | DAC 或通用 SPI 接口 |

| SPI 通信 | 只读 | 针对 LTC2348 / LTC2358 ADC 系列的读/写 | 使用回读写入 |

| 最大 SCK 频率 | 100兆赫 | 100兆赫 | 100兆赫 |

| 有效通信信号数 | 9(4 个 SPI,5 个控制) | 10(5 个 SPI,5 个控制) | 9(5 个 SPI,4 个控制) |

此外,利用支持链接的 ADC(图 5),单个 LTM2893 最多可连接 8 个 ADC。读取两个以上的并行 ADC 需要写入 LTM2893 中的配置寄存器以选择器件数量。配置寄存器允许选择两个、四个、六个或八个器件,通过两个MISOA和MISOB SPI输出访问。

图5.链接配置。

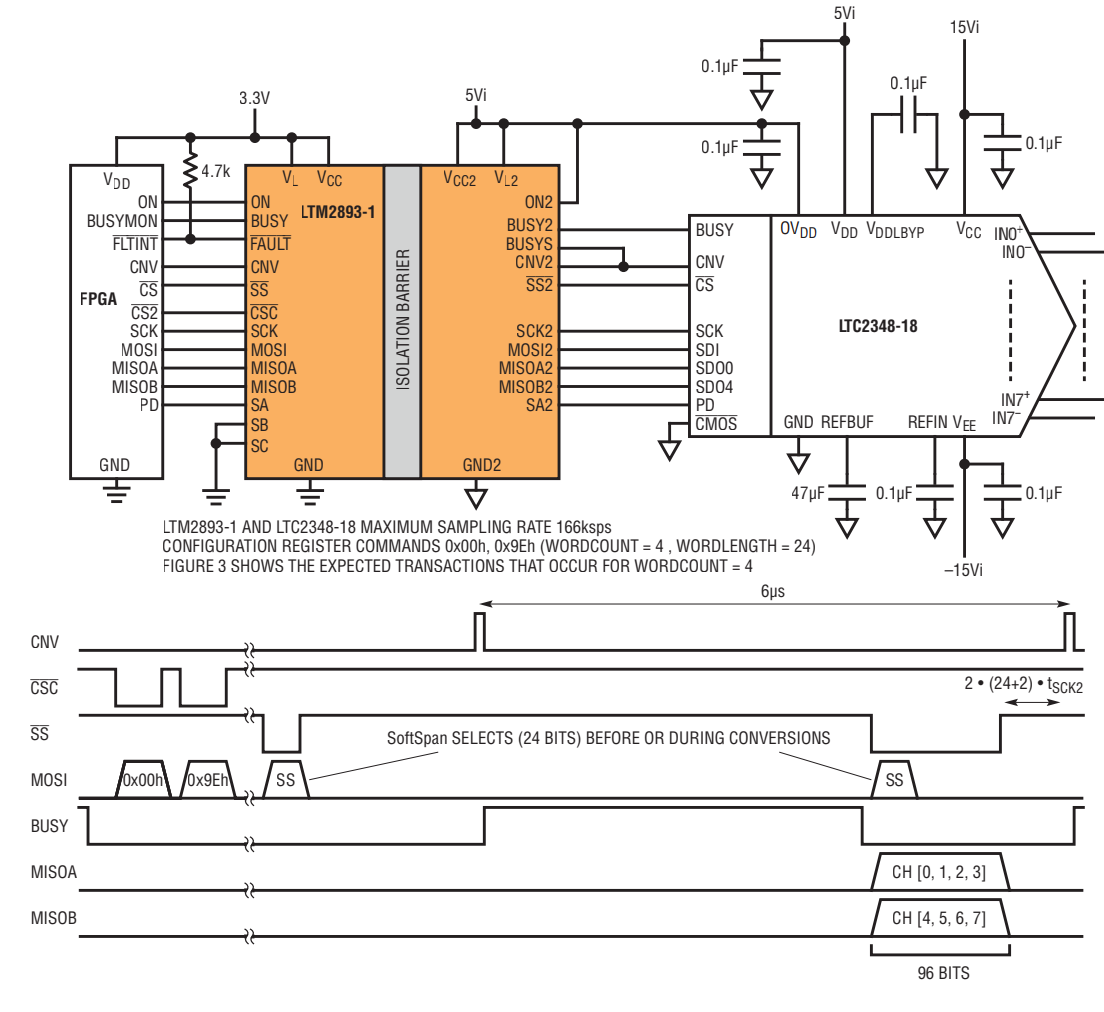

隔离 LTC2348 多路复用 ADC 与 LTM2893-1

大多数ADC只需要一个具有读取能力的SPI端口。LTM2893 专用于读取具有一个只读 SPI 端口的 ADC。LTM2893-1 专用于具有配置寄存器的 ADC,例如 LTC2348 同步采样 ADC 系列,如图 6 所示。LTM2893-1 读写 SPI ADC 隔离器支持配置 SoftSpan™寄存器和读取来自LTC2348的所有多路复用数据。LTC2348 ADC 系列具有 8 个模拟输入,这些输入可同时采样、顺序转换并通过一个 8 输出 SPI 端口进行访问。将端口 0 和 4 连接到 LTM2893-1 的 MISOA2 和 MISOB2 输入,并将 LTM2893-1 配置寄存器设置为字长 24,器件计数为 8,则每个转换转换将转换两个通道(每个结果)转移 4 个结果。向 LTC2348 添加一个隔离器会对采样速率造成很小的损失,从而将 200ksps 的理想速度降低到 166ksps。

图6.LTM2893-1 和 LTC2348-18。

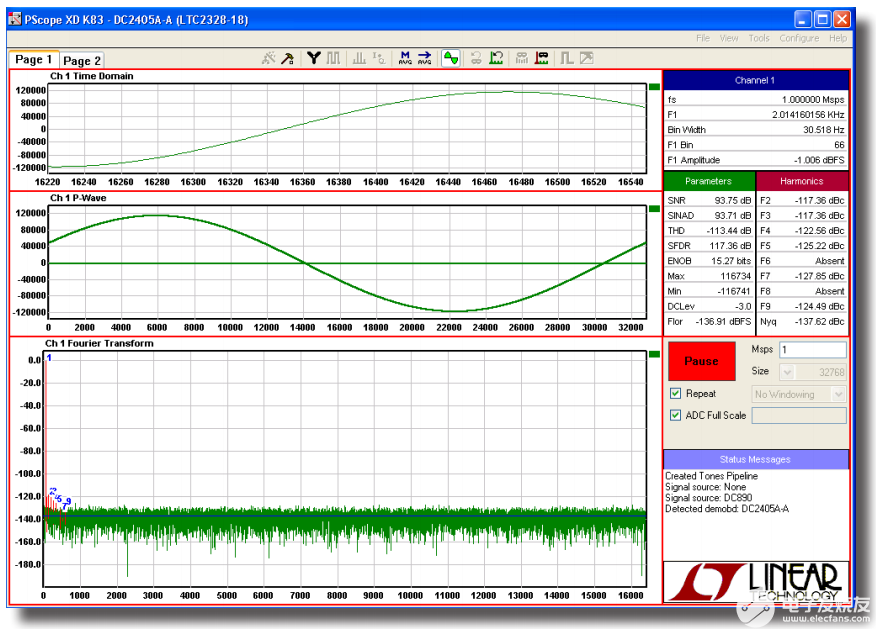

系统性能

添加任何数字隔离器都可能引入时序抖动,从而导致性能下降。LTM2893 专为转换开始信号设计了一个低抖动路径,以最大限度地降低信噪比性能。采用 LTC2328-18 的 LTM2893 的系统性能与 LTC2328-18 的独立性能相似。为了说明这种性能,图7显示了DC2405A演示板使用我们的PScopop在–1dBFS下捕获2kHz输入的曲线。™应用。

图7.DC2405A演示电路的PScope图。

结论

LTM2893 是一款专为 ADC 应用而设计的全集成隔离解决方案。LTM2893 可处理通过隔离栅访问 ADC 所需的所有信号,并将性能下降降至最低。LTM2893 在与 ADC 接口时满足 100MHz SPI 操作要求。相比之下,其他零碎的隔离解决方案必须降低时钟频率以克服传播延迟。与其他 SPI 隔离解决方案相比,LTM2893 的灵活接口使其能够隔离多个 ADC,从而减少了整体组件数量和系统复杂性。由于它针对ADC进行了优化,设计人员可以轻松地将其添加到任何需要鲁棒接口的解决方案中。

审核编辑:郭婷

-

用于Raspberry Pi的高分辨率流媒体2022-08-11 904

-

单片机内置ADC实现高分辨率采样的方法2021-12-08 1652

-

太秀了!单片机内置ADC实现高分辨率采样?2021-11-25 1113

-

如何设计高速高分辨率ADC电路?2021-04-23 2791

-

ADC信噪比要怎么分析?高速高分辨率ADC电路要怎么实现?2021-04-14 2813

-

高分辨率ADC解决实际难题2019-09-27 2116

-

使用单5V电源的高分辨率视频解决方案2019-05-16 2214

-

高分辨率、低漂移和精密称重天平电子秤解决方案2018-12-19 3278

-

探究驱动高分辨率 ADC 的方法2018-06-28 4712

-

驱动高分辨率 SAR ADC2018-06-07 5382

-

高分辨率 1Msps SAR 模数转换器隔离式解决方案2018-06-04 5999

-

高分辨率ADC的板布线分析2017-12-06 1154

-

高分辨率模数转换器(ADC)概述2011-01-01 4125

-

高速高分辨率ADC电路设计及信噪比分析2010-07-06 1999

全部0条评论

快来发表一下你的评论吧 !