Marvell交换芯片介绍之MII、MDIO

电子说

描述

该芯片作为PHY和SERDES使用

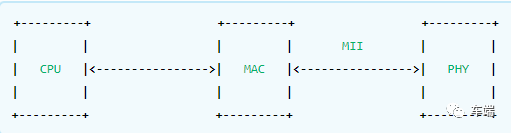

MII 是一个标准接口,用于连接 MAC 和 PHY。MII 是 IEEE-802.3 定义的以太网标准, MII 接口可以同时控制多个 PHY。

MII包含两个接口:

1.一个数据接口,用户 MAC 和 PHY 之间收发 Ethernet 数据 2.一个管理接口,这个管理接口通常称为 MDIO,MIIM 或者 SMI。 这个接口用于 MAC 从 PHY 读取相关管理寄存器的值,或者往 PHY 管理寄存器上写入数据。

MDIO

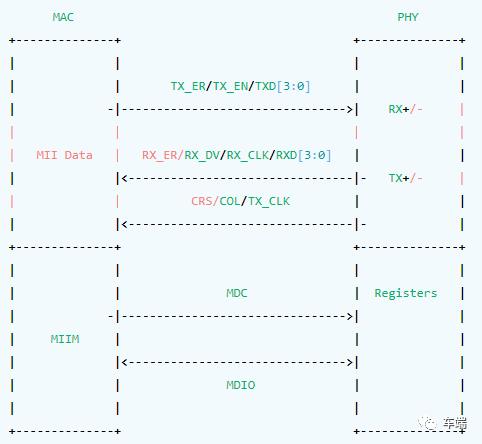

MDIO 也被称为 MIIM,或者 SMI,它是 IEEE802.3 定义标准 MII 接口的一部分,用于 MAC 配置 PHY。MDIO 具有两个信号线,分别如下:

1. MDC 时钟线:MDIO 的时钟信号,由 MAC 驱动 PHY 2. MDIO 数据线:双向数据线,用于在 MAC 和 PHY 之间传输配置信息

MDIO 总线只支持 MAC 作为主设备,PHY 作为从设备。MIDO 支持两种时序,分别为 Clause 22 和 Clause 45.

MDIO接口最初是由IEEE RFC802.3中的22号条款定义的,在最初的定义中,一个单独的MDIO接口可以访问32个不同的PHY设备中的32个寄存器,这些寄存器提供状态和控制信息,例如:连接状态、传输速度能力、当前选择的传速、低压消耗时的下电情况、全双工还是半双工、自动协商、错误提示以及反馈信息等等。

为了满足10G以太网设备的普及发展,在IEEE 802.3ae 的45号条款中为MDIO接口提供了额外的规范:

1)能够通过32个端口访问32个不同设备的65536个寄存器;

2)为访问10G以太网提供额外的OP码和ST码,从而可以直接访问寄存器地址;

3)端到端的报错信号;

4)环回模式控制;

5)低压电气标准。

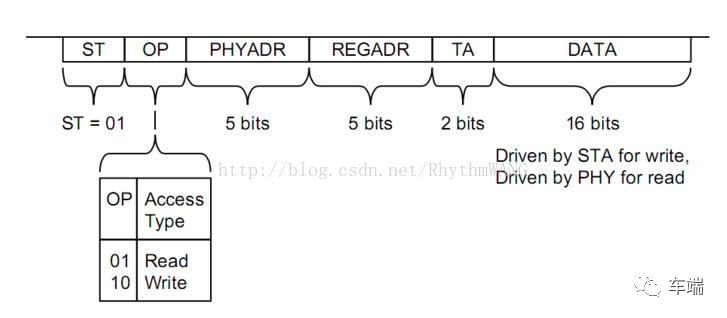

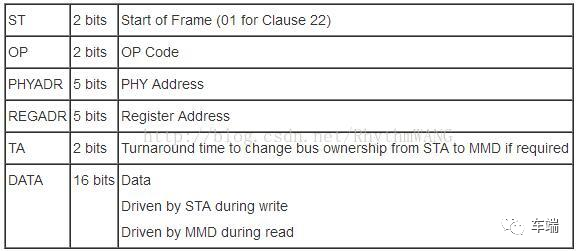

22号条款

22号条款的MDIO通信的帧格式定义如下:

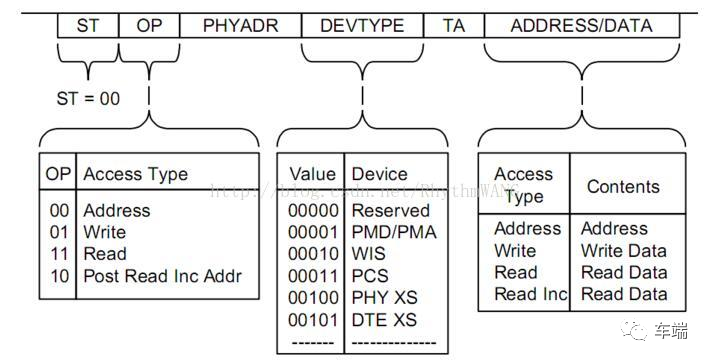

45号条款

为了弥补22号的条款中定义的缺陷,45号条款中增添了对低压设备的支持,最低可到1.2V,同时扩充了帧格式,能够访问更多的设备和寄存器。

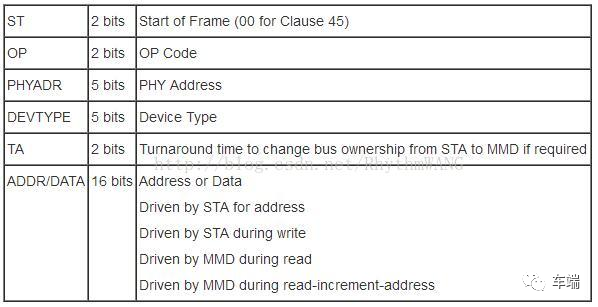

45号MDIO通信帧格式如下:

第45号条款的主要变化是如何访问寄存器。在第22中,一个单独的帧指定要读或写的地址和数据,同时完成了这些工作。45号中改变这种范式,第一个地址帧发送到指定的MMD和寄存器,然后发送第二帧来执行读或写。

工作模式

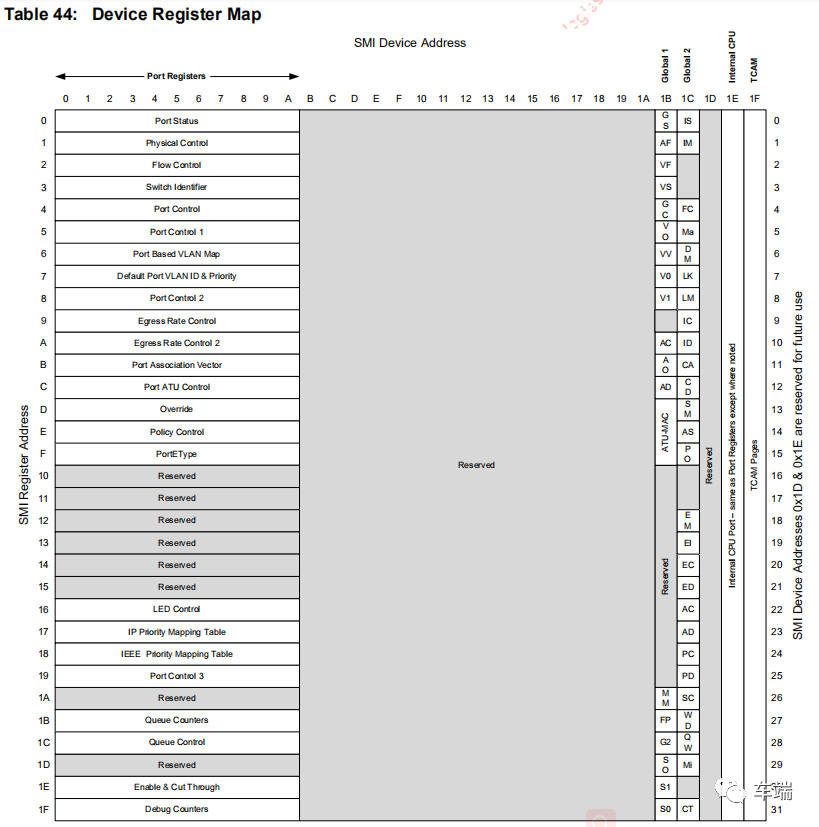

该芯片有两种寻址模式:单芯片寻址和多芯片寻址。

多芯片寻址

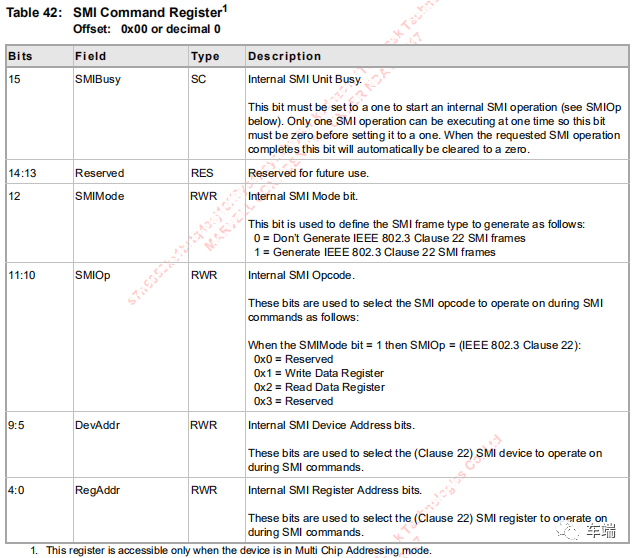

对于多芯片寻址,需要给芯片设置一个非零的SMI地址(ADDR[4:0]的反码)。在多芯片寻址模式下,仅有两个寄存器(0x00:SMI Command Register 0x01:SMI Data Register)能够使用,内部各PORT的寄存器均由这两个寄存器间接访问。

通过向SMI Command Register的[9:5]写入内部SMI设备地址,[4:0]写入内部SMI寄存器地址来访问各个Port的内部寄存器,[11:10]决定决前是写入还是读出操作。

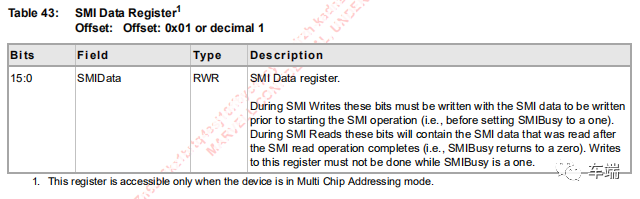

通过向SMI Data Register的[15:0]位写入或读取SMI Command Register设定的寄存器内容。

单芯片寻址

对于单芯片寻址,其SMI地址为0x00(针对整个芯片),即ADDR[4:0]=0x1F。

在单芯片寻址模式下,每个Port都有各自的SMI地址(针对内部每个Port),Port0-Port9对应的SMI地址分别为0x0-0x9(直接访问),port10对应0xA。

若Port0、1、2等接有外部PHY,则必须使用以下SMI地址,0x00对应Port0,0x01对应Port1,这样PPU才能自动的轮询各个PHY获取各自的连接状况,速度,双工情况,流控状态等信息,这些外部PHY需要使用Global2 offset 0x18、0x19进行访问。对于Port3a、Port4的内部PHY地址映射为0x03、0x04;Port9、Port10的内部SERDES映射为0x9、0xa,同样的,也是需要使用Global2 offset 0x18、0x19进行访问。

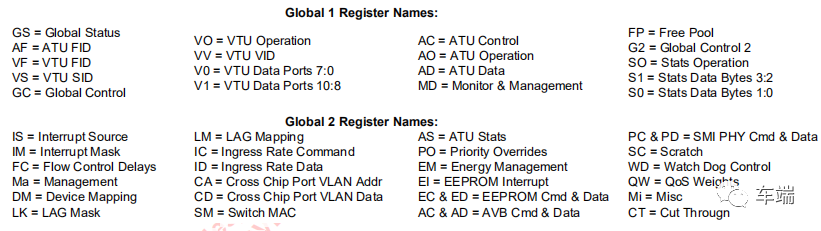

Global2 寄存器的 Offset24,25 寄存器

前文提到,两个非常重要的寄存器,即Global2 offset 0x18、0x19寄存器,在单芯片寻址模式下PHY和SERDES寄存器的访问都必须通过这两个寄存器间接访问。

Global2 offset 0x18 (SMI PHY Command Register)寄存器

bit[12]指定了帧协议是22号时序还是45号时序。22号协议下,与多芯片存储能够访问的Command Register寄存器一样,[9:5]写入SMI设备地址,[4:0]写入SMI寄存器地址来访问各个Port的内部寄存器,[11:10]决定当前是写入还是读出操作。45号协议,[9:5]指定port,[4:0]指定设备类别。

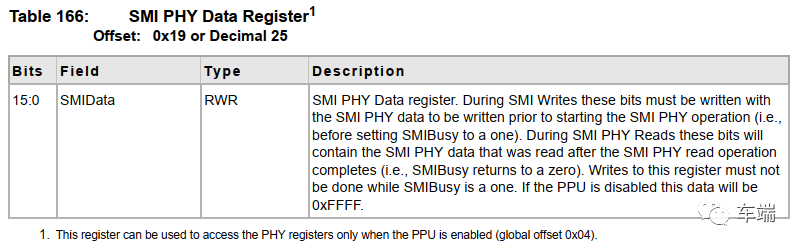

Global2 offset 0x19 (SMI PHY Data Register)寄存器

与SMI Data Register相同,通过[15:0]位写入或读取SMI Command Register设定的寄存器内容。

在45号协议下,第一个地址帧发送到指定的MMD和寄存器,我们要把PHY Command Reg中的[11:10]置为0x00=write Address register,即在第一个帧中的最后16位数据中,指定要操作的寄存器的地址。随后在第二个数据帧中,要把PHY Command Reg中的[11:10]置为0x01=write data register,即第二个帧中的最后16位写入的是数据。

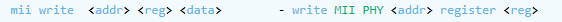

Uboot 中访问 MDIO (SMI/MIIM)

项目开发中,经常要在 uboot 阶段通过 MDIO 总线去配置 PHY 或者 SWITCH。

更多指令

示例:

6390x config **配置端口10** //0xa:P10 //0x34a: // bit[3:0]-0xa-接口配置模式-SGMII // bit[6] -0x1-EEE(Energy Efficient Ethernet)Enabled // bit[9:8]-0x3 = 10Gb or 2500Mbps miiwrite 0xa 0 0x34a **配置端口5** //p5 p177 p355 //addr:0x1c //regi:0x19 SMI Data register //regi:0x18 SMI Command register //在45号条款中 //第一个地址帧发送到指定的MMD和寄存器,然后发送第二帧来执行读或写。 miiwrite 0x1c 0x19 0x2000 //将数据0x2000写到PHY data寄存器0x19中 miiwrite 0x1c 0x18 0x82a4 //将数据0x82a4写到PHY Command寄存器中 //0x82a4 //bit[15]:0x1——此位在首次操作SMI时,要置为1,并且在操作SMI完毕之后会自动清零 //bit[14:13]:0x0——内部访问-用于访问包含在这个设备中的内部PHYs和/或serde。 //bit[12]:0x0——SMI MODE——Generate IEEE 802.3 Clause 45 SMI frames //bit[11:10]:0x0—— Write Address Register //bit[9:5]:写入SMI设备地址-0x15——Port 10 Lane 1 = Port 5 & its registers are accessed at SMI address 0x15 //bit[4:0]:device class(clause 45) //第一个地址帧的后16位为Addr,即data register中的数据0x2000 miiwrite 0x1c 0x19 0x8140 //将数据0x8140写到PHY data寄存器0x19中 miiwrite 0x1c 0x18 0x86a4 //将数据0x86a4写到PHY Command寄存器中 ////bit[11:10]:0x01—— Write data Register //第二个帧,后16位为要写入的数据,即data register中的数据0x8140 编辑:黄飞

-

飞凌嵌入式ElfBoard ELF 1板卡-uboot移植之网络修改-MDIO接口2025-06-16 1021

-

以太网交换机芯片概述2011-11-06 24343

-

Marvell交换芯片88E6097的电路设计原理2013-01-31 36969

-

求助,用过marvell88e6097交换芯片的大神2015-12-22 12550

-

am3352的网口配置成mii模式网络ping不通2018-05-15 4629

-

具有单MII/RMII/Turbo MII支持LAN9303的以太网交换机2020-05-18 5469

-

具有双RMII或单MII / RMII / Turbo MII接口的全功能三端口以太网交换机2020-08-17 3799

-

SDIO wifi Marvell8801是什么2021-07-28 1367

-

自己实现SDIO wifi Marvell8801/Marvell88w8801驱动 介绍(一) ---- 芯片介绍 精选资料推荐2021-07-29 2440

-

最近Marvell将 推出支持OpenFlow的交换机2011-06-23 1372

-

STM32F103驱动SDIO wifi Marvell8801/Marvell88w8801 介绍(十) ---- 移植TCP/IP协议栈LWIP2021-11-24 1464

-

交换芯片只适用在交换机上的?2022-11-09 1384

-

以太网PHY芯片的MII接口和MDIO接口介绍2023-07-26 18745

-

Marvell交换芯片是什么2024-03-16 3663

-

简单认识Marvell交换芯片2024-03-21 3086

全部0条评论

快来发表一下你的评论吧 !