基于数字解调器和JESD204B接口的多通道超声接收系统设计

描述

作者:Hugh Yu, Gina Kelso, and Ashraf Saad

随着医疗超声在医疗诊断领域的广泛应用,医生对超声图像系统图像质量的要求越来越高,而提高图像质量的关键技术之一是提高接收通道的信噪比。随着系统中接收通道数量的增加一倍,信噪比理论上应该提高3 dB。因此,增加系统通道数量已成为加强信噪比的最简单有效的方法。目前,128通道已成功成为中高级医疗超声设备的主流配置,192通道或更多通道将成为高端系统的下一个趋势。随着通道数量的增加,模拟前端和后端数字处理以及物理连接之间的数据速率急剧增加。它们还会导致数字电路器件接口的数量、处理能力、成本、整个接收器电路的设计复杂性以及相应的功耗增加。目前,超声系统使用射频(RF)波束成形。输出数据速率完全取决于模数转换器(ADC)的分辨率、采样速率和通道数。同时,模拟前端(AFE)通常使用低压差分信号(LVDS)输出接口。八通道AFE需要八对LVDS数据线以及一对数据时钟和帧时钟。对于拥有超过 128 个通道的系统,有大量的数据和物理连接。

本文介绍了一种基于八通道AFE的数字解调器和JESD204B接口的超声接收通道设计方案,有效解决了上述系统数据速率大、物理连接复杂带来的设计难题。

系统架构

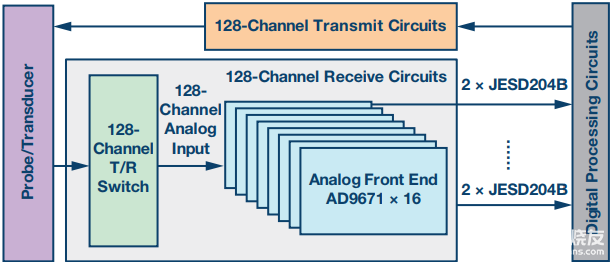

超声系统由探头(换能器)、发射电路、接收电路、后端数字处理电路、控制电路、显示模块等组成。图1是带有JESD204B接口的128通道超声系统发送/接收路径框图。数字处理模块通常包括现场可编程门阵列(FPGA),根据系统的当前配置和控制参数生成相应的波形。然后,发射电路的驱动器和高压电路产生高电压以激励超声换能器。超声换能器通常由压电陶瓷换能器(PZT)制成。它将电压信号转换为超声波,进入人体,同时接收组织产生的回波。然后将回波转换为电压信号并传输到发送/接收(T/R)开关电路。T/R开关电路的主要目的是防止高压发射信号损坏低压接收模拟前端。经过信号调理、增益和滤波后的模拟电压信号被传递到AFE的集成ADC,然后转换为数字数据,然后通过JESD204B接口传输到后端数字部分进行相应的处理,最终创建超声图像。接收通道由一个128通道T/R开关电路、一个带数字解调器和JESD204B接口的16八通道超声AFE器件以及一个带JESD204B接口的FPGA组成。

图1.128通道超声系统框图。

AD9671: 八通道超声AFE,内置数字解调器和JESD204B接口

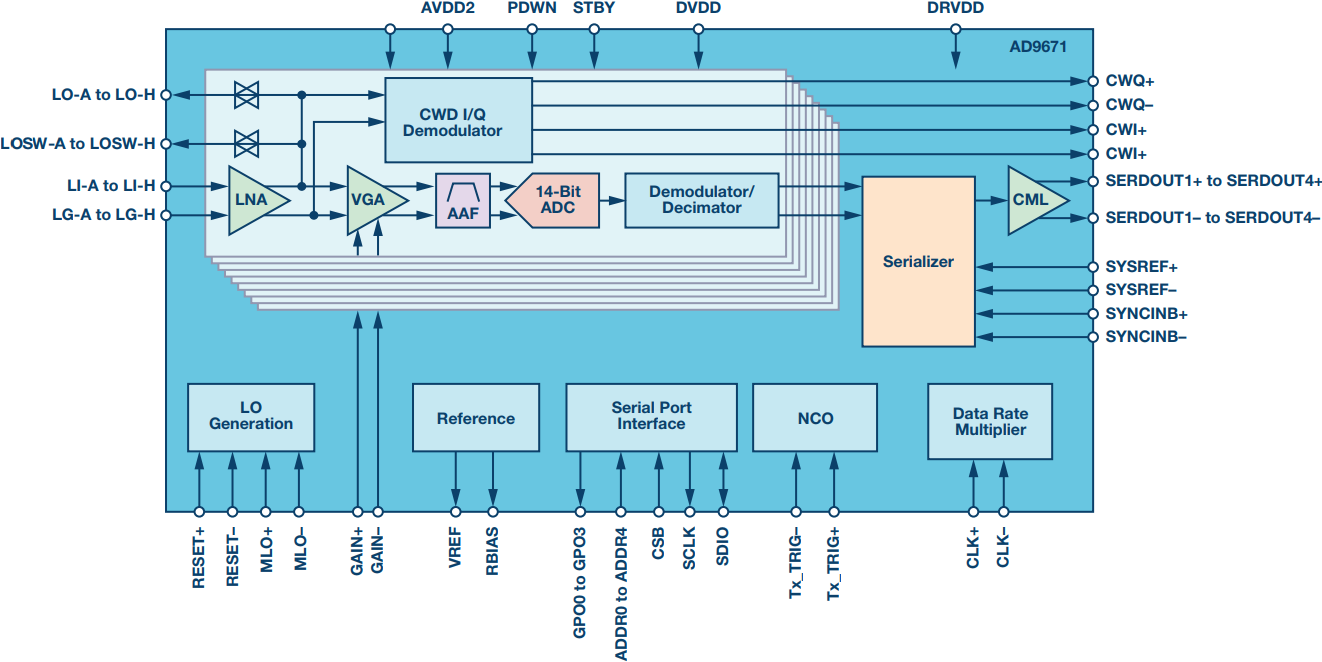

AD9671是八通道超声AFE,内置ADI公司(ADI)的数字解调器和JESD204B接口,被选用于该超声系统接收电路。它包含八个通道,包括一个带低噪声放大器(LNA)的可变增益放大器(VGA)、一个具有可编程相位旋转功能的连续波(CW)谐波抑制I/Q解调器、一个抗混叠滤波器(AAF)、一个14位ADC、一个用于数据处理和带宽降低的数字解调器和抽取器,以及JESD204B接口。图2是AD9671的功能框图。

图2.AD9671功能框图

数字解调器

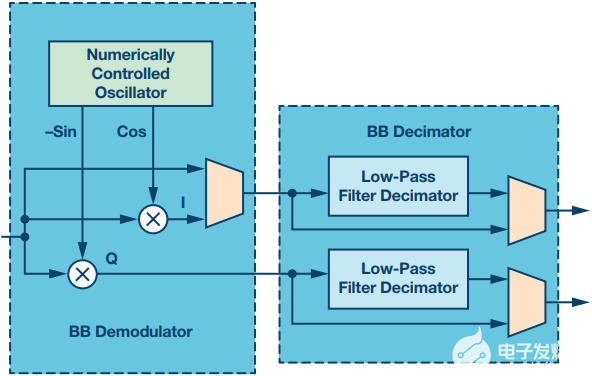

数字解调器由基带解调器和基带抽取器组成。解调器将RF信号下变频为基带正交信号。抽取器减少了多余的过采样。图3是数字解调器的框图。

图3.数字解调器框图。

JESD204B接口

AD9671数字输出符合JEDEC标准JESD204B,数据转换器串行接口。AD9671支持单通道、双通道或四通道接口。它可以连接到最大数据输出速率为 5.0 Gbps 的 FPGA。

系统设计与应用

本节介绍了AD9671多通道超声系统的接收电路设计,并进一步分析了使用数字解调器和JESD204B接口的优势。

接收电路设计

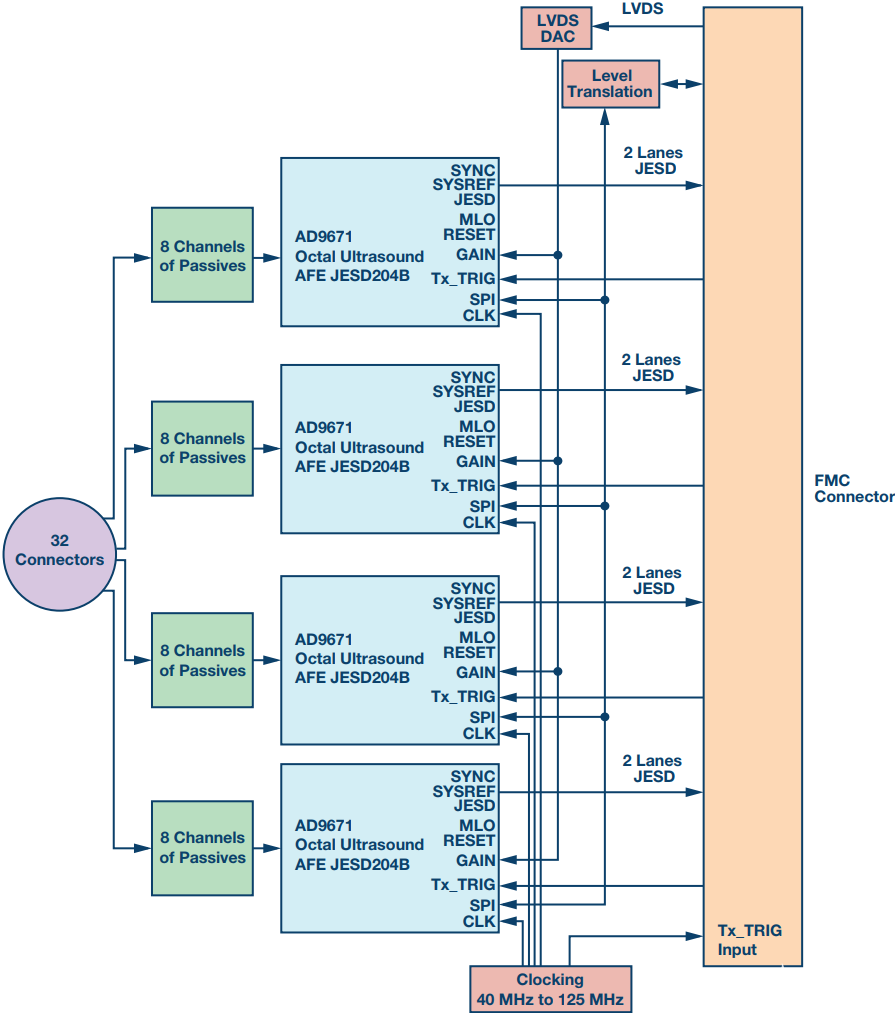

图4所示为32通道接收电路模块原理图,可用于验证基于AD9671的系统可行性。通过四个这样的模块,可以配置超声系统的128通道接收电路。该模块可用于执行数据采集和处理,并通过专用FMC连接器连接到FPGA来实现超声波信号处理和图像生成。

图4.接收电路的顶层原理图。

数字解调器应用分析

对于 128 通道超声系统,如果使用采样率为 40 MSPS 的 14 位 ADC,并且使用 RF 波束成形算法,则 ADC 输出和波束成形 FPGA 之间的数据速率为 14 × 40 × 128 = 71.68 Gbps。

下面分析了使用数字解调器的好处。

RF信号的基带解调器执行正交解调。这可以通过将ADC输出的数字化RF信号乘以复正弦信号

来实现,其中fd是可以接近超声换能器中心频率的解调频率,以将中心频率下变频至0 Hz左右。输出信号是一个复数信号,由其I(同相)和Q(正交相位)表示。探头的中心频率和所有感兴趣的频段信号被降档到大约0 Hz,用滤波器和抽取器滤除不需要的频率分量,以保留对生成超声图像有用的频段信息。

对于中心频率为3.5 MHz的探头换能器,经过基带解调和抽取后,具有16位格式I和Q数据输出,数据速率现在为2(I&Q)×16位×3.5 MHz×128通道= 14.336 Gbps。 与原来的71.68 Gbps相比,即使I和Q通道同时输出,数据速率也降低了80%。

JESD204B接口应用分析

就当前多通道超声系统应用中的AFE和ADC而言,LVDS已经取代了并行输出接口。然而,对于128通道或更高的超声系统,ADC输出的大量LVDS线连接仍然是设计工程师头疼的问题。对于LVDS,当前超声系统中有一个八进制AFE有10对电线。对于 128 通道超声系统,需要将 128/8 × 10 = 160 对 LVDS 数据和时钟线连接到 FPGA。

下面分析了使用JESD204B接口的好处。

由于JESD204B使用16位数字输出格式并使用8B/10B编码,因此具有14位分辨率、40 MSPS ADC的八通道AFE的输出数据速率为20 ×40 × 8 = 6.4 Gbps。AD9671 JESD204B接口每通道的最大数据速率为5.0 Gbps,因此只需两对数据通道即可实现8通道AFE数据输出。因此,对于 128 通道超声系统,与 160 对 LVDS 线相比,只需要 128/8 × 2 = 32 对输出数据通道;消除了 80% 的物理接口路由。

结论

本文介绍了一种基于AD9671(具有数字解调器和JESD204B接口的八通道AFE)的多通道超声系统设计。本文分别有效分析了在超声系统中使用这种带有数字解调器和JESD204B接口的AFE的应用优势和优势。与目前大多数RF波束成形和LVDS接口设计相比,模拟前端和数字处理部分之间的数据速率和接口路由都降低了80%。如果在分析中将这两种方法组合在一起,物理连接将进一步减少。因此,本文介绍的系统设计可以通过减少数据接口布线所需的电路板面积、计算复杂性要求以及系统设计成本,有效地简化电路设计和软件处理复杂性。

审核编辑:郭婷

-

JESD204B使用说明2024-12-18 3127

-

JESD204B的常见疑问解答2024-01-03 825

-

JESD204B的优势2022-11-23 774

-

JESD204B协议介绍2022-11-21 948

-

宽带数据转换器应用的JESD204B与串行LVDS接口考量2021-11-03 3297

-

AD9671:带数字解调器的八进制超声波AFE,JESD204B数据表2021-04-29 941

-

JESD204B协议有什么特点?2021-04-06 2113

-

FPGA高速数据采集设计之JESD204B接口应用场景2019-12-03 5250

-

JESD204B串行接口时钟的优势2019-06-19 3742

-

串行LVDS和JESD204B的对比2019-05-29 3176

-

JESD204B的系统级优势2018-09-18 2409

-

JESD204B标准及演进历程2017-11-18 15040

-

新型集成数字解调器和JESD204B接口的超声模拟前端2017-11-16 1722

全部0条评论

快来发表一下你的评论吧 !