设计从直流到宽带的高速模拟信号链

描述

如今,在转换器领域风靡一时的是GSPS ADC,也称为RF ADC。由于市场上有如此高的采样率转换器,与五年前相比,奈奎斯特打开了 10×。关于使用RF ADC的优势以及如何使用它们进行设计并以如此高的速率捕获数据,已经进行了大量讨论。谢谢JESD204x财团。但有一个考虑因素似乎被遗忘了,即低直流信号。

在高性能模数转换器(ADC)之前设计输入配置或前端对于实现所需的系统性能始终至关重要。通常,重点是捕获宽带频率,例如大于1 GHz的频率。然而,在某些应用中,直流或近直流信号也是必需的,最终用户可以欣赏,因为它们也携带重要信息。因此,优化整体前端设计以捕获直流和宽带信号需要一个直流耦合前端,该前端一直通向高速转换器。

由于应用的性质,需要开发有源前端设计,因为用于将信号耦合到转换器的无源前端和巴伦本质上是交流耦合的。本文将概述共模信号的重要性以及如何正确对放大器前端进行电平转换,以实际系统解决方案为例进行。

共模:概述

当客户对共模参数及其与器件的关系缺乏了解时,许多客户支持问题仍然来自客户。ADC数据手册规定了模拟输入的共模电压要求。关于这个问题没有太多的详细信息,但必须保持适当的前端偏置,以便在满量程下实现ADC的额定性能。

具有集成缓冲器的ADC通常具有电源一半的内部偏置共模(CM)电平加上二极管压降(AVDD/2 + 0.7 V)。该电路不需要外部电路来偏置,但必须保持该电路才能正确使用转换器。对于无缓冲(开关电容输入)转换器,共模偏置通常为模拟电源的一半,即AVDD/2。这可以通过多种方式从外部提供。一些转换器具有专用引脚,允许设计人员通过连接到模拟输入的几个电阻提供偏置。或者,设计人员可以将内部偏置连接到变压器的中心抽头,或者可以使用模拟电源旁的电阻分压器(模拟输入的每个支路到 AVDD 和地的电阻)。在使用转换器的V之前,请查看制造商的数据手册或应用支持小组裁判引脚,因为许多基准电压源无法在没有外部缓冲器的情况下提供共模偏置。这很诱人,因为您需要的CM电压就在那里并且很方便,但请注意 - 不要这样做。

如果未提供或维持共模偏置,转换器将产生增益和失调误差,从而影响整体测量。转换器可能会提前削波,或者根本不削波,因为无法达到转换器的满量程。在转换器前面连接放大器时,共模偏置尤其重要,尤其是在应用需要直流耦合时。检查放大器的数据手册规格,确保放大器能够满足转换器的摆幅和共模电源要求。转换器一直在推动更小的几何工艺,因此需要降低供应量。采用1.8 V电源时,如果需要直流耦合,放大器需要0.9 V共模电压。具有3.3 V至5 V电源电压的放大器可能无法保持如此低的电平,但较新的低压放大器可以,或者设计人员可以使用分离电源并在VSS引脚上使用负电源轨。但是,在执行此操作时,请记住,其他引脚也可能需要连接到负电源轨。请查阅产品的数据手册和/或直接应用支持,了解详情。

共模:已定义

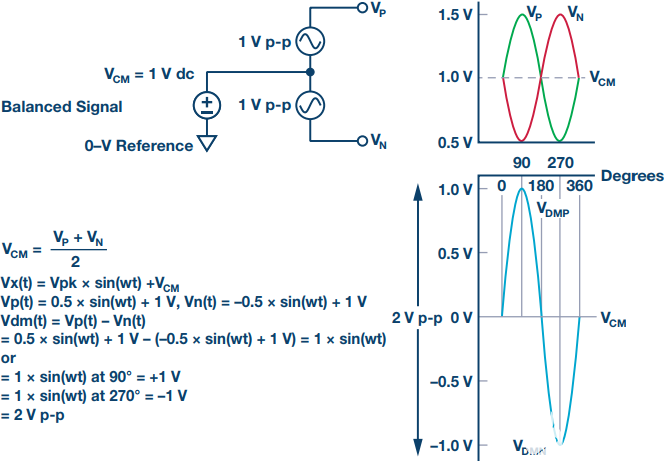

让我们从定义什么是CM电压开始。图1显示了转换器如何看到差分和共模信号。CM电压只是信号围绕的中心点移动——见图1。您也可以将其视为新的中心点或零码 - 放大器,CM建立在输出上,通常通过VOCM引脚或类似引脚。但要小心,这些引脚也有一定的电流和电压范围要求。最好查看放大器数据手册和/或使用不会加载电路内任何相邻电路或参考点的鲁棒偏置点。不要简单地断开转换器的基准电压引脚 (V裁判),通常是转换器满量程的一半。它可能无法提供足够的准确性偏差。谨慎的做法是查看转换器数据手册上的引脚规格。通常,具有1%电阻容差的简单分压器和/或缓冲驱动器等功能可以为放大器正确设置此CM偏置。

图1.差分和共模信号示例。

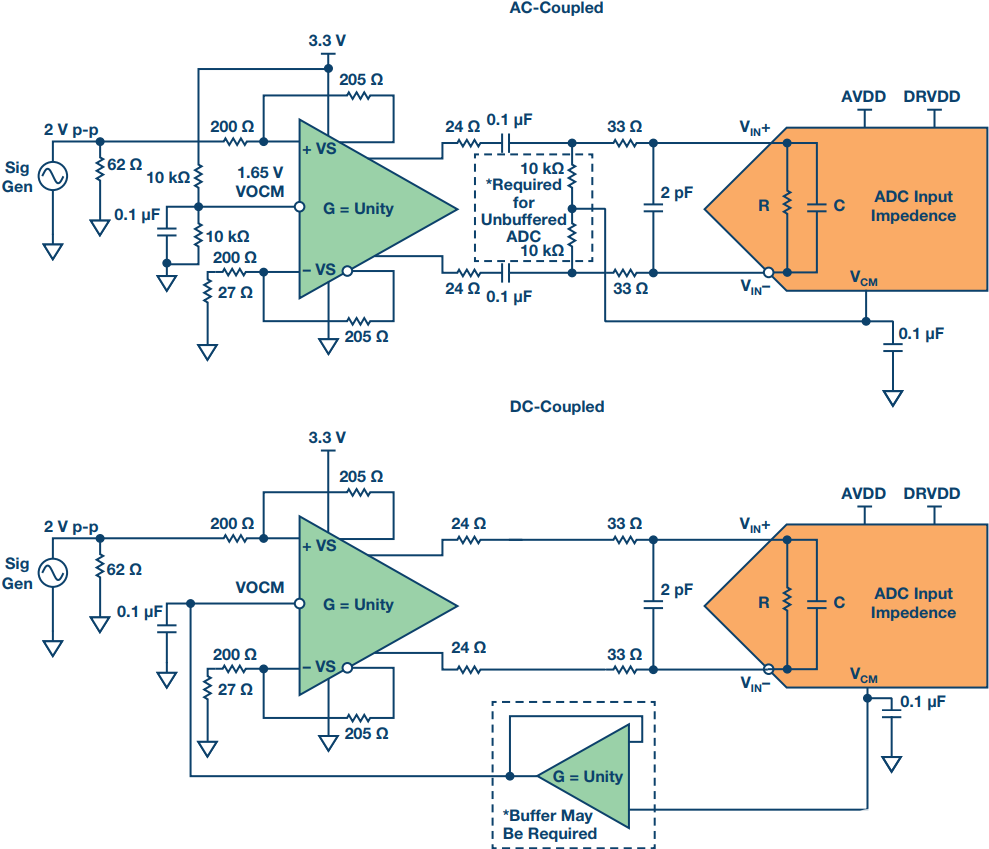

在表1中,下面列出了如何连接每个应用的放大器和转换器的快速摘要,以及图2所示的一些适当电路示例。

图2.放大器/转换器前端的交流耦合与直流耦合应用示例。

| 应用 | 放大器 | 模数转换器 | 笔记 |

| 直流耦合 | 在 DS 指定的限制范围内设置 VOCM。使用 ADC V 的分压器或缓冲放大器裁判/CML 引脚。 | 不提供 CM 偏置。 | 确保放大器和ADC CM偏置都在彼此的范围内。否则,不匹配将导致错误。 |

| 交流耦合(带无缓冲 ADC) | 在 DS 指定的限制范围内设置 VOCM。使用分压器或其他一些稳定的偏置点。 | 集合 V在CM 偏置至 AVDD/2。使用分压器或CML引脚提供CM偏置。 | 将交流耦合电容放在放大器的输出端。 |

| 交流耦合(带缓冲型 ADC) | 在 DS 指定的限制范围内设置 VOCM。使用分压器或其他一些稳定的偏置点。 | 不提供 CM 偏置。V在引脚自偏置至 AVDD/2 + 0.7。 | 将交流耦合电容放在放大器的输出端。 |

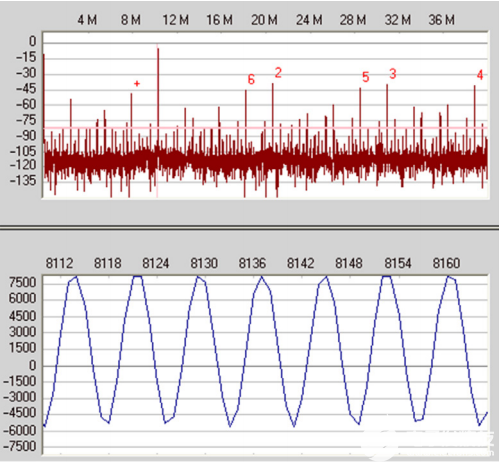

共模:损坏

如果未提供或维持共模偏置,则转换器将产生增益和失调误差,这些误差会降低到所采集的整体测量值。简而言之,转换器输出如图3所示或图3的某种变体。输出频谱将呈现为看起来像过载的满量程输入。这意味着转换器的零点偏离中心而不是最佳状态。设计人员可能会发现转换器会提前削波或无法达到转换器的满量程。最近,由于转换器使用1.8 V或更低的电源,这个问题变得更加严重。这意味着模拟输入的CM偏置为0.9 V或AVDD/2。并非所有单电源放大器都能支持如此低的共模电压,同时保持相对良好的性能。然而,一些新的放大器已经适应了这一点,并且今天已经上市。因此,谨慎的做法是审查哪些放大器可以在您的新设计中使用。不是任何旧的放大器都能工作,因为裕量可能会变得非常有限,内部晶体管开始塌陷。如果双电源与放大器一起使用,则在大多数情况下应有足够的裕量,以实现适当的CM偏置。不利的一面是额外的供应——可能是非标准的负供应,这意味着更多的零件和更多的钱。简单的逆变器电路将帮助解决这个问题。

图3.放大器和转换器之间的CM不匹配。

将一切整合在一起

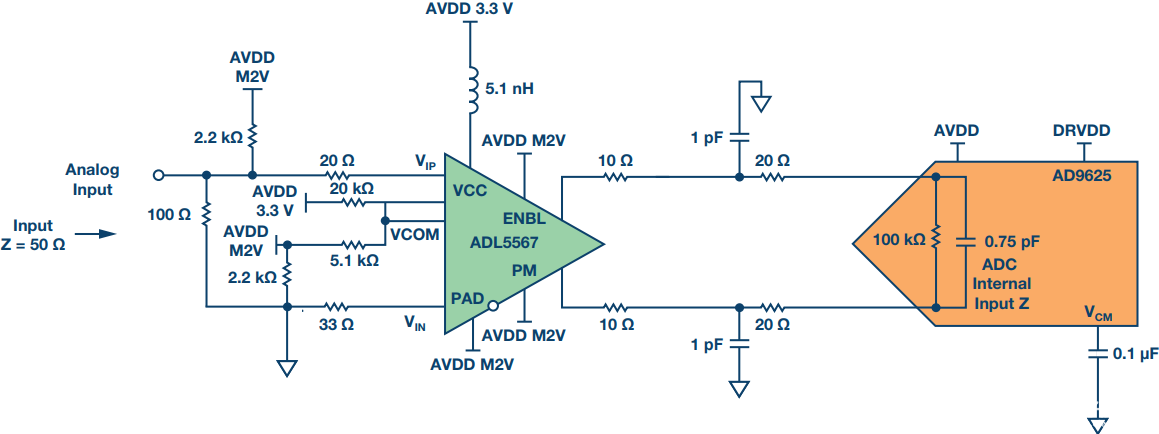

现在了解了共模和直流耦合,我们可以开始组合一个信号解决方案。例如,ADL5567是一款增益为20 dB的双通道差分放大器。它具有4.8 GHz带宽,适合与GSPS ADC接口,例如AD9625是一款12位、2.5 GSPS转换器,带有JESD204B 8通道接口。图 4 显示了该设置的整体框图。

图4.DC-WB放大器/转换器信号链示例

在所示的配置中,前端接口针对宽带采样进行了优化,同时保留了直流信号内容。由于该器件具有+5.5 V容限。该设计采用+3.3 V和−2 V AVDD分离电源。这使得放大器输出和ADC输入之间的共模对齐变得简单,两者在两个A上都需要+0.525 V。在+ 和 A在−. 另外,请注意,几个放大器引脚功能是接地的(V党卫军),现在仅使用单个电源强制使用−2 V电源(newV 党卫军).

CM电压输出相当简单,但了解放大器输入的共模需求可能有点棘手。对于接口,这里需要做两件事。首先,输入CM电压需要配置为0 V,否则,用失调驱动放大器将使输出轨偏向一侧。这将导致图3所示的性能问题或更糟的情况,即放大器和转换器信号链的交流性能较差。为此,放大器输入的每一侧都需要允许电流流向地,在这种直流耦合情况下为2 V。因此,在每个放大器输入端增加一个2.2 kΩ电阻,以消除该失调电流。

工作原理如下:放大器输出为~0.525 V,放大器的输入CM电压为0 V。使用500 Ω的内部反馈电阻和大约50 Ω的输入电阻,这看起来像550 Ω;或者在我们的例子中,我们假设 50 Ω源电阻与 100 Ω并联,这给了我们 33 Ω。串联中额外的 20 个Ω加起来就是 53 Ω。它与 500 Ω 内部反馈电阻串联,总计 553 Ω。这意味着开发了500 Ω和53 Ω的0.525 V电阻分压器。反过来,产生 900 μA 的电流(或 0.525/553)。将其分流到地面或新的 V党卫军或−2 V,增加一个2.2 kΩ电阻或−2 V/2.2 kΩ = 900 μA。

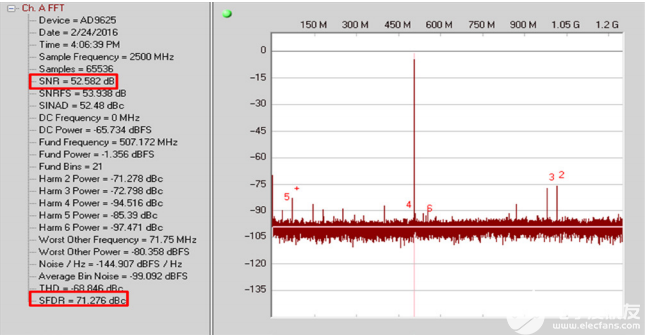

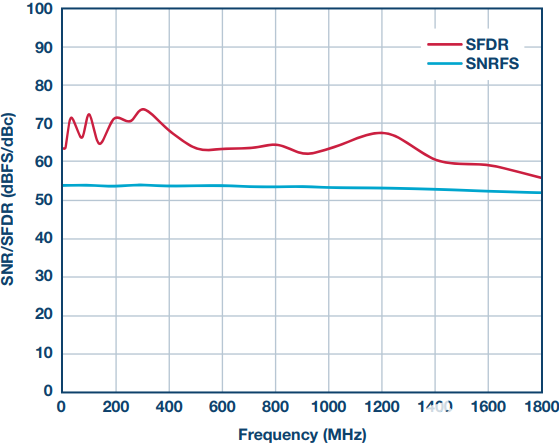

其次,输入是单端的,需要正确配置以保持最佳性能,同时保持低偶阶失真。同样,如前所述,有效 100 Ω与 50 Ω源电阻并行产生相当于 33.33 Ω的戴维宁。反过来,这通常反映在两个 V 上。在节点来平衡设备的输入,因为它是单端驱动的。但是,为了改善偶数阶失真,V上的20 Ω在+节点用于在所有宽带频率上保持低失真。这是通过使用特定的中频~500 MHz来完成的,或者参见图5作为测试用例。这可能很乏味,因为它是一个迭代过程。对于 S 中的计算和方程E有关放大器上的差分转换,请参见ADA4932数据手册。图6所示信号链设计的典型交流性能扫描输入频率高达2 GHz。

图5.典型 FFT 性能 @ 507 MHz A在@ 2500 MSPS。

图6.典型交流频率扫描性能 @ 2500 MSPS。

还值得注意的是,增加了与电源正电源轨输入串联的5.1 nH电感。这有助于通过在放大器内部捕获和再循环这些不平衡电流,再次提高偶数阶线性度性能。

最后,需要针对放大器和ADC之间的前端带宽优化接口。这通常也以迭代方式完成。但是,关于两个IC之间的某些值的设置,有几个注意事项需要牢记。可以应用以下规则列表,以便从界面中获得最佳BW。

首先,选择一个反冲电阻(R知识库)、(在本例中Ω),基于经验和/或ADC数据手册建议,通常在5 Ω到36 Ω之间。

然后,选择放大器外部串联电阻(R一个).使 R一个<如果放大器差分输出阻抗为100 Ω至200 Ω,则Ω 10。一个如果放大器的输出阻抗为 12 Ω或更低,则在 5 Ω 和 36 Ω 之间。本例为ADL5567选择10 Ω串联电阻,差分输出阻抗为10 Ω。

从放大器输出端看到的串联和并联电阻的总组合应接近放大器的额定负载(RL)。在这种情况下,160 Ω或 2 R一个+ 2 R知识库+ R模数转换器= 20 + 40 + 100,在图4的电路中。ADL5567的特性RL为200 Ω因此,如果设计偏离放大器的表征RL太远,线性度性能可能会有一些偏差。

最后,内部ADC电容C模数转换器,添加到 10 Ω串联电阻之后显示的分流 C,以帮助从内部 ADC 的采样网络反冲。这还提供软低通滤波,以减少带内折返的任何宽带谐波。

有关在放大器和ADC之间开发抗混叠滤波器的更完整过程,请参见CN-0227和CN-0238。

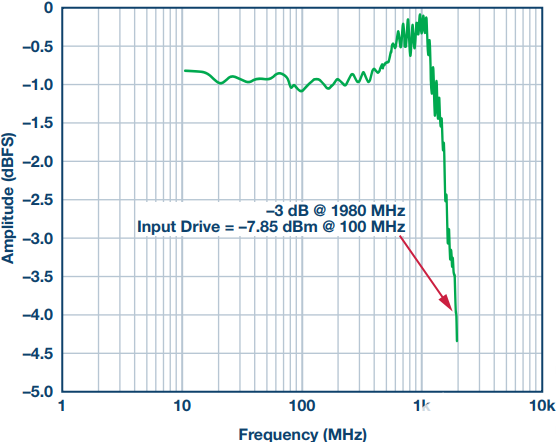

使用上述标准开发了2 GHz通带平坦度响应,以捕获1圣和 2德·奈奎斯特区,假设采样率为2.5 GSPS。本设计的输入驱动规格最终为−8 dBm或252 mV p-p,假设输入阻抗为50 Ω,基准电压源为100 MHz。这是放大器输入达到满量程所需的输入满量程电平。

图7.典型的通带平坦度性能和输入驱动电平。

结论

忽视转换器的共模输入电压规格可能会对任何直流耦合设计造成严重破坏。如果使用多个级,则整个信号链中的共模电平必须保持不变,以防止两个组件相互冲突。如果没有正确耦合,人们通常会在任何阶段之间获胜,从而产生虚假的测量结果。

对于交流耦合应用,在两级之间使用耦合电容来消除共模失配。例如,这允许设计优化放大器输出和ADC输入的偏置。

否则,系统设计中需要涉及双电源或电平转换电路,如上述直流耦合设计中所述。

审核编辑:郭婷

-

12大产品矩阵,高速高精度模拟信号链#芯片 #芯片 #国产芯片芯佰微电子 2025-04-24

-

模拟信号与数字信号的区别2024-05-21 4419

-

模拟信号是什么意思?怎么判断数字信号和模拟信号?2023-11-22 11978

-

从直流到宽带,模拟信号链设计不可忽略的“共模”资料下载2021-04-22 906

-

如何实现直流到宽带的高速模拟信号链设计2020-10-15 676

-

如何设计直流到宽带的高速模拟信号链?2019-08-02 1986

-

高速模拟信号链也可以从直流到宽带进行设计2019-04-10 2389

-

从直流到宽带,模拟信号链设计不可忽略的“共模”2018-10-11 2425

-

高速模拟信号链设计性能机制2018-09-12 2028

-

模拟信号链产品指南2017-09-12 1253

-

从直流到宽带的高速模拟信号链设计2016-12-23 3530

-

模拟信号链路产品指南2013-03-19 683

-

高速、高精度模拟信号处理2011-11-28 621

-

模拟信号,模拟信号是什么意思2010-03-06 3719

全部0条评论

快来发表一下你的评论吧 !