详解电源和地之间的走线电感

描述

PCB走线电感

其中W为走线宽度,l为走线长度,可以发现PCB走线电感与敷铜厚度无关,走线电感主要由长度l决定。

电源和地之间的走线电感

开关电源的MOSFET通常由IC的驱动级产生,MOSFET的源级通常接地,如果源级和地之间的走线有点长的话,在开关转换的瞬间上面会产生电感的反向电动势,不严重的话只是降低开关的切换速度,严重的话会是MOS管损坏,这种电压的脉冲不受控制,本质上是基于走线电感参数的,因此必须使你的源极寄生电感尽量小,走线短。

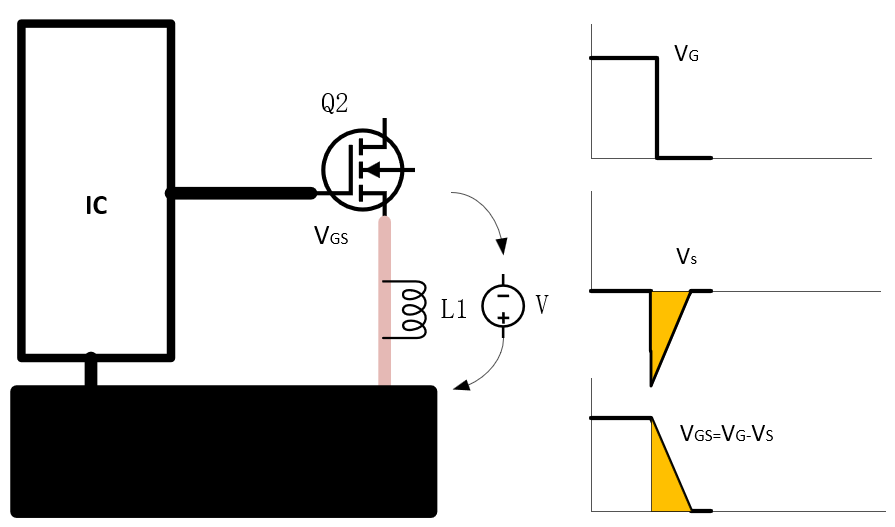

下图是MOS管开关瞬间可能发生的情形,这种情况是安全的,仅仅降低了开关的切换速度,当栅极控制MOS管关断的时候,由于漏源极导通的时候源极的PCB走线也通过了电流,这部分走线相当于一个小电感,由于电感的反向电动势,相当于一个小的电压源以阻止电流减小,电流持续流动一直到储能耗光,因此这段时间会使开关的关断速度下降。

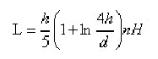

如果MOS管的源极是通过过孔下地,此时也需要注意过孔电感,此时需要多打过孔来减小寄生电感。

h为过孔深度(通孔为板厚),d为过孔直径,单位都为mm。

另外,射频调参的时候,理论的Smith圆图匹配和实际上差异非常大,是否需要把寄生参数表现出来的电容或者电感特性表示出来呢?感兴趣的同学可以思考一下走线电感与寄生电容/层间电容对射频电路的影响,以前项目需要,低频LC(125KHz)是可以通过已知参数计算出寄生电容的(pF/nF级,主要是使产品的谐振频率偏差5%以内,由于PCB板和每片IC的差异,因此需要通过对内部的谐振电容进行调谐),不过高频的没试过,频率稳定度要求高的话,100ppm的话也够了,不知道有没有这类的案例。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

【EMC技术案例】共模电感与电源模块之间PCB走线导致RE超标案例2025-09-28 835

-

是否存在有关 PCB 走线电感的经验法则?2024-12-13 4255

-

详解高密 PCB走线布线的垂直导电结构 (VeCS)2023-11-28 3470

-

如何计算地平面上方走线的电感?2023-11-11 3790

-

什么是环路面积?怎么减小走线的环路电感?2023-11-09 7661

-

详解pcb走线电流2023-10-30 3535

-

如何优化PCB走线来减小回路电感和环路面积?2023-10-23 6951

-

PCB走线的设计细节详解2023-04-13 2572

-

计算机组装电源线排,主机箱背部走线技巧 组装电脑走背线与理线教程2022-01-06 2996

-

如何有效减少PCB走线之间的串扰2021-03-03 4931

-

主板的走线和布局设计详解2011-06-23 7104

全部0条评论

快来发表一下你的评论吧 !