使用电解电容需要注意什么?

描述

1. 某应用中,大容量电容计算值为45uF,可以选择47uF的电容吗?

通常需要选择比理论计算值至少大1.4倍的电容。一定时间内影响电容实际容值的因素非常多,比如施加的电压增加,大多数MLCC的容值会显著下降,铝电解的容值更稳定,但是铝电解容易老化,电解液会变干,伴随着容值的显著下降并且ESR会增大。另一方面,钽电容的ESR可令人接受,容值更稳定,没有老化现象,且工作温度范围很宽,但是钽电解最大额定电压限制在50V,实际应用还会降到该值的一半,另外,钽电解失效模式为爆炸。所以此应用选择68uF的陶瓷电容较为合适。对于铝电解电容,由于损坏之前ESR变得更高,所以应该2个47uF并联使用。对于钽电解,在输入电压不超过18V的情况下,单独使用一个47uF/35V的电容就可以了。

2. 我可以将几个相同的电容并联改善旁路性能吗?

可以,但只是在一定程度上面改善,电路总的ESL和ESR减小了,电容成倍的增加,但是电容组总的自谐振频率与一个电容相比是不变的。

假设有n个电容并联,则C=>nC, ESR=>ESR/n,ESL=>ESL/n, fc谐振=>fc谐振。对于现在DCDC应用来说,0.1uF的MLCC自谐振频率为30MHz, 这一频率已经足够高了。

3. 使用电解电容需要注意什么?

首先,电容是有极性的,只能承受1.5V的反向电压。电解电容最大的问题是最低工作温度,因为液体电解质会凝固,虽然大多数电容最低-40甚至-55°C,但是容值在低温下会下降10%~20%,同时ESR会增加10倍。

由于电容的初始容值公差是±20%,如果电容寿命为初始容值基础上再降低20%,那么100uF的电解电容有效寿命最恶劣的情况是100uF*(1-20%)*(1-20%)=64uF。为了防止振动使电解电容从PCB脱落,需增加点胶工艺。

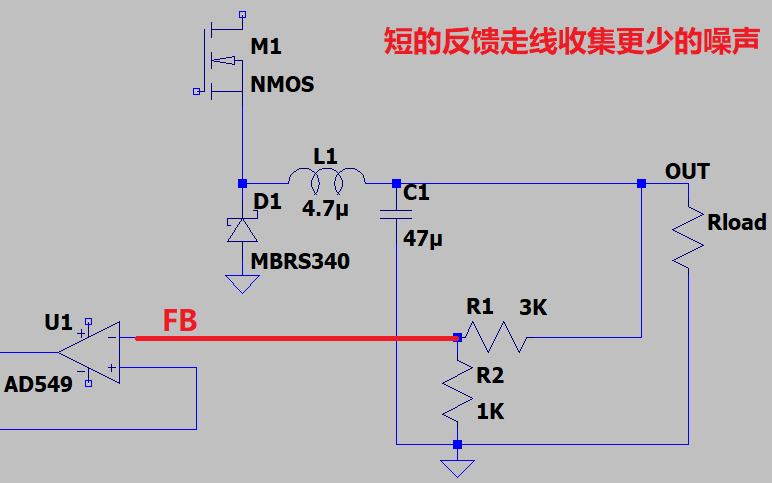

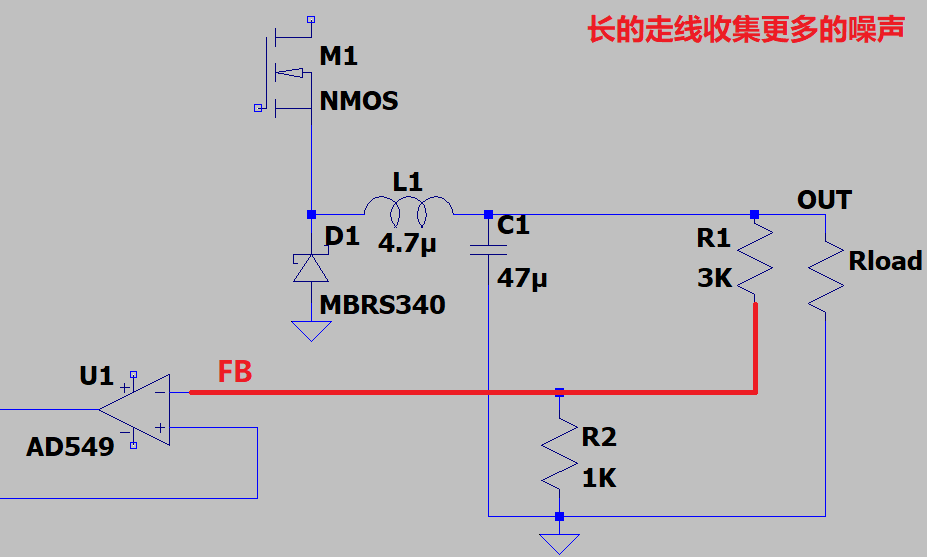

4. DCDC分压器如何布局,决定反馈走线噪声大小的关键因素?

首先,反馈引脚的走线是一条非常敏感的走线,途中会拾取大量的噪声,影响负载调整率(负载调整率=(空载时输出电压-满载时输出电压)/(额定负载时输出电压)*100%,好的电源负载调整率小),信号抖动甚至振荡等等。其次反馈走线只有在离开了电阻分压节点之后才会对噪声变得敏感,即在通向反馈引脚的线路中,主要是因为走线两端都倍高阻抗所包围,无法有效衰减噪声。因此分压电阻不能选的足够大,如几百K,否则噪声会更大。通常PCB Layout时应使这段线足够短。

-

电源滤波用电解电容2012-08-14 3349

-

高通滤波器需要22UF电容,可以用电解电容代替吗2017-07-02 7927

-

贴片电容和电解电容有什么区别2019-06-27 3475

-

电解电容的作用和使用注意事项2007-10-15 5503

-

浅谈电源滤波用电解电容2016-08-22 1096

-

整流后滤波用电解电容的选择2017-03-04 1411

-

贴片电解电容焊接技巧_电解电容焊接方法2018-03-14 41719

-

电解电容的原理2018-11-05 29640

-

使用电解电容器时需要注意哪些事项2022-02-16 7230

-

电解电容和非电解电容有什么区别?2022-10-28 3805

-

电解电容基础2022-12-19 4548

-

作为电解电容器,钽电容器优于铝电容器?2023-11-03 2027

-

使用电容降压时都需要注意哪些?2024-02-02 1664

-

电解电容的正负极怎么区分2024-06-18 14390

-

贴片电解电容和电解电容替换的选用2024-11-17 3409

全部0条评论

快来发表一下你的评论吧 !