PCI总线地址空间与系统地址空间的关系

描述

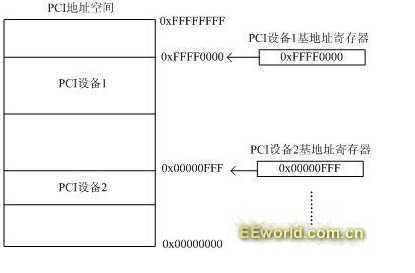

1、PCI地址空间

PCI总线具有32位数据/地址复用总线,所以其存储地址空间为2的32次方=4GB。也就是PCI上的所有设备共同映射到这4GB上,每个PCI设备占用唯一的一段PCI地址,以便于PCI总线统一寻址。每个PCI设备通过PCI寄存器中的基地址寄存器来指定映射的首地址。PCI地址空间对应于计算机系统结构中的PCI总线。

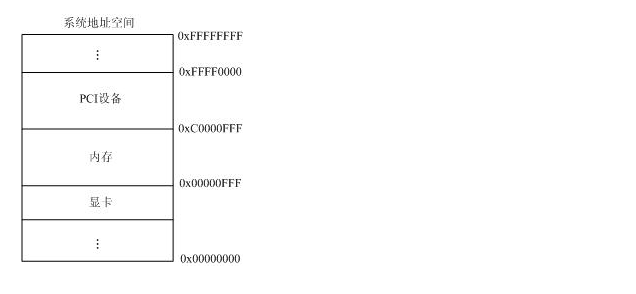

2、系统地址空间

如果处理器具有32位的地址总线,其理论可寻址空间为2的32次方=4GB。但这并不意味着内存就可以4GB大小,其实XP系统最大内存大约为2GB,这与CPU访问系统中其它设备的存储器方式有关(比如CPU访问PCI总线上的存储器)。

计算机系统中在不同的物理位置上存在着不同设备,不同的设备又各自具有存储器,那么CPU如何访问这些存储器呢?CPU把系统中各个设备的存储空间映射到一个统一的存储空间上,称为系统存储空间共4GB,这样CPU就可以访问到所有的存储器。比如PCI存储器映射到从0xFFF80000开始的地址空间,显卡映射到0XFFF00000,再加上操作系统会占用一些空间,就只剩下不到2G能真正分配给物理内存了。(具体数值是为解释需要取的任意值,不代表真实情况)

系统地址空间对应于计算机系统结构中的前端总线(FSB)。

3、PCI总线地址与系统存储空间转换映射

3、PCI总线地址与系统存储空间转换映射

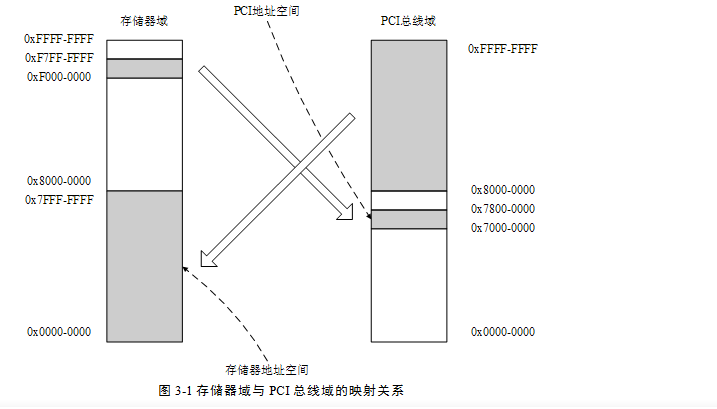

我们假设在一个32位处理器中,其存储器域的0xF000-0000~0xF7FF-FFFF(共128MB)这段物理地址空间与PCI总线的地址空间存在映射关系。

当处理器访问这段存储器地址空间时,HOST主桥将会认领这个存储器访问,并将这个存储器访问使用的物理地址空间转换为PCI总线地址空间,并与0x7000-0000~0x77FF-FFFF这段PCI总线地址空间对应。

为简化起见,我们假定在存储器域中只映射了PCI设备的存储器地址空间,而不映射PCI设备的I/O地址空间。而PCI设备的BAR空间使用0x7000-0000~0x77FF-FFFF这段PCI总线域的存储器地址空间。

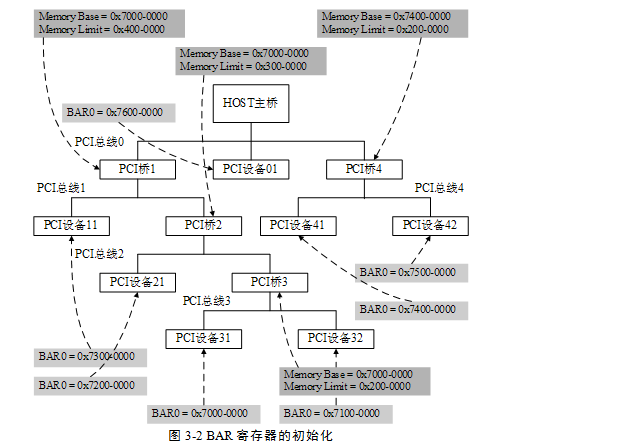

PCI桥的Base、Limit寄存器保存“该桥所管理的PCI子树”的存储器或者I/O空间的基地址和长度。值得注意的是,PCI桥也是PCI总线上的一个设备,在其配置空间中也有BAR寄存器,本节不对PCI桥BAR寄存器进行说明,因为在多数情况下透明桥并不使用其内部的BAR寄存器。下文以图3‑2所示的处理器系统为例说明上述寄存器的初始化过程,该处理器系统使用的存储器域与PCI总线域的映射关系如图3‑1所示。

注意观察上图中PCI设备的BAR0寄存器值,如果PCI设备向下级联了(相当于PCI桥),BAR0是不变的,而且LIMIT寄存器受PCI未继续级联(而是直接接了PCI设备)的BAR0影响。

在PCI设备的BAR寄存器中,包含该设备使用的PCI总线域的地址范围。在PCI设备的配置空间中共有6个BAR寄存器,因此一个PCI设备最多可以使用6组32位的PCI总线地址空间,或者3组64位的PCI总线地址空间。这些BAR空间可以保存PCI总线域的存储器地址空间或者I/O地址空间,目前多数PCI设备仅使用存储器地址空间。而在通常情况下,一个PCI设备使用2到3个BAR寄存器就足够了。

为简化起见,我们首先假定在图3‑2中所示的PCI总线树中,所有PCI Agent设备只使用了BAR0寄存器,其申请的数据空间大小为16M字节(即0x1000000字节)而且不可预读,而且PCI桥不占用PCI总线地址空间,即PCI桥不含有BAR空间。并且假定当前HOST主桥已经完成了对PCI总线树的编号。

根据以上假设,系统软件该PCI总线树的遍历过程如下所示。

(1) 系统软件根据DFS算法,系统软件率先寻找到第一组PCI设备,分别为PCI设备31和PCI设备32[1],并根据这两个PCI设备需要的PCI空间大小,从PCI总线地址空间中(0x7000-0000~0x77FF-FFFF)为这两个PCI设备的BAR0寄存器分配基地址,分别为0x7000-0000和0x7100-0000。

(2) 当系统软件完成PCI总线3下所有设备的BAR空间的分配后,将初始化PCI桥3的配置空间。这个桥片的Memory Base寄存器保存其下所有PCI设备使用的“PCI总线域地址空间的基地址”,而Memory Limit寄存器保存其下PCI设备使用的“PCI总线域地址空间的大小”。系统软件将Memory Base寄存器赋值为0x7000-0000,而将Memory Limit寄存器赋值为0x200-0000。

(3) 系统软件回朔到PCI总线2,并找到PCI总线2上的PCI设备21,并将PCI设备21的BAR0寄存器赋值为0x7200-0000。

(4) 完成PCI总线2的遍历后,系统软件初始化PCI桥2的配置寄存器,将Memory Base寄存器赋值为0x7000-0000,Memory Limit寄存器赋值为0x300-0000。

(5) 系统软件回朔到PCI总线1,并找到PCI设备11,并将这个设备的BAR0寄存器赋值为0x7300-0000。并将PCI桥1的Memory Base寄存器赋值为0x7000-0000,Memory Limit寄存器赋值为0x400-0000。

(6) 系统软件回朔到PCI总线0,并在这条总线上发现另外一个PCI桥,即PCI桥4。并使用DFS算法继续遍历PCI桥4。首先系统软件将遍历PCI总线4,并发现PCI设备41和PCI设备42,并将这两个PCI设备的BAR0寄存器分别赋值为0x7400-0000和0x7500-0000。

(7) 系统软件初始化PCI桥4的配置寄存器,将Memory Base寄存器赋值为0x7400-0000,Memory Limit寄存器赋值为0x200-0000。系统软件再次回到PCI总线0,这一次系统软件没有发现新的PCI桥,于是将初始化这条总线上的所有PCI设备。

(8) PCI总线0上只有一个PCI设备,PCI设备01。系统软件将这个设备的BAR0寄存器赋值为0x7600-0000,并结束整个DFS遍历过程。

精彩推荐 至芯科技12年不忘初心、再度起航12月17日北京中心FPGA工程师就业班开课、线上线下多维教学、欢迎咨询! 至芯科技精品寒假班来袭,1月7号线上授课,欢迎广大学子,电子爱好者前来学习! FPGA学习-IO延迟的约束方法 关于数字信号处理中的降采样扫码加微信邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:PCI总线地址空间与系统地址空间的关系

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- FPGA

-

MMU虚拟地址空间布局2023-11-26 1818

-

Linux虚拟地址空间和物理地址空间的关系2023-10-08 2313

-

Linux系统为什么需要引入虚拟地址2023-10-07 1753

-

Linux操作系统中程序地址空间详解2023-09-12 950

-

Normal World与Secure World的地址空间隔离是如何实现的2023-09-05 2203

-

psram地址空间如何对应?2023-08-16 481

-

PCI/PCIe地址空间的概念2023-07-30 1332

-

Linux程序地址空间详解2023-03-26 1150

-

如何使用MMU隔离地址空间2021-12-31 593

-

S5PV210的内存地址线与CPU地址空间有何关系2021-10-21 1419

-

Linux操作系统知识讲解:走进linux 内存地址空间2020-08-28 6016

-

深入浅出Linux的进程地址空间2020-06-20 2478

-

PCI总线的地址空间分配2018-04-12 8194

-

什么是cpu的io端口?地址空间如何共享?2017-11-15 16134

全部0条评论

快来发表一下你的评论吧 !