解读用于通信系统的差分滤波器

描述

当涉及到通信系统时,差分电路总是可以 在单端电路上提供更好的性能。他们可以提供 更高的线性度,对共模干扰信号的抗扰度,以及 更多。然而,差分电路周围往往有很多谜团。 一些 RF 工程师认为他们很难设计、测试和调试。这 差分滤波器似乎尤其如此。是时候揭开面纱了 关闭差分滤波器设计。

为此,我们将从通信系统接收链 IF 开始 舞台过滤器。我们将看一些基本的过滤器键规范概念,一个 几种常用的滤波器响应,切比雪夫 1 型滤波器 应用,以及如何从单端滤波器设计开始,然后转移 即差分滤波器设计。我们还将研究差分滤波器 设计示例以及如何优化差速器的几点 电路PCB设计。

差分电路在RF信号链应用中的优势

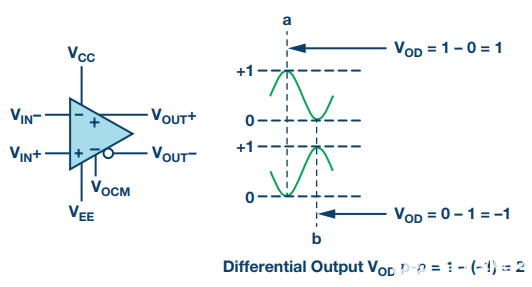

用户使用差分电路可以获得比 具有单端电路。在相同的电源电压下,a 差分信号可以提供两倍的幅度 单端信号。它还提供更好的线性度和信噪比性能

图1.差分输出幅度

差分电路相当不受外部EMI和串扰的影响。 附近的信号。这是因为接收电压加倍,而且, 从理论上讲,噪声对紧密耦合走线的影响相等,从而抵消 彼此出来。

差分信号也往往产生较少的EMI。这是因为 信号电平(dV/dt 或 dI/dt)的变化会产生相反的磁场, 再次相互抵消。

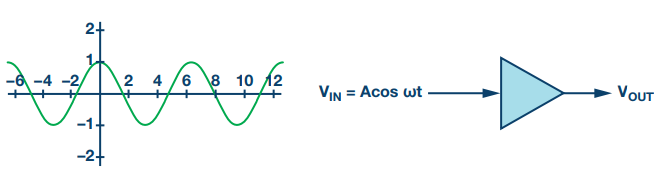

差分信号可以抑制偶次谐波。这显示在 以下示例中,连续波 (CW) 通过一个 增益阶段。使用一个单端放大器时,输出可以是 表示,如图2、等式1和等式2所示。

图2.单端放大器

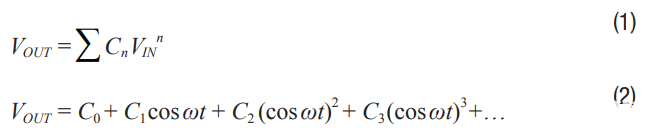

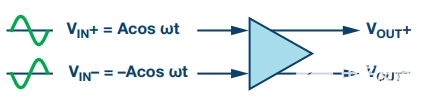

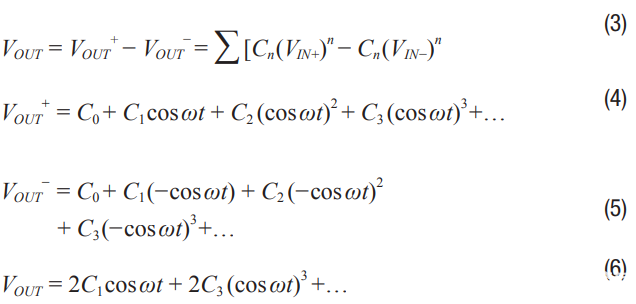

使用一个差分放大器时,输入和输出显示在 图3和等式3、等式4、等式5和等式6。

图3.差分放大器

理想情况下,输出没有任何偶次谐波,使 差分电路是通信系统的更好选择。

过滤 器

过滤器规格

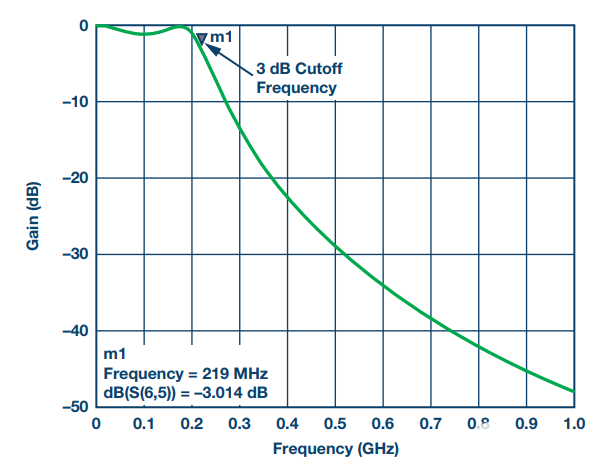

截止频率、转折频率或断路频率是 能量流经系统时系统的频率响应 开始减少(衰减或反射)而不是通过。

图4.3 dB 截止频率点

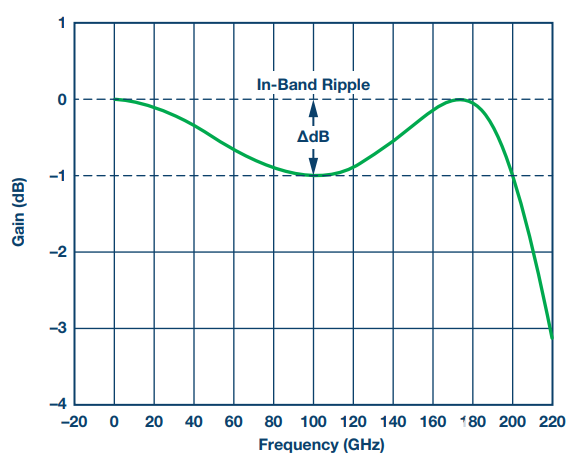

带内纹波是通带内插入损耗的波动

图5.带内纹波。

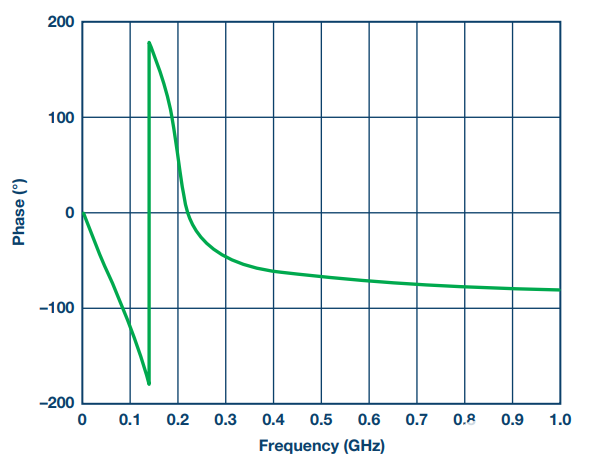

相位线性度是相移与频率的直接比例 感兴趣的频率范围。

图6.相位线性度

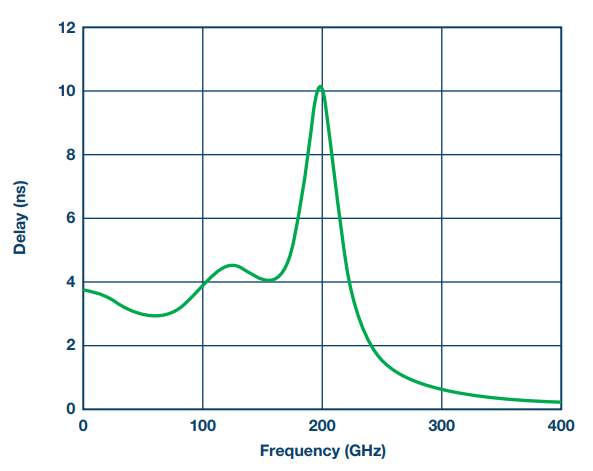

群延迟是幅度包络 通过被测器件的信号的各种正弦分量, 并且是每个组件的频率的函数。

图7.组延迟

过滤器比较

| S21 响应 | 优点 | 缺点 |

|

巴特沃思 |

||

| 参见图8 | 通带平整度非常好 | 在停止带中缓慢滚动 |

|

椭圆 |

||

| 参见图9 | 在停止带内非常迅速地滚落 | 在通带和阻带均有均衡纹波;这会影响阻带抑制性能 |

|

贝塞尔 |

||

| 参见图 10 | 最大平坦群/相位延迟 | 停止带内滚降非常慢 |

|

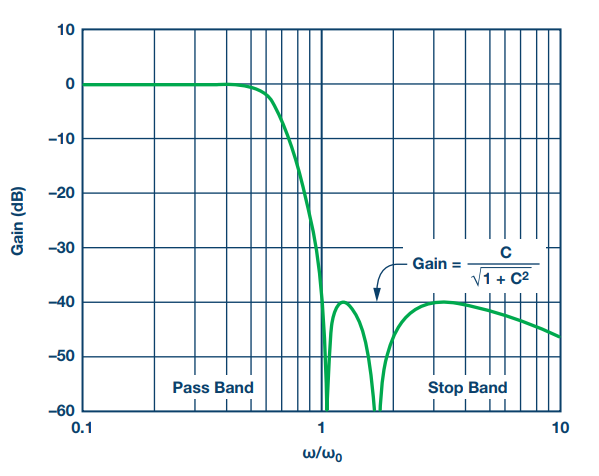

切比雪夫I型 |

||

| 参见图 11 | 在阻带中快速滚落;阻带内无均衡纹波 | 在通带中具有均衡纹波 |

| 切比雪夫II型 | ||

| 参见图 12 | 通带内无纹波 | 滚降不是很快;在阻带中均衡纹波 |

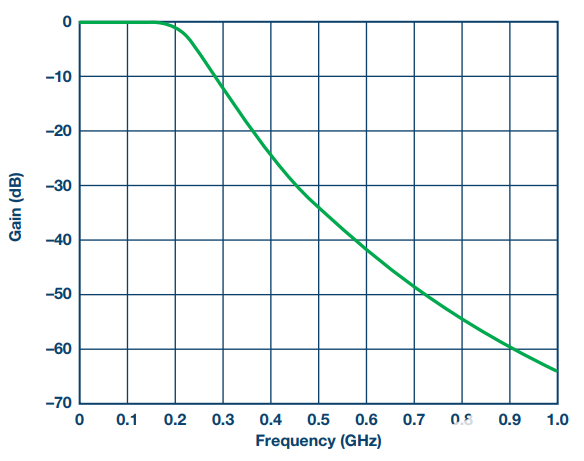

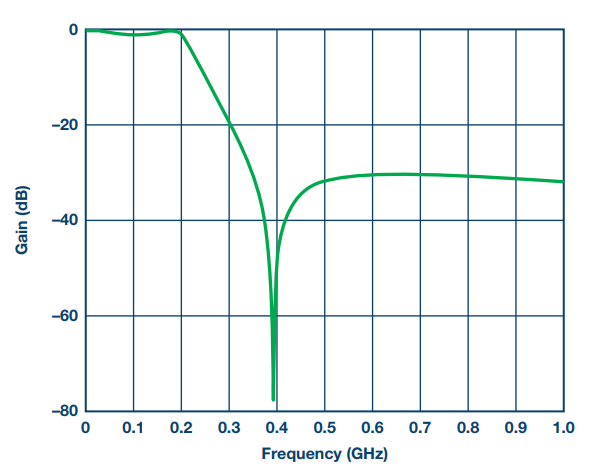

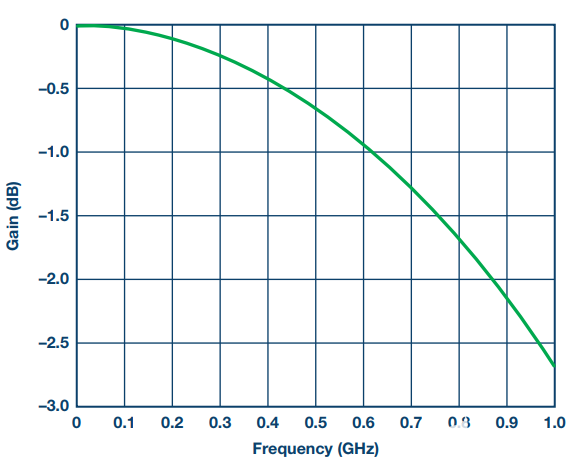

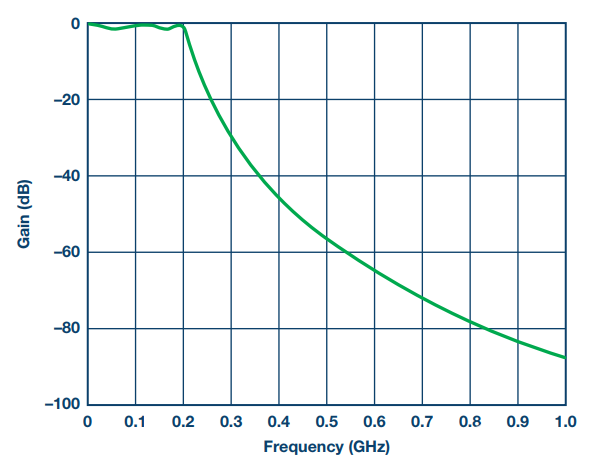

图8.巴特沃斯滤波器 S21 响应。

图9.椭圆滤波器 S21 响应

图 10.贝塞尔滤波器 S21 响应。

图 11.切比雪夫 I 型过滤器 S21 响应。

图 12.切比雪夫II型滤波器S21响应

通信接收链中的IF滤波器基本上是低通 滤波器或带通滤波器。它用于抑制混叠信号 与有源组件产生的杂散。杂散包括谐波 和IMD产品等。使用过滤器,接收链可以 提供高SNR信号供ADC分析。

选择切比雪夫 I 型滤波器作为拓扑,因为它具有 良好的带内平坦度、快速滚降,在 停止带。

设计低通滤波器

由于接收器IF滤波器用于抑制杂散和混叠信号, 其阻带滚降应尽可能快。但是,滚降速度更快 意味着高阶组件,高阶有几个原因 不建议进行筛选:

在设计和调试阶段难以调整。

量产难:电容器和电感器有零件间的差异,每个PCB板上的滤波器很难有相同的响应。

电路板尺寸大

通常,使用七阶或更低的滤波器。同时,如果更大 带内纹波不是相同阶数分量的问题,那么 在停止波段中更快的滚降是一种支出。

然后,通过指定所需的衰减来定义所需的响应 在选定的频率点。

要确定通带中的最大纹波量,请保留 规范到系统要求的最大限制。这可以 帮助在停止带中更快地滚降。

使用滤波器软件(如 MathCad、MATLAB 或 ADS)来设计 单端低通滤波器。®®

或者,手动设计过滤器。一个有用的指南是射频电路设计 作者:克里斯·博威克。

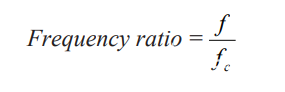

要确定滤波器的阶数,请将感兴趣的频率归一化为 将其除以滤波器的截止频率。

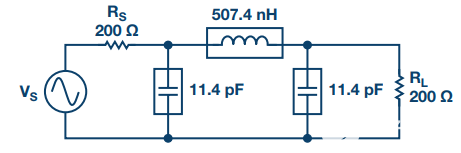

例如,如果带内纹波需要为0.1 dB,则3 dB截止 频率为 100 MHz。在 250 MHz 时,抑制需要为 28 dB,因此 频率比为2.5。三阶低通滤波器可以满足这一要求。 如果滤波器的源阻抗为200Ω,则 滤波器也是200Ω,RS/RL为1——使用电容器作为第一元件。 然后,用户收到规范化的 C1 = 1.433,L2 = 1.594,C3 = 1.433。 如果FC为100 MHz,则使用公式7和公式8获得最终结果。

哪里:

C规模是最终的电容值。

L规模是最终电感值。

Cn是低通原型元素值。

Ln是低通原型元素值。

RL是最终负载电阻值。

fc是最终截止频率。

C1规模= 1.433/(2π × 100 × 106 × 200) = 11.4 pF

L2规模= (1.594 × 200)/(2π × 100 × 106) = 507.4 nH

C3规模= 11.4 pF

电路如图13所示。

图 13.单端滤波器示例

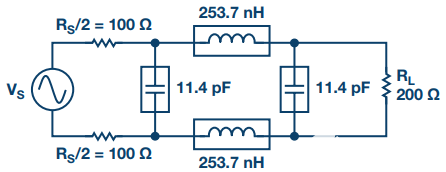

将单端滤波器转换为差分滤波器(见图14)。

图 14.将单端滤波器转换为差分滤波器

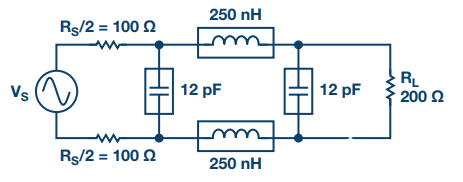

使用每个组件的实际值,筛选器更新为 如图 15 所示。

图 15.最终差分滤波器

注意,如果混频器或中频放大器的输出阻抗和 ADC的输入阻抗是容性的,最好考虑使用一个 电容器作为第一个元件,电容器作为最后一个元件。 此外,调谐第一级电容器和最后级电容器也很重要 高于输出电容的速率(至少0.5 pF)的值 混频器或IF放大器的阻抗和ADC的输入阻抗。 否则,很难调整滤波器响应。

设计带通滤波器

在通信系统中,当中频频率相当高时,有些低 频率杂散需要滤除,例如半中频杂散。为此, 设计带通滤波器。对于带通滤波器,没有必要 对称,用于低频和高频抑制。简单的方法 设计带通抗混叠滤波器就是先设计低通滤波器, 然后在 滤波器的最后级,用于限制低频元件(并联电感器) 是一个高通共振极点)。如果是单级,则高通电感不是 足够了,再添加一个与第一级并联的并联电感器 电容,以获得对低频杂散的更多抑制。添加后 并联电感,再次调谐所有组件以实现正确的带外 拒绝规范,然后最终确定过滤器组件值。

请注意,一般来说,对于带通滤波器,串行电容不是 建议使用,因为它们会增加调优和调试难度。 电容值通常很小,并且受到以下因素的严重影响 寄生电容。

应用示例

以下是ADL5201和AD6641之间的滤波器设计示例。 ADL5201是一款高性能中频数控增益放大器 (DGA),专为基站真实中频接收器应用或 数字预失真 (DPD) 观察路径。它具有 30 dB 增益控制 范围、极高的线性度(OIP3 达到 50 dBm)和电压增益 约 20 分贝。AD6641是一款250 MHz带宽DPD观测器件 集成 12 位、500 MSPS ADC、16,000 × 12 FIFO 的接收器,以及 一个多模式后端,允许用户通过 串行端口。此筛选器示例是一个 DPD 应用程序。

以下是一些带通滤波器规格,取自 真实的通信系统设计:

中心频率: 368.4 MHz

带宽:240兆赫

输入输出阻抗:150Ω

带内纹波:0.2 dB

插入损耗:1 dB

带外抑制:614.4 MHz 时为 30 dB

要构建示例设计,请执行以下操作:

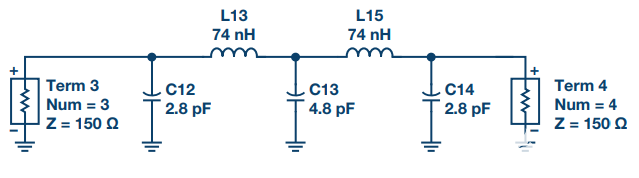

1. 从单端低通滤波器设计开始(见图16)。

图 16.单端、低通滤波器

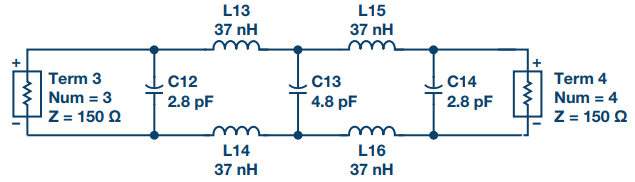

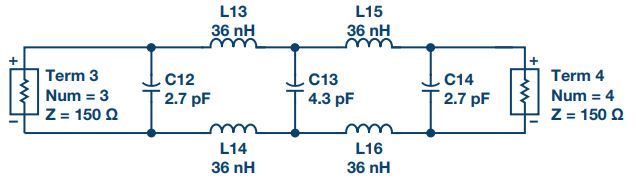

2.将单端滤波器改为差分滤波器。保留源 与负载阻抗相同,分流所有电容,并切断所有串联 电感器对半,并将它们放在另一个差分路径中(见图17)。

图 17.具有理想元件的差分低通滤波器。

3. 以实际价值优化组件的理想价值 (参见图 18)。

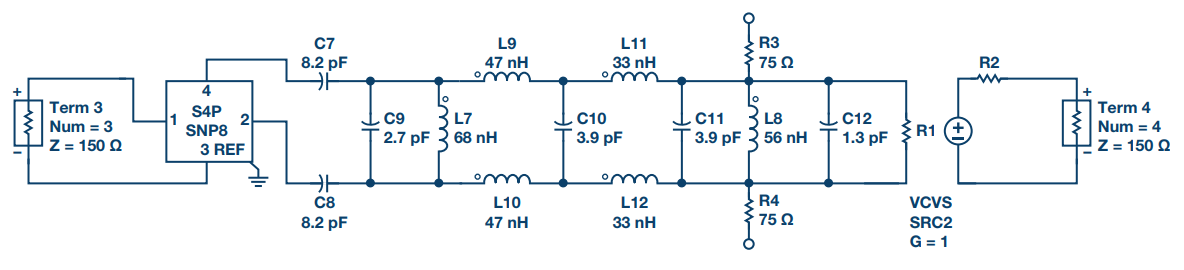

图 18.具有实际值的差分低通滤波器

4. 对于子系统级仿真,添加ADL5201 DGA S参数 文件,使用电压控制电压源对 滤波器输出端的AD6641 ADC。更改低通滤波器 在带通滤波器中,增加两个并联电感:L7 并联 C9 和 L8 与 C11 并行。C12代表AD6641输入 电容。R3和R4是两个负载电阻,位于 AD6641为负载滤波器。AD6641输入为高阻抗。 调整后,请参见图 19。

图 19.差分带通滤波器。

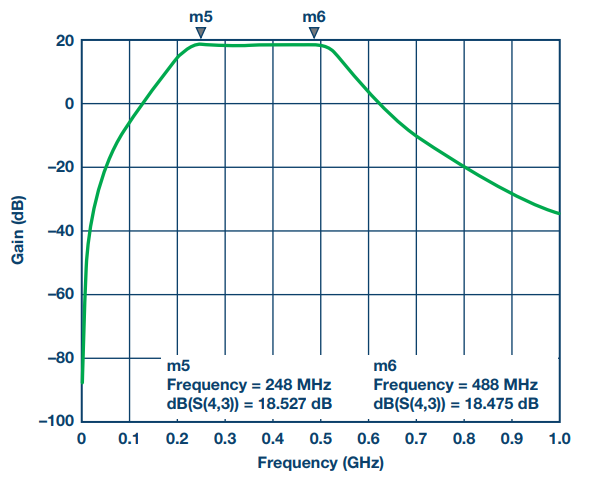

5. 理想元件的仿真结果如图20所示。

图 20.使用理想电感器滤波传输响应。

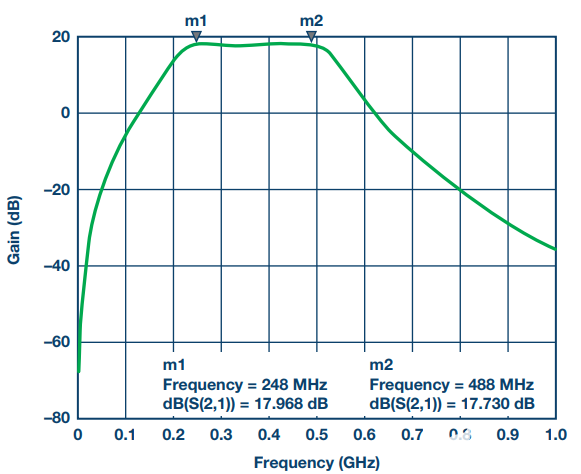

6.将所有理想电感器更换为电感器S参数文件 目标设备(例如,村田制作所LQW18A)。插入损耗 比使用理想电感器高一点。仿真结果 略有变化,如图 21 所示。

图 21.使用村田制作所LQW18A电感器的滤波器传输响应。

差分滤波器布局注意事项

一对中的差分走线需要具有相等的长度。此规则起源于 从差分接收器检测到负极位置的事实来看 正信号同时相互交叉——交叉 点。因此,信号同时到达接收器 操作正常。

差分对内的走线需要彼此靠近布线。 如果 它们之间的距离为介电厚度的>2×。此外,此规则是 基于以下事实:因为差分信号相等并且 相反,如果外部噪声同样干扰这些信号,则噪声 无效。类似地,差分信号引起的任何不需要的噪声 如果走线并排布线,则取消进入相邻导线。

差分对内的迹线分离需要在其上保持恒定 整个长度。如果差分走线靠近布线,它们将 影响整体阻抗。如果不保持这种分离 驱动器到接收器,沿途存在阻抗不匹配, 导致反射。

使用较宽的对间间距以最大程度地减少对之间的串扰。

如果在同一层上使用铜填充,请增加与 铜填充的差分走线。最小间隙为迹线的 3× 建议从走线到铜填充的宽度。

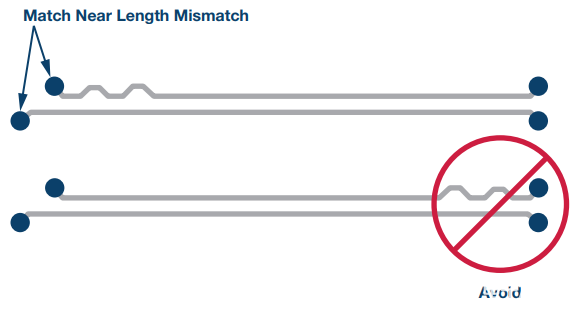

通过引入小的、蜿蜒的 接近偏斜源的校正(参见图 22)。

图 22.使用蜿蜒的校正

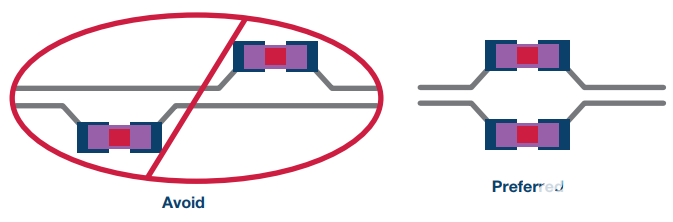

布线差分对时避免急(90°)弯曲(见图23)。

图 23.避免 90° 弯曲

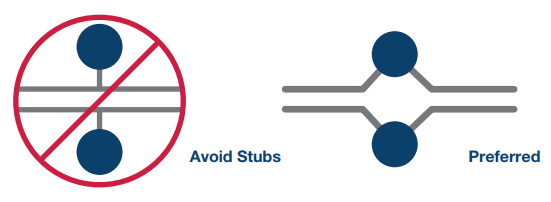

路由差分对时使用对称路由(参见图 24)。 如果需要测试点,请避免引入跟踪存根并进行测试 点对称(参见图 25)。

图 24.对称路由准则

图 25.避免跟踪存根

在放宽过滤器组件值调优工作负载方面 印刷电路板(PCB),保持寄生电容很重要 电感尽可能低。寄生电感可能不会 与滤波器中电感器的设计值相比,意义重大 设计。寄生电容对于差分IF滤波器更为关键。 中频滤波器设计中的电容器只有几皮法。如果寄生 电容达到十分之几皮法,它会影响滤波器 反应显著。为了防止寄生电容,一个好的做法是 避免差分路由区域下的任何接地或电源层 和电源阻塞下。

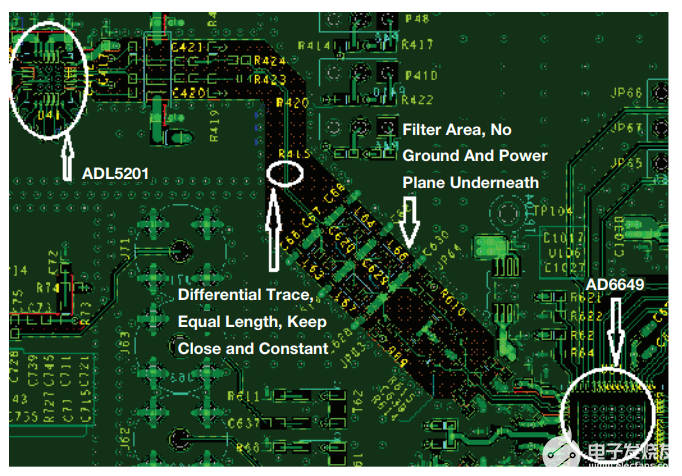

差分滤波器PCB布局的一个示例是ADI接收器基准电压源 设计板(见图 26)。这显示了 ADL5201和AD6649。AD6649是一款14位、250 MHz流水线ADC 具有非常好的信噪比性能。

图 26.差分电路PCB布局设计示例

更好地了解差分滤波器设计

差分电路为设计人员提供了一些显著的优势。 也许使用它们的最大挑战是简单地超越 认为它们很难设计、测试和纠正。一旦你拿了一个好 看看如何使用差分滤波器,你可能会发现自己有一个 用于射频设计的宝贵新工具。

审核编辑:郭婷

-

差分滤波器截止频率应该是多少?2024-11-28 1054

-

如何将单端滤波器设计转化为差分滤波器设计2023-11-23 1286

-

差分滤波器如何计算频率带宽2022-07-13 27672

-

浅谈差分输入的 2 极滤波器设计2021-06-16 10238

-

差分滤波器的布局布线需要考虑那些问题2020-10-10 806

-

差分滤波器布局布线需考虑以下八个要点2019-06-24 2430

-

通信系统中,差分滤波器如何布局?2018-12-27 2050

-

差分滤波器布局布线的8个注意点2018-08-18 3864

-

通信系统中接收链差分滤波器设计2018-04-08 1401

-

基于LC带通差分滤波器的精细化仿真方法(利用ADS设计)2017-11-01 3018

-

详细解析差分滤波器:性能 原理 应用 电路图 设计2017-05-04 40283

-

差分滤波器布局需要考虑的那些事儿2017-02-10 2575

-

差分滤波器布线需要注意的8个问题2016-12-05 4839

-

差分滤波器设计2016-08-23 2076

全部0条评论

快来发表一下你的评论吧 !