D触发器不同应用下的电路图详解

电子说

描述

D 触发器或数据触发器是一种触发器,它只有一个数据输入“D”和一个时钟脉冲输入, 这种触发器也称为延迟触发器,经常用于许多时序电路,如寄存器、计数器等。下面一起来了解一下D触发器不同应用下的电路图。

一、使用D触发器的移位寄存器

触发器也是单个寄存器,当一个寄存器设计有多个触发器时,可以存储一位,可以容纳更多位数据。最后,移位寄存器是一种用于存储或传输数据的逻辑电路。

移位寄存器设计有不同数量的触发器,数据可以从左到右或从右到左传送。它可以有并行输入或串行输入和串行输出或并行输出。移位寄存器也可以设计为D触发器。

二、使用 D 触发器的串行输入串行输出移位寄存器

在这种类型的寄存器中,输入是一次一位串行,输出也是串行一位。

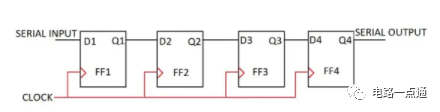

带D触发器的串行输入串行输出移位寄存器设计

每个触发器一次只能存储一位,因此对于 4 位移位寄存器,需要四个触发器。如上所示,串行数据通过第一个触发器的 D 应用到所有剩余的触发器。当一系列数据输入寄存器时,每一位都随着时钟脉冲的每个正沿提供给下一个触发器,并且随着每个时钟脉冲,串行数据从一个触发器移动到下一个触发器。

三、2 位移位寄存器使用 D 触发器

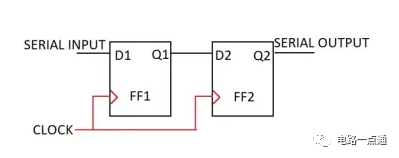

下图是可以存储或传输2位数据的2位移位寄存器的示意图。其中输入数据和输出数据都是串行的,所以它是一个 串行输入串行输出 (SISO) 两位移位寄存器,输入数据的过程从寄存器的最低有效位开始,数据输入随着时钟脉冲的每个正沿进入寄存器。

使用D触发器的移位寄存器

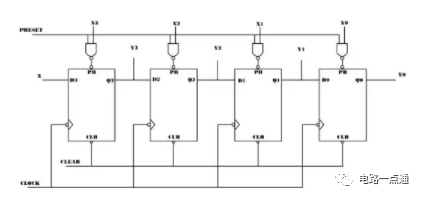

三、使用 D 触发器的并行输入串行输出移位寄存器

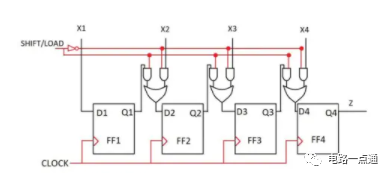

下面是 4 位移位寄存器的 XNUMX 条不同的数据线;每个 D 触发器都有其单独的输入。数据以并行方式送入各个寄存器。对于每个时钟脉冲,数据位都移向此处的输出 Z。输出以串行序列形式输出。并行输入串行输出 (PISO) 移位寄存器可以进行两种数据加载:同步加载和异步加载。有了这个移位寄存器,就可以将并行形式的数据转换成串行形式的数据。

并行输入串行输出移位寄存器电路图

四、使用 D 触发器的 4 位双向移位寄存器

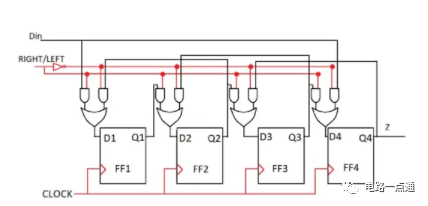

一个 4 位 双向移位寄存器 是一种移位寄存器,其中数据位可以根据需要从左向右或从右向左移位。当Right/Left为高电平时,该电路作为右移位寄存器工作,当它为低电平时,该电路作为左移位寄存器,数据随着该类型寄存器中时钟脉冲的每个正沿而移位。

用D触发器设计的4位双向移位寄存器示意图

五、使用 D 触发器的 4 位通用移位寄存器

这是一个 双向移位 寄存器,其中输入可以串行或并行方式馈送,输出也可以串行或并行方式。这就是为什么它被称为通用移位寄存器。此外,它可以开发一个D触发器,如通用移位寄存器的给定图所示。

使用d触发器的通用寄存器电路图

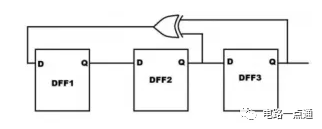

六、使用D触发器的伪随机序列发生器

伪噪声序列 不是真正随机的;它是一个有待确定的有限长度的周期性二进制序列。该 PN序列发生器 可以设计一个线性反馈移位寄存器,而在移位寄存器中,数据随着每个时钟周期从左向右移位。

使用 d 触发器的 PN 序列发生器设计伪噪声序列发生器 采用D触发器和异或门设计;这里的位随着时钟从左向右移位,第三个 D 触发器的输出和第二个 D 触发器的输出一起异或并作为输入馈送到第一个 D 触发器。PN 序列随着所用触发器的数量而增加。

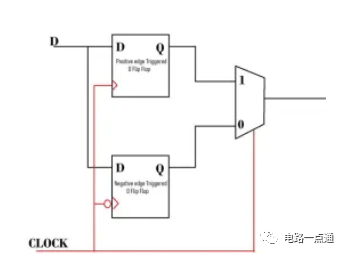

七、双边沿触发 D 触发器

双边沿或双边沿触发 D 触发器 是一种时序电路,可以从时钟脉冲的正负沿选择数据。双边沿触发 D 触发器可以由两个 D 触发器设计为一个正极。正沿 D 触发器输出馈入一个输入数据,负沿 d 触发器输出馈入多路复用器的另一个输入数据。

用 MUX 和 D 触发器设计的双边沿触发 D 触发器

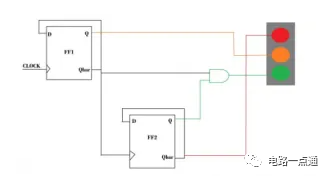

八、使用 D 触发器的交通灯控制器

交通灯控制器 可以用d触发器设计,如图所示,第2个D触发器的Qbar为红灯供电。第一个 D 触发器的 Q 为黄灯供电,而当与门为高电平时,绿灯供电。

用D触发器设计的交通灯控制器示意图

两个D触发器在时钟高电平时都处于切换状态,没有时钟时触发器都处于切换状态;触发器处于保持状态。可通过时钟频率控制每盏灯的持续时间;对于不同的要求,可以改变时钟脉冲频率。

审核编辑:汤梓红

-

rs触发器电路图与rs触发器内部电路图2022-10-19 35285

-

如何用JK触发器构成D触发器 电路图2011-11-14 45841

-

J-K触发器组成D触发器电路图2010-09-24 8987

-

D触发器组成T和J-K触发器电路图2010-09-20 22099

-

双D触发器延时熄灯控制电路图2009-06-13 2492

-

D触发器的制作及电路图2009-05-19 4004

-

时基触发器电路图2009-05-18 636

-

触发器的输入电路图2009-05-08 878

-

基本RS触发器电路图2008-10-20 25983

-

单稳态触发器电路图2008-09-22 3794

全部0条评论

快来发表一下你的评论吧 !