动态功率缩放简介

描述

在当今的数据采集系统(DAQ)中,性能界限不断被突破。系统设计人员需要更高的速度、更低的噪声和更好的总谐波失真(THD)性能,所有这些都是可能的,但没有一个是免费的。这些性能改进通常以更高的工作电流为代价,进而导致更大的功耗。然而,在许多应用中,对功耗的敏感性也是一个日益受到关注的问题。原因多种多样。它可能是一个由纽扣电池运行的远程系统,其中主要关注的是电池寿命,或者可能是一个多通道系统,其中来自高通道数和高电路密度的热量集中会导致温度引起的漂移问题。无论哪种情况,最小化电流消耗和功耗都至关重要。系统设计人员必须在高性能和低功耗的竞争优先级之间取得平衡。实现解决方案的一种途径是通过称为动态功率缩放 (DPS) 的过程。

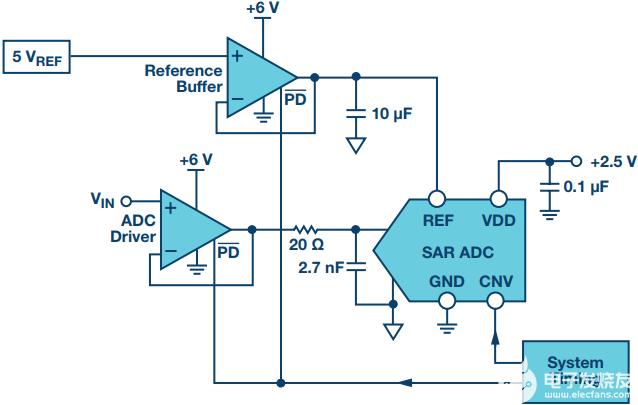

简单地说,DPS是在需要时动态启用电子元件并在不需要时禁用它的过程。图1所示为典型的基于SAR ADC的数据采集子系统。SAR ADC的关键属性之一是其功率与吞吐速率成比例,使其成为功耗敏感型应用非常有吸引力的选择。从历史上看,ADC驱动器和基准电压缓冲器没有共享SAR所享有的自动功率调节功能。它们通常在系统运行时通电并启用,从而消耗多余的功率。假设使能时间足够快,则可以动态驱动放大器掉电引脚,以在ADC转换之间禁用放大器。这就是动态功率缩放。通过将DPS施加到放大器上,可以大大降低其平均电流消耗。对于DPS,放大器静态电流是驱动掉电引脚占空比的函数。理论平均静态电流由下式给出

哪里:

我平均是平均DPS静态电流

我Q_ON放大器的静态电流是否已启用

我Q_OFF放大器的静态电流是否被禁用

t上是放大器使能的时间

tS是采样频率周期

图1.基于SAR ADC的数据采集子系统框图

在本文的其余部分,ADC驱动放大器将是重点,但DPS概念也可以应用于基准电压缓冲器,结果类似。

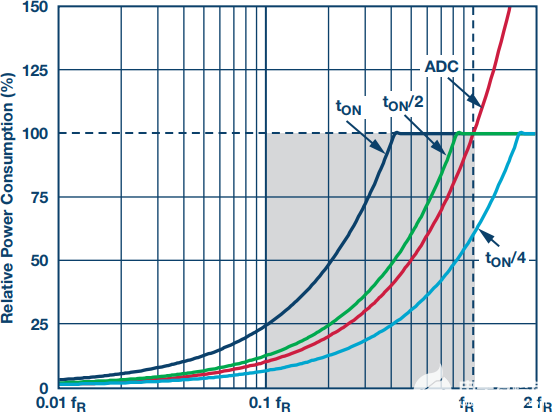

图2显示了ADC驱动放大器持续使能时的理论效率改进情况。f 处的垂直参考线R表示ADC的功耗等于持续使能的驱动放大器的功耗时的采样频率。在较低的采样速率下,放大器主导功耗,在较高的采样速率下,ADC主导功耗。参考频率(fR) 将根据放大器和所选 ADC 的功耗而变化,但基本概念保持不变。显示了功率调节的同一放大器在三个不同值的t下相对效率改进上.正如预期的那样,较短的t上在给定采样率下提高效率,并允许在更高的采样率下使用 DPS。阴影区域表示,增量缩短的改进面积最大 t上通常向下延伸至低于f的十年左右R.当采样率继续降低到该点以下时,实现了最大的整体节能,但进一步缩短了上可以忽略不计,因为功耗逐渐接近掉电或禁用状态的功耗。

图2.选定温度下DPS的理论放大器功耗上(相对于放大器持续启用)。

为了使用DPS实现最佳性能,系统定时和最小值的确定上至关重要。

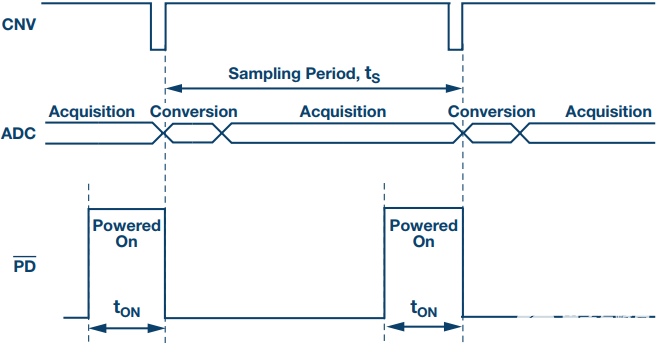

图3显示了ADC和驱动器放大器的简化时序图。图1所示的系统时序模块(FPGA、DSP和微控制器)提供适当定时的ADC转换启动(CNV)和放大器关断(PD)信号。SAR ADC在CNV的上升沿启动转换。放大器在ADC采集阶段上电一段时间(t上)之前,然后与CNV的上升沿同步断电。但是正确的时间段是多少上?

图3.放大器和ADC控制信号的简化时序图。

虽然图 2 说明了使用任意时间对 t 进行的概念上,它清楚地表明,只有当最小值上被使用。这是放大器在ADC转换之前必须使能的最短时间,以确保获得准确的结果。任何短于此时间都会导致SNR或THD的侵蚀,而任何更长的时间都不会导致任何性能改进。在实践中,最小值 t上在采样率范围内不是恒定的,必须根据经验确定的独特应用。最小值 t上将因放大器和系统而异。例如,在图1电路中使用ADA4805-1和AD7980的放大器/ADC组合,最小值为”上随着采样速率的增加而降低,在1 kSPS时通常需要~4 μs,在1 MSPS时只需要~600 ns。在低采样速率下,由于掉电状态的时间延长,较长的周期为内部放大器节点提供了更多的放电时间,从而导致更长的导通时间。相反,较短的较高采样率周期不允许进行尽可能多的内部放电。事实上,随着采样速率的增加,放大器的有限关断时间将变得比掉电状态下的时间更长。实际上,放大器在完成关闭之前重新打开。这看起来像是人为地快速开启时间,但在性能数据显示没有下降时会得到验证。

预测潜在的节能时要考虑的最后一点是输入信号频率的影响。到目前为止,DPS的概念已经使用给定放大器的静态电流计算出来。将信号施加到放大器输入端时,动态电流也会随着输入信号频率的增加而增加。如果输入频率足够低,则影响无关紧要。随着频率的增加,放大器输出端的RC网络呈现出更重的负载,需要放大器提供更多的电流来处理信号。

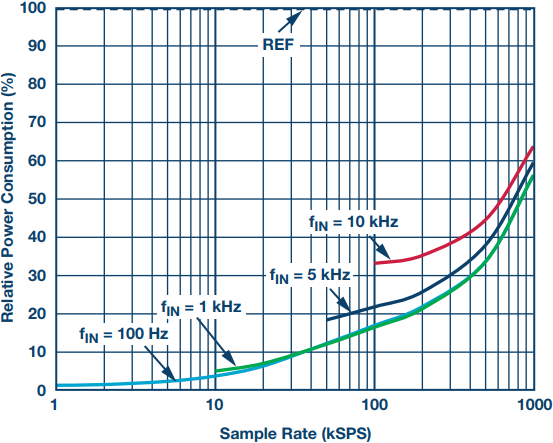

使用前面提到的ADA4805-1和AD7980,将这些概念放在一起,得到图4中的曲线。该图显示了动态功率调节的ADC驱动器放大器在持续使能时相对于同一放大器的功耗(以百分比表示)。绘制了所选输入频率的DPS效率图,以说明较高输入频率对功耗的影响。最小值 t上针对从 1 kSPS 到 1 MSPS 的多个采样速率确定,定义为最短的上这会导致放大器持续使能的情况下SINAD(信噪比和失真)衰减<0.5 dB。该图显示,在低采样率下处理慢速输入信号时,可实现高达95%的节能。但更重要的是,对于更高吞吐量的系统,潜在的节省仍然很大,在100 kSPS时高达65%,在1 MSPS时高达35%。需要注意的是,图4反映了连续采样系统中单个单位增益缓冲器的性能。但是,如前所述,这些DPS概念可以很容易地应用于基准电压缓冲器,并期望获得类似的结果。

图4.具有动态功率缩放的相对放大器功率—实验结果。

虽然DPS是一个相对较新的概念,并且需要考虑设计和时序考虑因素,但初步结果是有希望的。有一点非常清楚,对更高性能和更低功耗的渴望将持续到未来,这将进一步增加对创造性低功耗解决方案的需求。

审核编辑:郭婷

-

《Visual C# 2008程序设计经典案例设计与实现》---动态打开、显示和缩放图像2017-07-08 2047

-

8168缩放问题,请问mpsclr是不是固定缩放到1920*1080?2018-06-22 1617

-

是否可以针对WiFi调整PHY的动态速率缩放算法呢?2023-03-01 593

-

用TPS62200作为OMAP1510的动态电压缩放器2009-12-21 1107

-

TPS62200可调式降压型转换器实现动态电压缩放技术电路图2010-03-30 1241

-

Protel99鼠标缩放软件2017-11-29 1176

-

基于概率随机裁剪的图像缩放算法2018-01-17 1052

-

AN-1289:在无动态功率控制的应用中使用AD5755和类似的动态功率控制DAC2021-03-21 658

-

AD7768-1:DC至204 kHz,动态信号分析,带电源缩放功能的精密24位ADC数据表2021-04-23 805

-

使用缩放布局案例效果演示2022-03-21 454

-

使用HLS封装的缩放IP来实现视频图像缩放功能2022-10-11 3851

-

功率密度基础技术简介2022-10-31 836

-

随温度变化的动态电压缩放实现2023-09-13 468

-

具有动态电压缩放功能的双同步降压DC-DC变换器LM3370数据表2024-04-10 469

-

使用功率缩放库2024-10-18 294

全部0条评论

快来发表一下你的评论吧 !