3D NAND结构给制造过程带来的挑战

描述

3D NAND闪存实现了新一代的非易失性固态存储,适用于几乎所有我们可以想像得到的电子设备。

3D NAND能够实现超过2D NAND结构的数据密度,即便是在新一代技术节点上制造时也是如此。

然而,目前提高3D NAND存储容量的方法可能会带来一些在存储器储存、结构稳定性和电气特性方面的不利影响。

3D NAND器件及其工作原理

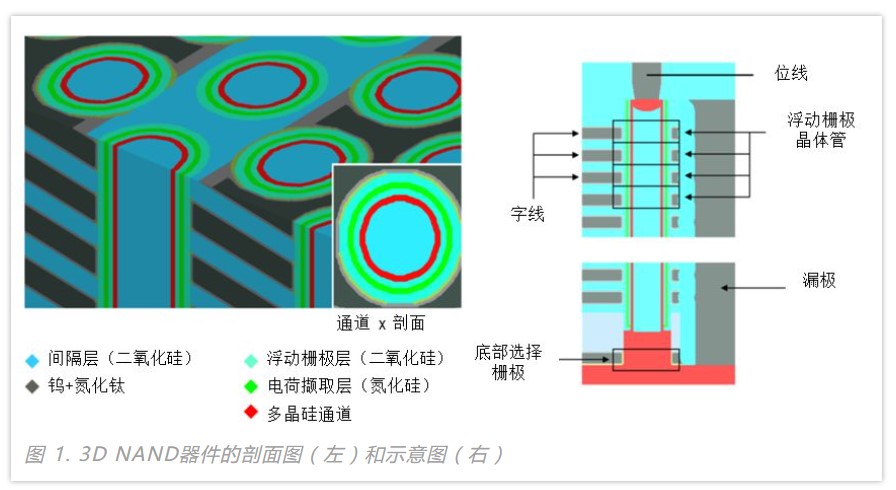

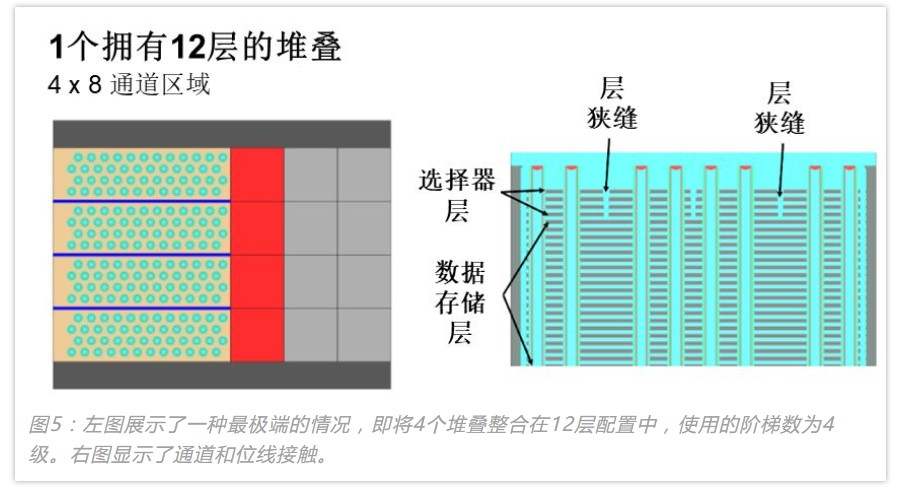

3D NAND器件包括三个主要组成部分:一是存储数据的通道区域,它以垂直方式穿过交替堆叠的导体层和绝缘层;二是“阶梯”,用于访问上文提及各层中的每个字线;三是狭缝,用于隔离连接位线的通道。下图展示了3D NAND堆叠的剖面图(左)与示意图(右):

如上图所示,电荷撷取型3D NAND结构采用钨和二氧化硅的交替堆叠,其垂直圆柱状通道穿透整个堆叠。当电压施加到字线时,电子通过隧道从通道区域移动到由氮化硅组成的电荷撷取层,数据被写入或擦除。

存储容量挑战

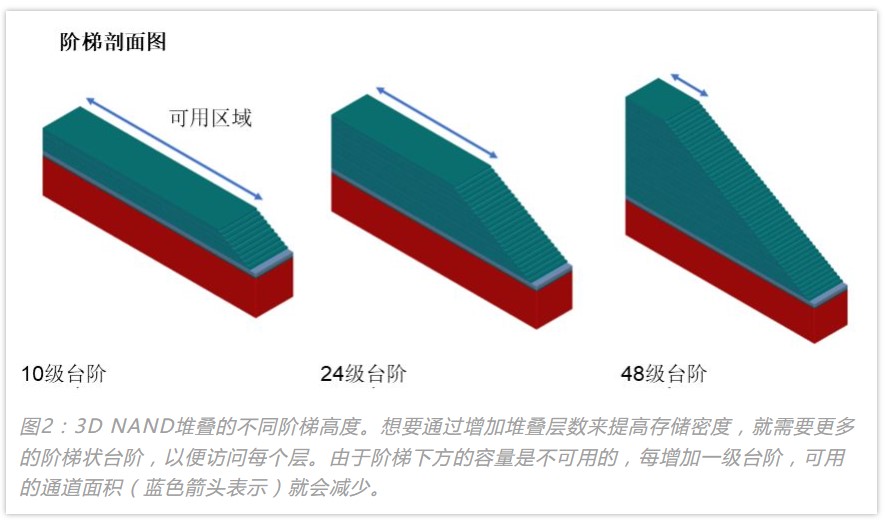

虽然3D NAND存储容量的提高看似可以通过添加更多堆叠层非常轻松地实现,但堆叠高度的增加会带来很大的挑战。如下图所示,通道的可用面积将会减小:

随着“阶梯”高度的提高,可用的空间随之减少。在某些类型的3D NAND中,由于去除了阶梯“台阶”之间的牺牲层,产生了更多的挑战。

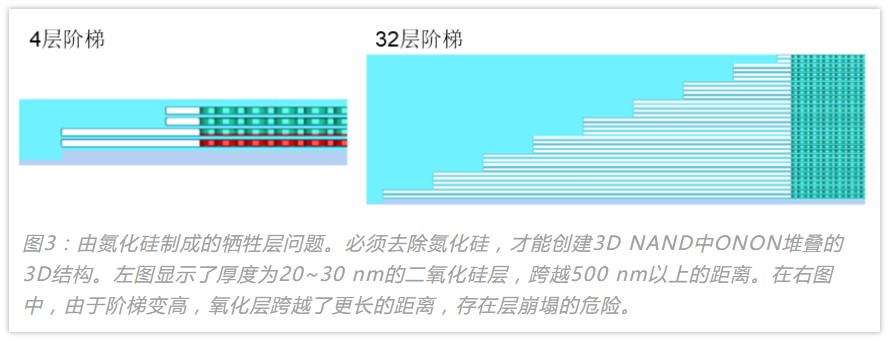

在这些结构中,工程师通过湿法刻蚀去除牺牲层,是为了给之后制造工艺中的原子层沉积创造空间。

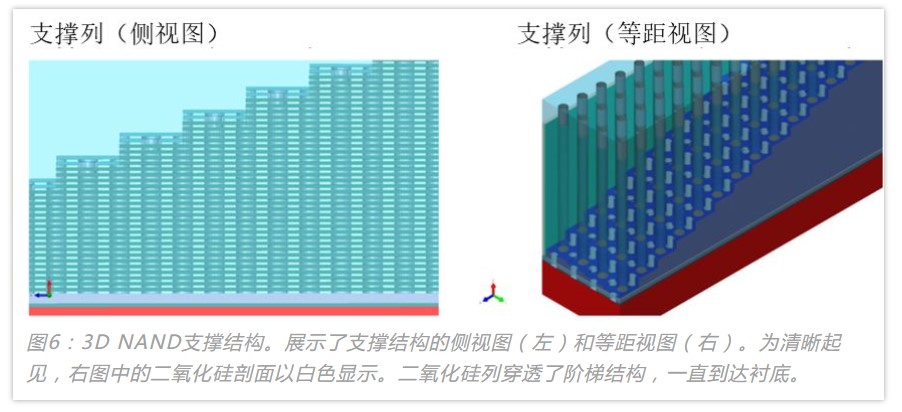

因此,更高的阶梯意味着有更长的隔离层将悬浮在空中,也意味着结构崩塌的可能性更高:

对台阶进行分区,可在台阶结构中插入更多字线接触通孔,从而创建更紧凑的阶梯,而不出现崩塌的危险。

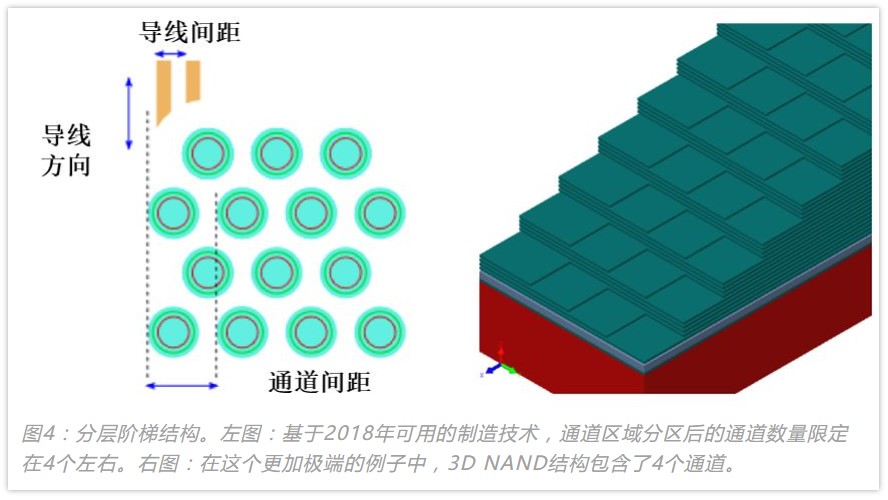

但是,由于所有通道必须进行电气隔离,可访问通道的数量取决于适应通道间距的最小导线间距(假设每个通道都有自己的导线)。

基于目前的制造技术(2018年底/2019年初),分区后的通道数量被限制在四个左右:

但是,更宽的堆叠(因需要的狭缝数量少而受用户欢迎)可能包含四个以上的通道,它们需要被分成多个周期组。

通过使用刻蚀工艺来穿透一部分层,将通道组隔离,有效地使用几个浮动栅级层作为选择器晶体管:

支撑列影响分析

由于3D NAND的制造工艺非常复杂,因而我们很难全面理解在存储容量和稳定性方面的各种权衡因素,以及由于在堆叠中添加更多层、台阶分区、层穿透而导致的其他属性变化。

以下所示的虚拟工艺模型模拟了建议的制造步骤。我们使用SEMulator3D®来测试不同支撑列数量和接触通孔尺寸产生的结果。

所添加的列用于在去除阶梯层之间的牺牲材料过程中支撑整个结构,它的孔由刻蚀形成,并用二氧化硅填充。

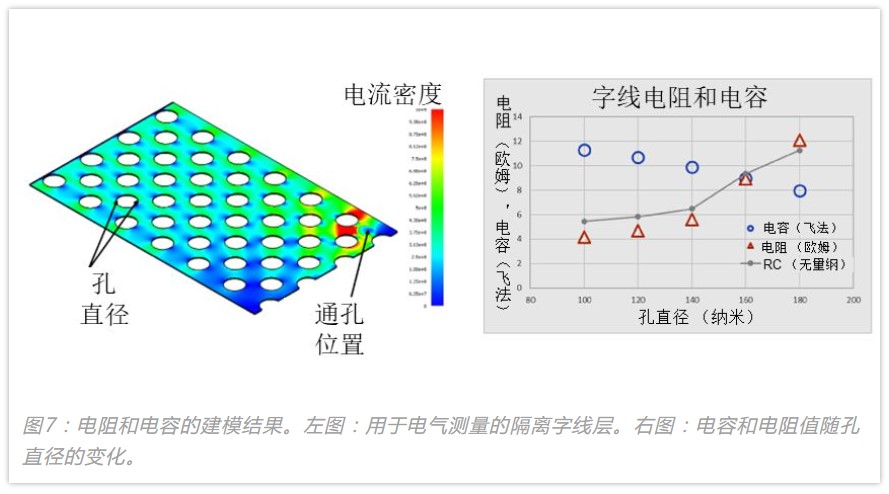

在对Semulator3D模型执行的电气分析中,我们研究了隔离字线层,并模拟了列尺寸对电阻和字线电容的影响(在右图中,孔直径表示列宽度):

扩大支撑列可以提供更好的结构稳定性,但会增加字线电阻,占用更多的空间。

因此,在器件的结构完整性允许的情况下,最大程度地减小支撑列的尺寸和数量对器件结构是有帮助的。

本研究展示了分层3D NAND阶梯结构的实际工艺模型。我们还应用了虚拟的制造技术,加深在使用支撑列增强高密度存储结构稳定性过程中的各种权衡因素的理解。

审核编辑:刘清

-

3D混合制造技术介绍2019-07-08 2112

-

3D NAND技术资料分享2019-09-12 2821

-

芯片的3D化历程2020-03-19 2146

-

3D NAND与4D NAND之间的差别在哪儿?2021-06-18 3062

-

干货!一文看懂3D NAND Flash2016-08-11 44657

-

OPPO Find X的FaceKey 3D结构光给力 期待oppo findx兰博基尼版2018-07-20 4160

-

美光扩大在新加坡的研发业务,致力于制造3D NAND闪存2018-08-01 2935

-

半导体行业3D NAND Flash2018-10-08 777

-

浅析3D结构光技术2018-10-23 21997

-

随着更高性能的存储火爆 也给3D Xpoint带来了新的机会2019-01-19 1339

-

旺宏将于2020年开始出货3D NAND2019-12-14 5955

-

未来的3D NAND将如何发展?2020-11-20 3079

-

什么是3D NAND闪存?2023-03-30 4189

-

请问3D NAND如何进行台阶刻蚀呢?2024-04-01 2338

-

3D闪存的制造工艺与挑战2025-04-08 2004

全部0条评论

快来发表一下你的评论吧 !