设计资料原理图ORihard KCU116E: 100Gbps 网络和存储 FPGA 开发平台

电子说

描述

ORihard KCU116E: 经济实惠的 100Gbps 网络和存储 FPGA 开发平台

Kintex® UltraScale+™ 系列被认为是 Xilinx® 基于 TSMC 16 nm FinFET 技术构建的、具有“价格/性能/瓦特”平衡比的 FPGA 器件。结合皆为新的 UltraRAM 和互连优化技术 (SmartConnect),该器件为需要通过高端功能收发器实现 100 Gbps 连接内核的应用提供了最经济实惠的解决方案。这个系列专门为网络和存储应用而设计,如网络包处理和无线 MIMO 技术、100 Gbps 有线网络、工业和数据中心网络加速以及 NVMe SSD(固态硬盘)存储加速。本文通过使用 Design Gateway 的 TOE100G-IP 内核和 NVMeG4-IP 内核,在 Xilinx 的 KCU116E 评估套件上演示了 TCP 卸载引擎网络和 NVMe SSD 实现的100Gbps 解决方案。其中,TOE100G-IP 内核用于在 100 GbE 接口上进行 12GB/s TCP 传输的 CPU 解决方案,而 NVMeG4-IP 内核则能够实现每个 SSD 约 4GB/s 的难以置信的快速传输性能。

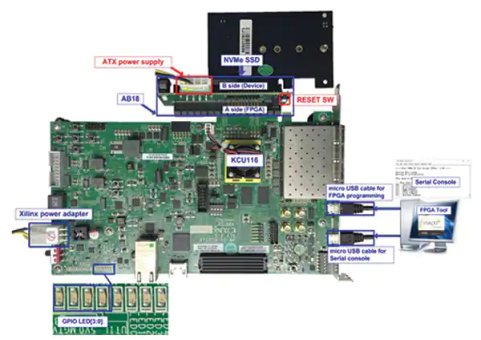

Kintex® UltraScale+ KCU116E 评估套件简介

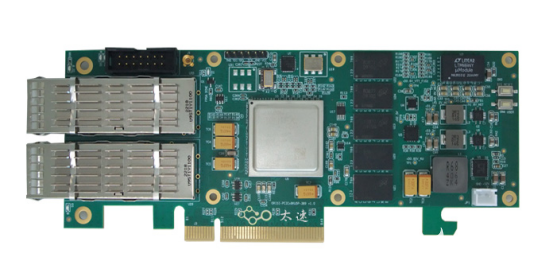

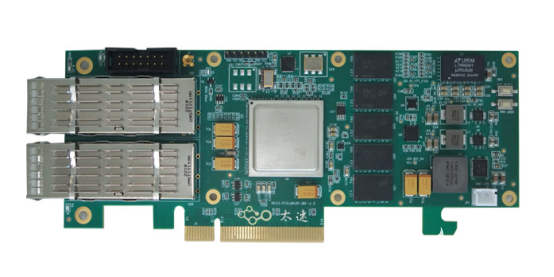

KCU116E 非常适用于评估 Kintex UltraScale+ 的关键功能,尤其是 28 Gbps 收发器性能。该套件非常适用于基于 XCKU5P-2FFVB676E FPGA 器件的快速原型开发。

板上包括一个板载的 1GB 64 位 DDR4-2666、以及用于多达 2 个 M.2 NVMe SSD 接口的 PCIe Gen4 x8 通道。16 x 28 Gbps GTY 收发器可用于组成 PCIe Gen4 X8和 2个100 GbE 接口,并提供各种外设接口和 FPGA 逻辑以方便用户进行定制设计。

图 1:KCU116E 评估套件。

通过搭配 Design Gateway 的 IP Cores,KCU116E 能提供开发最先进的 100Gbps 网络和存储解决方案所需的一切,而且不需要 MPSoC 支持。

实现 100Gbps 网络和存储解决方案

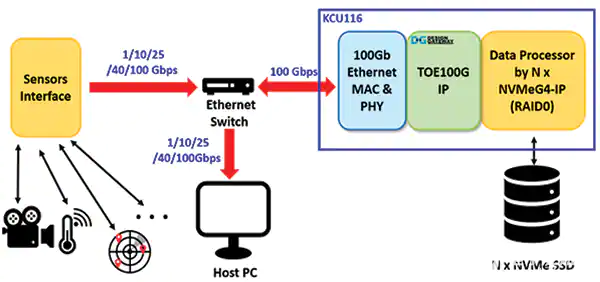

图 2:KCU116E 的 100Gbps 网络和存储解决方案。(图片来源:Design Gateway)

尽管 Kintex UltraScale+ 器件不像 Zynq UltraScale+ 那样采用了 MPSoC 技术,但通过利用 Design Gateway 的 IP Cores 解决方案,可以实现网络和 NVMe 存储协议处理,无需处理器和操作系统。

1. TOE100G-IP:100GbE 全 TCP 协议栈 IP Core,无需 CPU

2. NVMeG4-IP:独立的 NVMe 主机控制器,内置 PCIe Gen4 IP 软核

TOE100G-IP 和 NVMeG4-IP 都可以在不需要 CPU/OS/驱动的情况下运行。对于使用这两种 IP 的控制和数据路径的用户逻辑,可以由 Microblaze 的纯硬件逻辑或裸机操作系统来实现,以使高层应用和算法的开发更快、更容易,而无需担心复杂的网络和 NVMe 协议。这为先进的系统级解决方案创造了新的机会,如传感器数据采集、板载计算和基于 AI 的边缘计算设备。

Design Gateway 的 TOE100G-IP 用于 UltraScale+设备

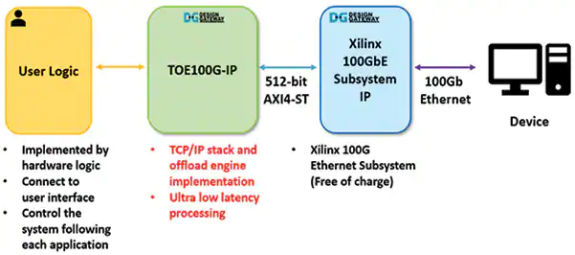

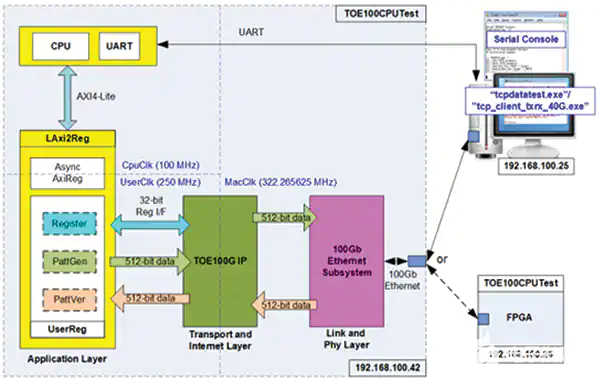

图 3:TOE100G-IP 系统。(图片来源:Design Gateway)

TOE100G IP 内核执行 TCP/IP 协议栈(在硬线逻辑中),与 Xilinx 的 100Gb 以太网子系统模块连接,用于下层硬件。TOE100G IP 的用户接口包括一个用于控制信号的寄存器接口、一个用于数据信号的 FIFO 接口。TOE100G IP 旨在与 100Gb 以太网子系统连接,后者使用 512 位 AXI4-ST 连接至用户接口。Xilinx 提供的以太网子系统包括 EMAC、PCS 和 PMA 功能。100Gb 以太网子系统的用户接口时钟频率等于 322.265625 MHz。

TOE100G-IP 的特点

· 完整的 TCP/IP 堆栈实施

· 一个 TOE100G IP 支持一个会话(可通过使用多个 TOE100G IP 实现多重会话)

· 同时支持服务器和客户端模式(被动/主动打开和关闭)

· 支持 Jumbo 框架

· 通过标准 FIFO 接口提供简单的数据接口

· 通过单端口 RAM 接口进行简单的接口控制

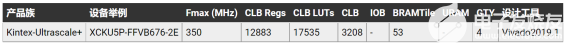

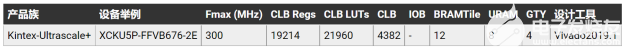

XCKU5P-2FFVB676E FPGA 器件上的 FPGA 资源使用情况如下表 1 所示。

表 1:Kintex Ultrascale+ 器件的使用统计示例

有关 TOE100G-IP 的更多详情,请参阅其规格书。可从 Design Gateway 网站下载规格书。

Design Gateway 的 GTY 收发器的 NVMe PCIe Gen4 主机控制器

Kintex UltraScale+ 有一个 GTY 收发器,能够支持 PCIe Gen4 接口,但不含 PCIe Gen4 集成块和 ARM 处理器。

Design Gateway 通过开发 NVMeG4-IP 内核解决了这个问题,该内核能够作为独立 NVMe 主机控制器运行并在单个内核中内置 PCIe 软 IP 和 PCIe 桥接逻辑。NVMe PCIe Gen4 固态硬盘访问的启用简化了用户界面,使标准功能设计易于使用,而不需要掌握 NVMe 协议的知识。

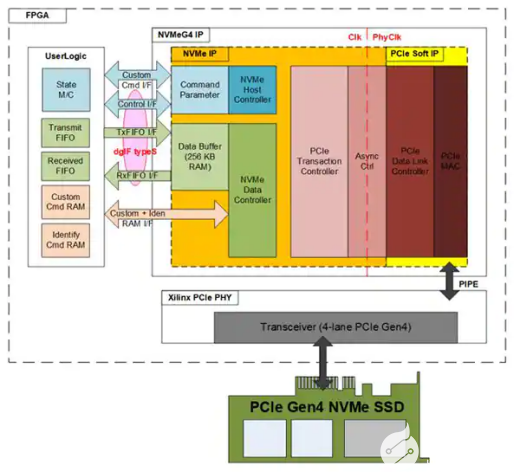

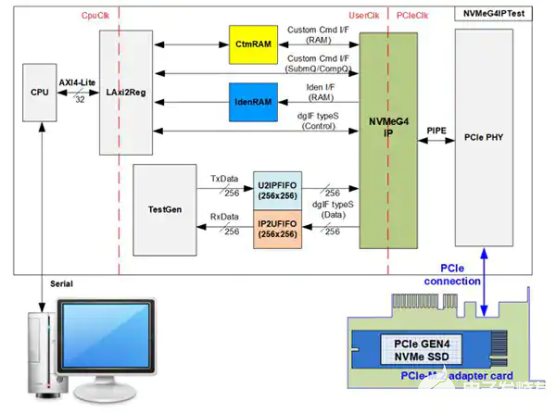

图 4:NVMeG4-IP 框图。(图片来源:Design Gateway)

NVMeG4-IP 的特点

· 能够实现应用层、事务层、数据链路层和物理层的某些部分在没有 CPU 或外部 DDR 存储器的情况下访问 NVMe SSD

· 使用配置为 4 通道 PCIe Gen4(256 位总线接口)的 Xilinx PCIe PHY IP 进行操作

· 包含 256 KB RAM 数据缓冲区

· 支持六条命令,即识别、关断、写入、读取、SMART 和刷新(可选择支持其他命令)

· 用户时钟频率必须大于或等于 PCIe 时钟(Gen4 为 250 MHz)

XCKU5P-2FFVB676E FPGA 器件上的 FPGA 资源使用情况如下表 2 所示。

表 2:Kintex Ultrascale+ 器件的实施统计举例

有关 NVMeG4-IP 的更多详情,请参阅其规格书。可从 Design Gateway 网站下载规格书。

在 KCU116E 上实施 TOE100G-IP 的举例和性能结果

图 5 所示为基于 KCU116E 的参考设计,以展示 TOE100G-IP 的应用情况。该演示系统包括裸机操作系统 Microblaze 系统、用户逻辑和 Xilinx 的 100Gb 以太网子系统。

图 5:TOE100G-IP 演示系统框图。(图片来源:Design Gateway)

该演示系统专们用于评估 TOE100G-IP 在客户端和服务器模式下的操作。使用测试逻辑功能,可在测试模式下发送和接收数据,以便在用户界面侧获得尽可能高的数据速度。对于使用 KCU116E 的 100GbE 接口,需要四个 SFP+ 收发器 (25GBASE-R) 和光纤电缆,如图 6 所示。

图 6:在 KCU116 上安装的 TOE100G-IP 演示环境。(图片来源:Design Gateway)

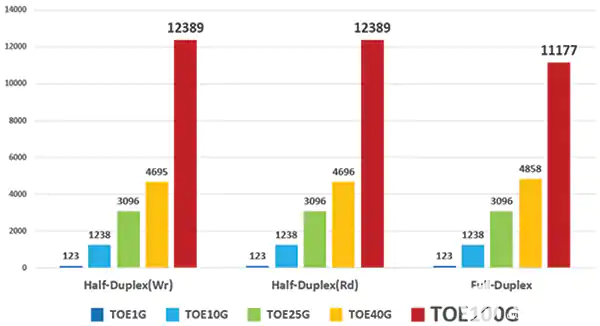

图 7 显示了 100G 与其他 (1G/10G/25G/40G) 比较时的示例测试结果。

图 7:TOE100G-IP 与 KCU116E 上的 1G/10G/25G/40G 性能比较。(图片来源:Design Gateway)

测试结果表明,TOE100G-IP 能够实现大约 12GB/s 的 TCP 传输速度。

在 KCU116E 上的 NVMeG4-IP 实施和性能结果示例

图 8 所示为基于 KCU116E 的参考设计,以展示 1CH NVMeG4-IP 的实施情况。如果用户定制设计的 FPGA 资源可用的话,可以实施 NVMeG4-IP 的多个实例以实现更高的存储性能。

关于 NVMeG4-IP 参考设计的更多详情,请参考 Design Gateway 网站上提供的 NVMeG4-IP 参考设计文件。

图 8:NVMeG4-IP 参考设计概览。(图片来源:Design Gateway)

该演示系统旨在通过 KCU116E 上的 NVMe SSD 写入/验证数据。用户可通过串行控制台控制测试操作。为了使 NVMe SSD 与 KCU116E 连接,需要一块 AB18-PCIeX16 适配器板,如图 9 所示。

图 9:在 KCU116E 上安装的 NVMeG4-IP 演示环境。(图片来源:Design Gateway)

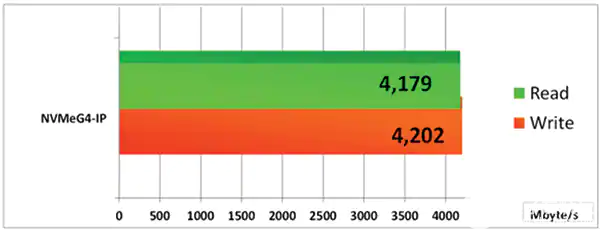

使用 512 GB Samsung 970 Pro 时,在 ZCU116 上运行演示系统的示例测试结果如图 10 所示。

图 10:使用 Samsung 970 PRO S 时,ZCU116 上 NVMe SSD 的读/写性能。(图片来源:Design Gateway)

结语

TOE100G-IP 和 NVMeG4-IP 内核都提供了在 KCU116E 板上使用 100Gbps 连接功能的解决方案,可实现网络和 NVMe 存储应用。一个 TOE100G-IP 能够在 100GbE 上进行大约 12GB TCP 传输。NVMeG4-IP 可以通过 NVMe PCIe Gen4 提供卓越的高性能存储,每块 SSD 的速度约为 4GB/s。NVMeG4-IP 的多个实例可用于组成 RAID0 控制器,并可提高存储性能,以匹配 100GbE 的传输速度。

利用 KCU116E 评估套件和 Design Gateway 的网络与存储 IP 解决方案,就有可能以最少的 FPGA 资源实现最高性能的目标,从而获得基于 Xilinx® Kintex UltraScale+® 器件的、经济实惠的解决方案或产品。

审核编辑 黄昊宇

-

聊聊高速PCB设计100Gbps信号的仿真2025-03-17 1186

-

资料#BananaPi BPI-F2S FPGA开发平台硬件原理图2022-09-01 22145

-

升特推出首个高频宽100Gbps Gearbox芯片组2011-03-29 3145

-

Altera首次演示FPGA与100Gbps光模块的互操作性2012-02-24 1621

-

博通推出业界首款100Gbps全双工网络处理器单元BCM880302012-04-28 3774

-

TeliaSonera建成全球首个横跨欧美100Gbps网络2013-03-21 1204

-

100Gbps数据吞吐量?Samtec can do it!2017-12-15 2584

-

Xilinx Kintex UltraScale+ FPGA KCU116评估套件主要性能和优势2018-07-05 7715

-

MC100E116 ECL Quint差分线路接收器2019-04-18 361

-

诺基亚与沃达丰正试验100Gbps速度的宽带技术2021-02-03 2026

-

开源100 Gbps NIC Corundum环境的搭建2022-08-02 2946

-

Xilinx KCU116:经济高效的 100 Gbps 网络和存储 FPGA 开发平台2022-11-24 293

-

寻找开源100G NIC Corundum中的隐藏BUG2023-05-23 2472

-

中国移动发布广域高吞吐100Gbps网卡2024-10-12 1674

-

5V ECL Quint Differential Line Receiver MC10E116和MC100E116的特性与应用2026-04-11 292

全部0条评论

快来发表一下你的评论吧 !