MIMXRT1021CAG4B GPIO口复位值详解

电子说

描述

在MIMXRT1021CAG4B使用中,当系统上电后,发现不同的端口在通电后具有不同的值。例如,现在使用GPIO_EMC_39和唤醒引脚,两者结果是不同的。从GPIO数据手册中,GPIO DATA寄存器的复位值为0x00000000。但对于唤醒引脚,复位后状态后为高电平。

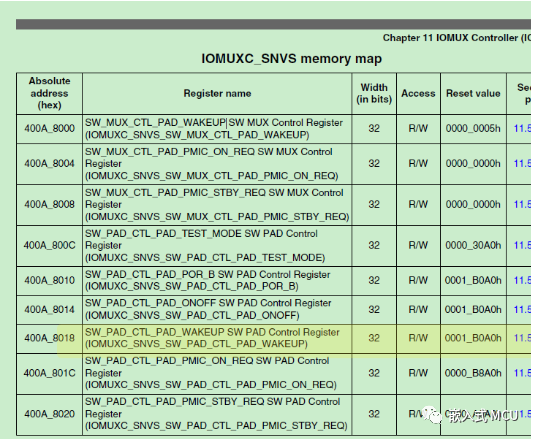

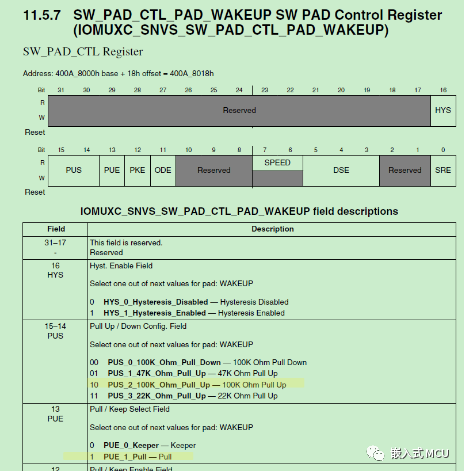

-> GPIO引脚默认为输入功能,而非输出功能。因此,它由上拉和下拉配置决定。对于唤醒PIN,可以检查以下寄存器:

默认情况下,使能了内部100K上拉,因此上电复位后,GPIO口是高电平。针对 GPIO_EMC_39 也是一样的,如果添加DCD将配置SDRAM SEMC端口,它将由SEMC配置结果决定。在从QSPI加载应用程序代码之前,如下相关信号被驱动为HIGH,为什么呢?

| GPIO_PAD | DEFAULT SIGNAL |

| GPIO_EMC_08 | SEMC_DM00 |

| GPIO_EMC_29 | SEMC_CS0 |

| GPIO_EMC_39 | SEMC_DQS |

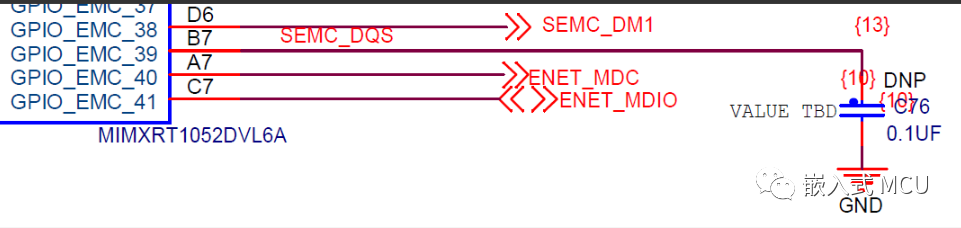

问题是,将上述这些信号用作GPIO,并将其用作电机的启用以及打开/关闭阀门的控制。这些信号具有相当强的下拉电阻,因此认为处理器正在积极地将这些信号配置为输出并将其驱动为高电平。为什么这些信号在通电时会短暂地切换到高电平,如何防止这种情况发生吗?

->该问题与DCD配置有关。在RT1020EVK上做了一个快速测试,没有看到这个问题。可以检查C76处的电压以确定GPIO_EMC_39引脚状态。

还有一种应用场景,需要在固件升级后保留输出状态。通常它需要在固件升级后重新启动,但在重新启动期间输出状态将会被重置。如何实现在固件升级后保持输出状态高电平呢?

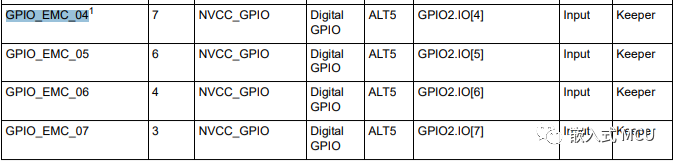

事实上,GPIO输出状态由代码控制,如果更新固件,然后复位,代码将运行,GPIO状态完全由代码控制。但是在复位期间,可以外接上拉电阻,因为,如果引脚是输入Keeper的,那么它是由外部信号决定的。GPIO_EMC_05和06中的Keeper 电路已启用,在复位期间将输出高电平。但对于GPIO_EMC_04,它将在复位期间用作调试 JTAG_ACT功能,它将输出低电平。

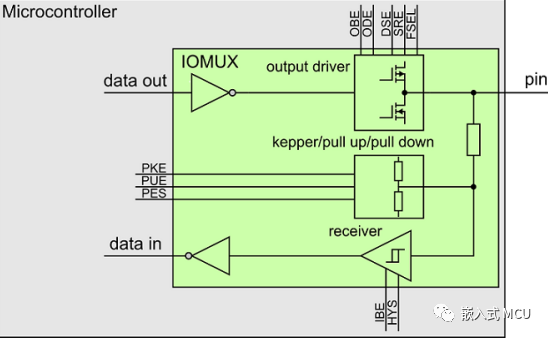

当输出驱动器被禁用时,Keeper功能够保持先前的输出值。

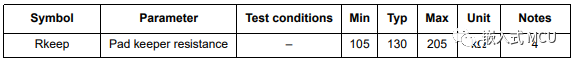

Keeper的内部电阻远高于标准输出驱动器的内部电阻——见上表。此选项对于在逻辑值更改时需要大量能量的应用中节省功耗,但在仅需要保持状态时几乎不需要消耗能量。另一种类型的应用是必须确保引脚在任何情况下都被驱动,即使强度小得多,因此输出引脚不会浮空,并且其电平被定义。

pull / keeper 由PKE、PUE和PUS位控制。pull / keeper 可通过pull / keeper 启用(PKE)位启用。当pull / keeper 启用时,可以选择PUE(上拉启用)位启用器件对应的功能。

I2C / I2S 要求双向通信,如下位在 IOMUX中需要配置:

• 输入 IBE = 0b1

• 输出 OBE = 0b1

• 开漏功能 ODE = 0b1

• 针对低频信号的配置 PKE = 0b1, PUE = 0b1, PUS = 0b11或者外接上拉用于固定的或者高频信号

审核编辑:汤梓红

-

如何使用SD卡启动MIMXRT1024CAG4B?2023-05-05 694

-

CAG4M-FP-FA 初级用户手册 CAG4M-FP-FA V850E/CAG4-M 闪存编程适配器用户手册2023-04-27 449

-

MIMXRT1021CAG4A无法正常启动是为什么?2023-04-18 799

-

比较器MIMXRT1020-EVK引脚更改示例问题求解2023-03-16 491

-

MIMXRT1062CVL5B和MIMXRT1062XVN5B的区别2022-12-06 3418

-

MIMXRT1021和MIMXRT1024 ADC通道数2022-12-02 3986

-

MIMXRT1064CVL5B连接HyperRAM2022-11-08 3288

-

在MIMXRT1021CAG4B MCU上打印printf()到指定的串口2022-11-07 1474

-

rt1021编译出错请问如何处理2022-10-20 1224

-

GPIO寄存器详解2022-01-18 1076

-

STM32单片机GPIO口简介2021-12-28 1465

-

【STM32】STM32F4 GPIO八种模式及工作原理详解2021-11-26 1705

全部0条评论

快来发表一下你的评论吧 !