差分运算放大器驱动器可保护高分辨率ADC免受输入过压影响

描述

本应用笔记讨论如何有效保护ADC,使其免受运算放大器驱动器引起的输入过压的影响。新型MAX44205为180MHz、低噪声、低失真、全差分ADC驱动器,内置箝位功能,使驱动器输出摆幅保持在ADC的额定电源范围内。

介绍

具有超低失真和噪声的高性能、全差分运算放大器对于实现高分辨率和低总谐波失真(THD)至关重要。运算放大器(我们在这里简称为驱动器)在ADC的前端执行各种操作。驱动程序处理缓冲和幅度缩放。它将单端输入转换为差分输出,为ADC的差分输入供电。它通过VOCM引脚上的电压设置来调整ADC的共模输入信号,并对信号进行滤波。

在本应用笔记中,我们将说明如何有效保护ADC免受运算放大器驱动器引起的输入过压的影响。新型MAX44205为180MHz、低噪声、低失真、全差分ADC驱动器,内置箝位功能,使驱动器输出摆幅保持在ADC的额定电源范围内。这种硬箝位可保护ADC免受其输入端过压的影响;该驱动器和ADC之间无需额外的外部分立元件即可实现箝位保护。与传统的保护二极管方法相比,这种设计节省了空间和成本。

保护ADC免受输入过压影响的重要性

由于高性能ADC价格高,系统设计人员必须选择能够保护ADC免受过压影响的驱动器。当今的18位/20位ADC使用的基准电压/电源电压不超过3.3V,但ADC驱动器通常使用±5V分离电源或更高的电压。驱动器 V 上的负电压党卫军引脚用于适应整个ADC轨到轨输入信号摆幅。这里有一个警告。根据驱动器的输入信号,其输出可能远远超出ADC输入电源。如果我们不将驱动器输出电压箝位到ADC电源电压以内,ADC可能会永久损坏。

市场上的大多数ADC在两个电源轨的输入端都有ESD保护二极管,但这些二极管在永久损坏之前无法处理>20mA至50mA量级的电流超过几秒钟。即使长时间通过内部ESD二极管泄漏也会损坏保护二极管和ADC。

大多数设计人员在驱动器输出端使用齐纳二极管或肖特基二极管来限制ADC的输入信号摆幅。该钳位解决方案需要四个分立二极管和限流电阻。还有另一种选择。MAX44205为180MHz、低噪声、低失真、全差分运算放大器驱动器,内置箝位,将输出摆幅限制在ADC电源范围内。因此,它可以保护ADC免受输入端过压的影响。该驱动器的钳位特性省去了四个额外的分立元件,节省了PCB空间和成本。

离散地实施夹紧

设计人员使用肖特基二极管来箝位ADC输入电压。这是一个很好的方法,因为这些二极管提供~0.25V至0.4V的最低正向压降电压,具体取决于流经它们的电流。肖特基二极管还有其他三个重要优点:1)非常低的反向漏电流;2)寄生电容较小;3)非常快的反向恢复时间。在肖特基二极管的这三个优点中,低反向漏电流和较小的寄生电容在精密ADC应用中至关重要。第三个优点是快速反向恢复时间,当二极管进入箝位和箝位的速度至关重要时非常有用。

虽然肖特基二极管的寄生电容很小,但设计人员必须选择电容随施加到二极管的反向电压变化变化最小的二极管。这种非线性效应对于谐波失真很重要的应用至关重要。

齐纳二极管还用于箝位电压,其中需要粗箝位 工作时,齐纳二极管具有较高的反向漏电流,使其对ADC应用的效率较低。

图1显示了使用肖特基二极管在ADC输入端实现预定电压电平的电压箝位的基本方法。

图1.带肖特基二极管的基本电压钳位方案。

图1使用两个BAT42 Vishay®肖特基二极管。当ADC驱动器输出超出正ADC电源时,正电源电压的每个输出上的两个肖特基二极管开始导通;二极管将这些节点的电压电平维持在3.3V,加上这些二极管的正向压降。请注意,肖特基二极管的正向压降电压因二极管的功率处理能力而异。因此,应选择具有较低正向压降规格且正向连续电流规格适合应用的肖特基二极管。

在四个电阻中,R限制限制流过肖特基二极管并进入稳压器提供的 3.3V 电源轨的电流。R系列保护ADC的内部ESD保护二极管。设计人员必须调整这些电阻的尺寸,以将电流保持在应用的可管理水平。

R型限制电阻还有助于减少流入稳压器的电流,即3.3V电源轨。如果不限制此电流,稳压器的输出电压可能会增加,并使用电路板的相同稳压器输出电源损坏其他IC。如果您知道ADC驱动器的电流不能超过~100mA,则有另一种方法。不要对串联电阻使用限流电阻。驱动器和ADC之间的RC抗混叠滤波器将通过外部肖特基二极管的电流限制在~10mA的可管理水平。

所以重复一遍,R限制电阻有助于限制流入 3.3V 电源轨的电流。此外,它们与肖特基二极管电容一起形成低通滤波器,并将滚降电路带宽响应。对于需要更高带宽的ADC应用,这是一个问题,不利于ADC工作。

保护电路示例

使用外部肖特基二极管进行硬箝位

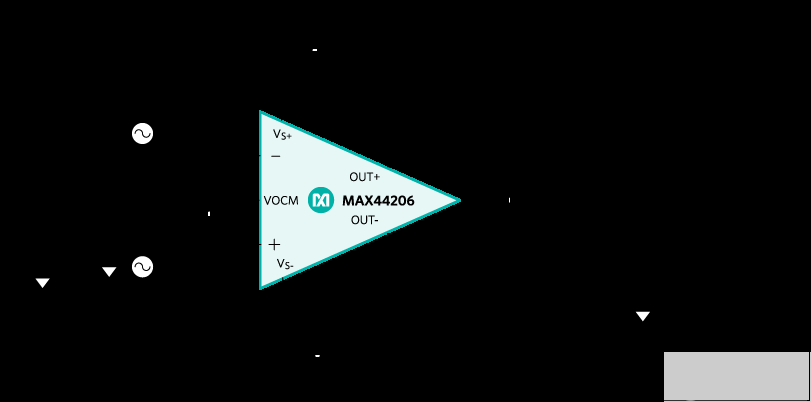

现在,我们将展示一个使用四个肖特基二极管(图2)的电路,该电路可保护ADC免受驱动器输出过压的影响。高性能16位至20位ADC需要一个低噪声、低失真驱动器,以保持输入信号的质量并保持ADC的整体转换精度。这里,一对7.5Ω电阻和一个1nF电容构成一个抗混叠滤波器,提供21.22MHz截止频率。为简洁起见,我们不讨论低通滤波器元件的尺寸,本应用笔记仅限于ADC过压保护。

图2.采用四个外部肖特基二极管箝位驱动器输出可保护ADC免受驱动器输出过压的影响。

图2所示为MAX44206运算放大器,配置为增益 = 1V/V差分放大器配置,采用±5V分离电源,VOCM = 1.65V。每个输出均经过直流电平转换至1.65V,即ADC的中轨,以利用ADC的0V至3.3V全转换范围。±5V 分离电源允许驱动器在整个 0V 至 3.3V 转换范围内提供输出电压摆幅。驱动器输入端使用的输入信号的幅度通常相等,异相180,以实现最大的差分输出信号摆幅。现在每个输出都直流电平转换到1.65V,每个输出将具有基于180相分离的输入的等幅信号摆幅。°°

在我们的实验中,我们执行了两个测试用例:

1. 每个输出的输出电压摆幅设置为3.3VP-P带 1.65V直流偏见

每个输入为 3.3VP-P具有180相分离;实际差分输入电压(V°英迪夫) 两路输入为 6.6VP-P.由于增益 = 1V/V,因此每个输出也是 3.3VP-P具有 180 相分离和 6.6V°P-P输出两端的差分电压(

图 3

)。

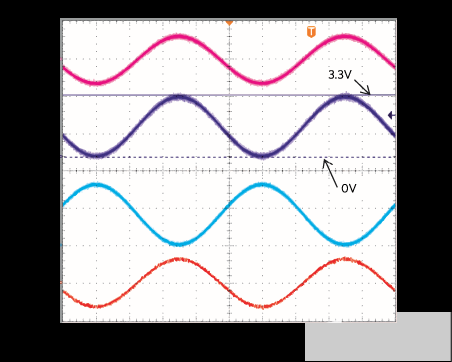

图3.图2电路的输出瞬态响应。这里 VIN+= 3.3VP-P和 VHNL= VIN+-180;VOCM =1.65V。°

图3示波器图显示,每个输出上尚未开始箝位动作,因为每个输出上的最大和最小电压分别为3.3V和0V,如V所示外曲线。可以理解的是,二极管尚未导通以保护ADC。

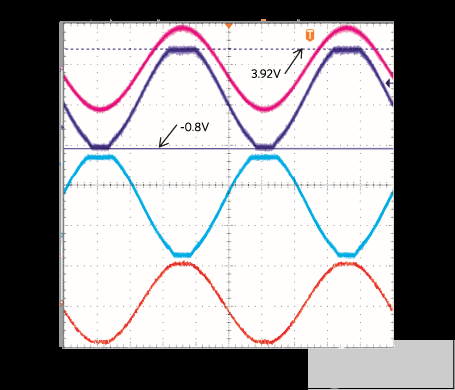

2. 每个输出端的输出电压摆幅设置为5VP-P带 1.65V直流偏见

每个输入为 5VP-P具有 a180 相分离(图 4)。实际差分输入电压(V°英迪夫) 两路输入为 10VP-P.由于增益 = 1V/V,每个输出应为 5VP-P同相分离180次;一个 10V°P-P预计输出两端的差分电压。5VP-P每个输出上具有 1.65VDC 偏置意味着输出摆幅在 4.15V 和 -0.85V 之间。实际上,只要每个输出超过3.3V加上二极管的正向压降,二极管就会导通,开始导通,并将驱动器输出箝位至3.92V。类似地,二极管将驱动器输出箝位至-0.8V。

图4.图2电路的输出瞬态响应,具有硬箝位功能。这里 VIN+= 5VP-P和 VHNL= 5VP-P;VHNL= VIN+-180°;V中氯= 3.3V;V中电= 0V;VOCM = 1.65V。

在图2设置中,肖特基二极管导通时,硬钳位状态下消耗的电源电流约为15mA。大多数ADC的输入电压的绝对最大额定值高于供电轨0.3V,低于供电轨0.3V。

硬箝位,无需外部分立二极管

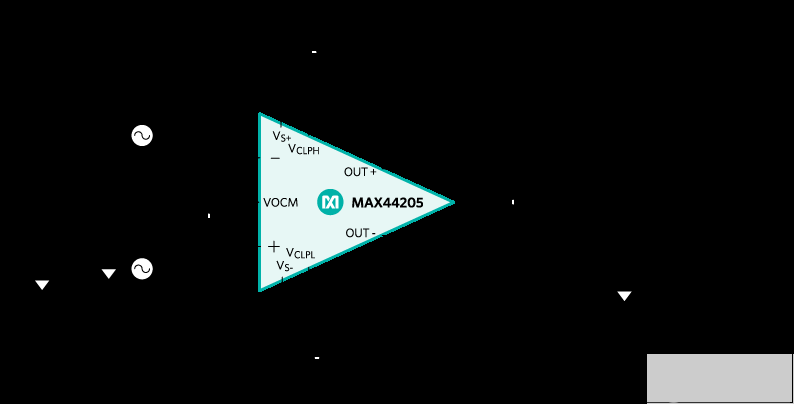

现在,我们将展示一个电路(图5),该电路无需外部二极管即可保护ADC免受驱动器输出过压的影响。该解决方案不仅节省了PCB空间,还节省了肖特基二极管的额外成本。图5与图2几乎相同,只是没有四个二极管。

图5所示的MAX44205运算放大器具有两个输出箝位引脚:V中氯和 V中电可用于将输出电压电平限制在预定电压。当ADC电源轨连接到这些箝位引脚时,驱动器输出被箝位在ADC电源轨内,与施加到驱动器的输入摆幅无关。

图5.在该电路中,驱动器输出被箝位,无需外部肖特基二极管或分立元件。

同样,我们执行了两个测试用例:

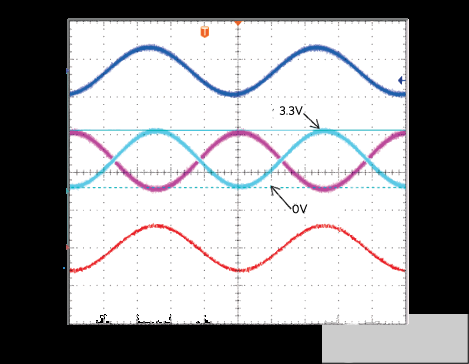

1. 每个输出的输出电压摆幅设置为3.3VP-P带 1.65V直流偏见

同样,每个输入为3.3VP-P具有 180 相分离(图 6)。由于增益 = 1V/V,因此每个输出也是 3.3V°P-P具有 180 相分离。在示波器图中(图6),驱动器的每个输出摆幅在3.3V至0V之间,与ADC电源轨完全相同,因此,到目前为止没有箝位动作。°

图6.图5电路的输出瞬态响应(带V)IN+= 3.3VP-P和 VHNL= 3.3VP-P;VS+= +5V;VS-= -5V;VHNL= VIN+-180;VOCM = 1.65V。°

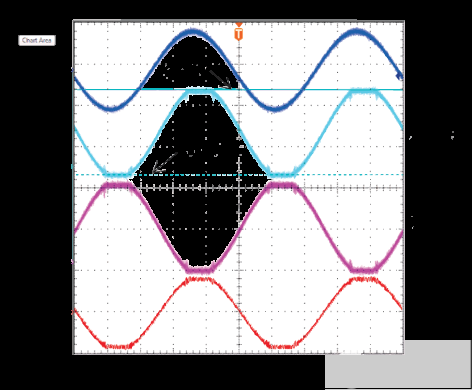

2. 每个输出端的输出电压摆幅设置为5VP-P带 1.65V直流偏见

每个输入为 5VP-P具有180相分离;实际差分输入电压(V°英迪夫) 在两个输入端为 10VP-P,如图 7 所示。由于增益 = 1V/V,每个输出应为 5VP-P具有 180 相分离。再次,5V°P-P理论上,每个输出上的1.65VDC偏置意味着输出摆幅在4.15V和-0.85V之间。MAX44205运算放大器在正摆幅上箝位输出和限值为3.72V,在负摆幅上将限值箝位至-0.4V,如V所示输出+跟踪(图7)。

图7.图5电路上硬箝位时的输出瞬态响应。这里 VIN+= 5VP-P和 VHNL= 5VP-P;VS+= +5V;VS-= -5V;VHNL= VIN+-180;VOCM = 1.65V。°

MAX44205运算放大器具有专有的箝位机制,在硬箝位状态下通过VCLPL仅消耗92μA电流。相比之下,使用图4中的分立设计进行箝位时,箝位为10毫安。MAX44205在箝位时的输出电压限值为V中氯+ 0.34 和 V中电- 0.42.不建议精确地箝位ADC的电源轨,因为驱动器输出需要摆动至任一ADC轨而不会失真。如果驱动器输出正好箝位在V中氯和 V中电,当输出位于ADC电源时,箝位可能会导通,从而导致失真。

审核编辑:郭婷

-

全差分运算放大器结构框图解析 常见的全差分运算放大器电路分析2023-09-25 17547

-

低噪声、精密运算放大器驱动高分辨率SAR ADC2023-01-03 3198

-

差分运算放大器板的资料分享2022-06-28 1360

-

低噪声、高精度运算放大器驱动高分辨率SAR/ADC2021-05-27 1018

-

LTC6362:精密、低功耗轨对轨输入/输出差分运算放大器/SAR ADC驱动器数据表2021-04-18 1025

-

运算放大器输出相位反转和输入过压保护2021-03-23 1129

-

MT-036:运算放大器输出相位反转和输入过压保护2021-03-21 1655

-

低噪声精密运算放大器驱动高分辨率 SAR ADC2021-01-21 1202

-

运算放大器输入过压保护:箝位与集成2019-10-13 3125

-

【模拟对话】运算放大器输入过压保护:箝位与集成2019-09-29 1628

-

基于LTC6363差分运算放大器/ADC驱动器的DC2319A-A2019-05-17 3440

-

运算放大器输出相位反转和输入过压保护PDF2018-11-05 1924

-

驱动高分辨率 SAR ADC2018-06-07 5421

-

高性能运算放大器与ADC的接口设计2009-09-25 751

全部0条评论

快来发表一下你的评论吧 !