浅谈DRAM制造工艺及微缩挑战

存储技术

描述

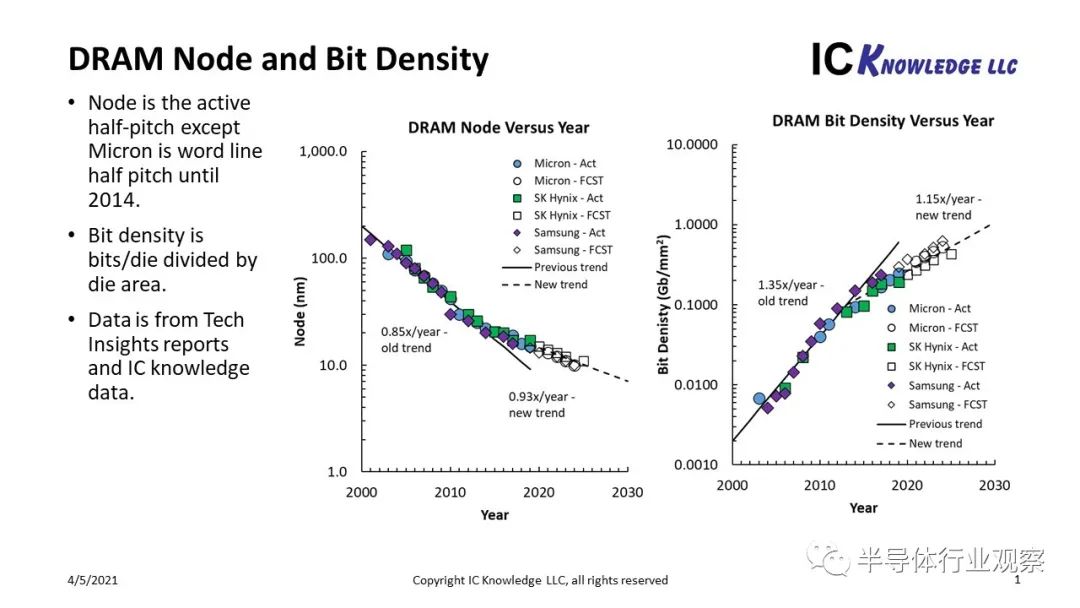

在2021年2月举行的SPIE高级光刻会议上,应用材料的Regina发表了一个题为:“Module-Level Material Engineering for Continued DRAM Scaling”的演讲。在演讲中,Regina强调DRAM的微缩正在放缓,需要新的解决方案来继续提高密度,见图1。

图1. DRAM节点和位密度趋势。

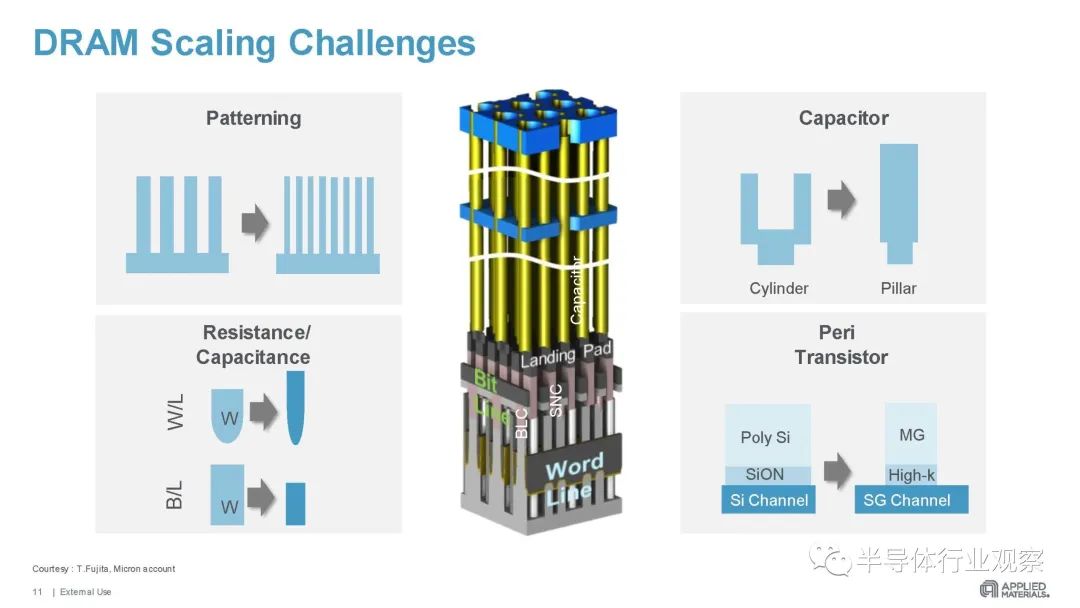

按照他们介绍,DRAM的微缩迎来了多个方面挑战:

图案化-如何创建越来越密集的图案。

电容器–从圆柱体演变为柱状结构,需要对高深宽比进行构图。

电阻/电容–位线和字线需要提高电阻/电容才能提高访问速度。

外围(Peri)晶体管–从含氧化硅的多晶硅栅到高K金属栅(HKMG)的演变。

图2. DRAM扩展挑战。

本文将重点讨论图案化和电容器。

电容器图案化最近已经通过交叉自对准双图案化( cross self-aligned double patterning:XSADP)完成,但现在正在发展为甚至更复杂的交叉自对准四重图案化( (XSADP) but is now evolving to even more complex :XSAQP)。如三星所公开的,另一种选择是间隔物辅助的图案化,该图案化可以使掩模上的孔密度增加3倍,但需要使孔尺寸相等的蚀刻。最近,EUV已开始被应用到DRAM的生产中。

作者指出,三星正在将EUV用于1z DRAM上,并且预计现在将EUV用于多层的1α DRAM上,SK Hynix也有望在今年推出其使用EUV***的1α DRAM。

然而,为DRAM实施EUV面临以下几个挑战:

局部临界尺寸均匀性(Local Critical Dimension Uniformity:LCDU),这种变化会改变电气性能和蚀刻纵横比。

孔尺寸– EUV对孔尺寸敏感,并且加工窗口狭窄。

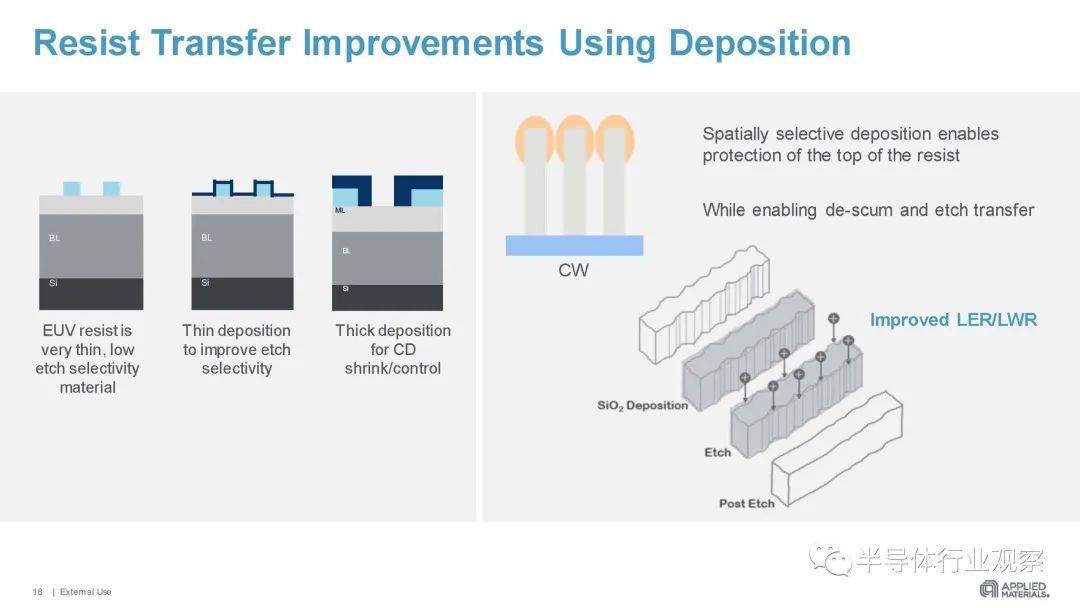

薄抗蚀剂– EUV抗蚀剂非常薄,需要硬化。

薄沉积的使用可以使抗蚀剂硬化,厚沉积的使用可以缩小临界尺寸(Critical Dimensions:CD)。在图案顶部的空间选择性沉积可以改善线边缘粗糙度(Line Edge Roughness:LER)/线宽粗糙度(Line Width Roughness :LWR),这是EUV图案形成中的显着缺点。参见图3。

图3.使用沉积的光致抗蚀剂改进。

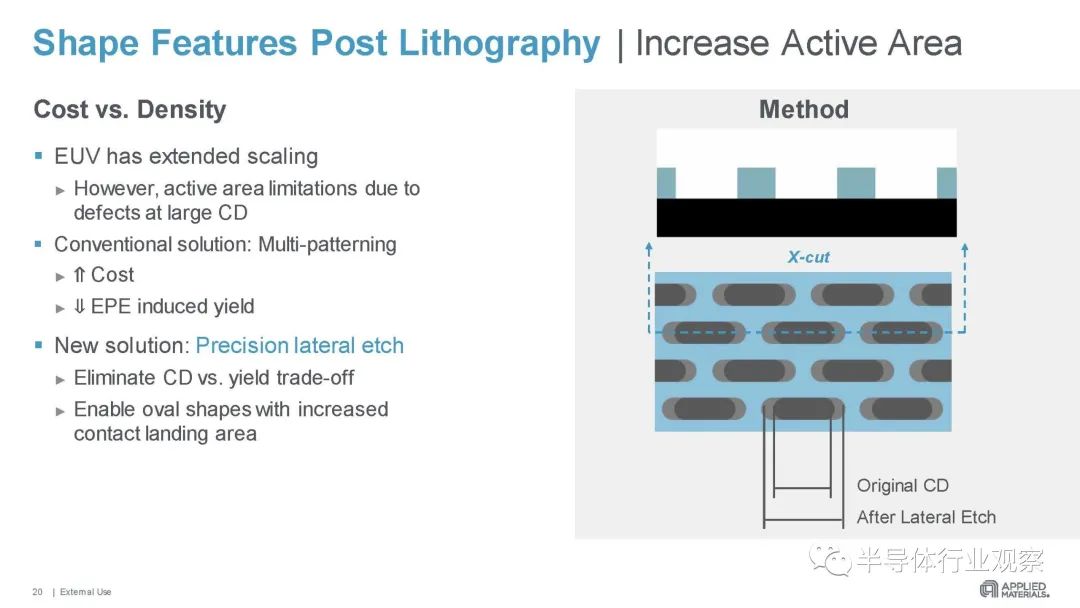

对于有源区域缩放,EUV在大CD上存在缺陷问题,相反,您可以蚀刻小孔,然后使用精确的横向蚀刻在一个方向上打开特征,从而缩小针尖到针尖的距离。该技术消除了CD与产量之间的折衷,并使ovals 具有更大的接触焊盘面积,见图4。

图4.用于有源图案的精密横向蚀刻。

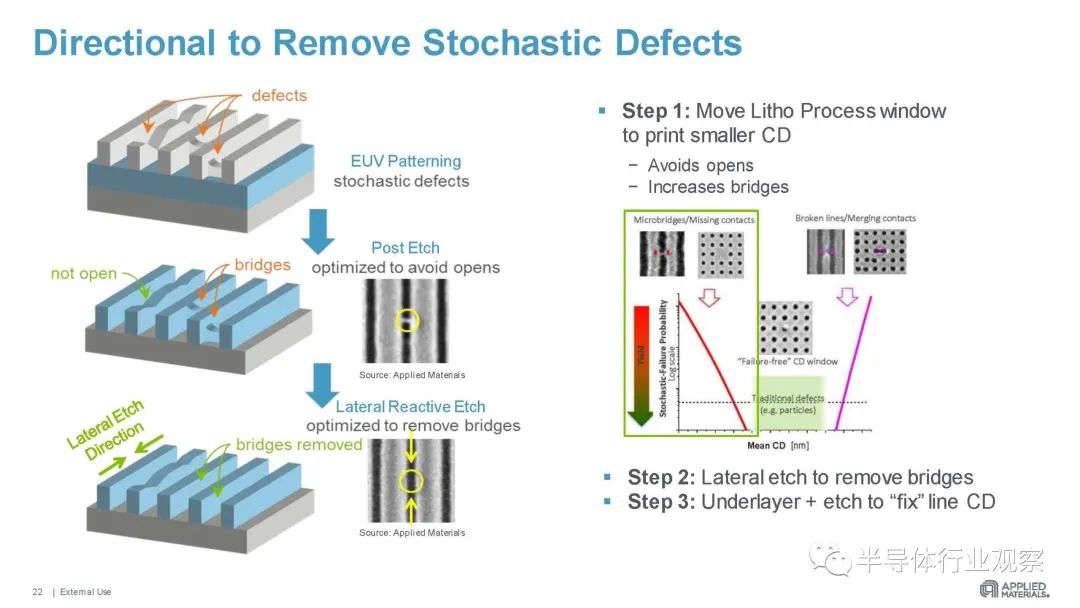

EUV的一个主要问题是狭窄的工艺窗口,可以接受可接受的随机缺陷。定向蚀刻为过程设计提供了一个额外的knobs,如果过程窗口的中间已打开并桥接,则可以向具有桥接的窗口一侧移动,然后使用定向蚀刻移除桥接,请参见图5。

图5.定向蚀刻以消除随机缺陷。

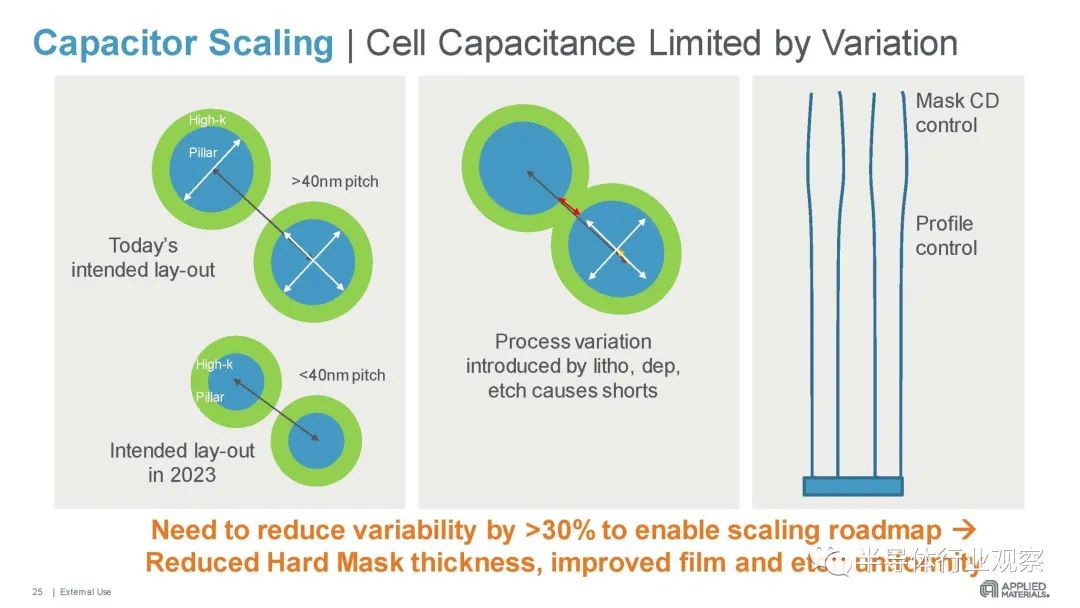

当今的电容器间距极限大于40nm,这也是当前电容器图案化的EUV极限。将来将需要更小的间距,并且工艺可变性需要提高30%以上,才能实现缩放,请参见图6。

图6.电容器缩放受变化的限制。

减少硬掩模厚度和提高蚀刻均匀性都是实现这一目标所必需的。

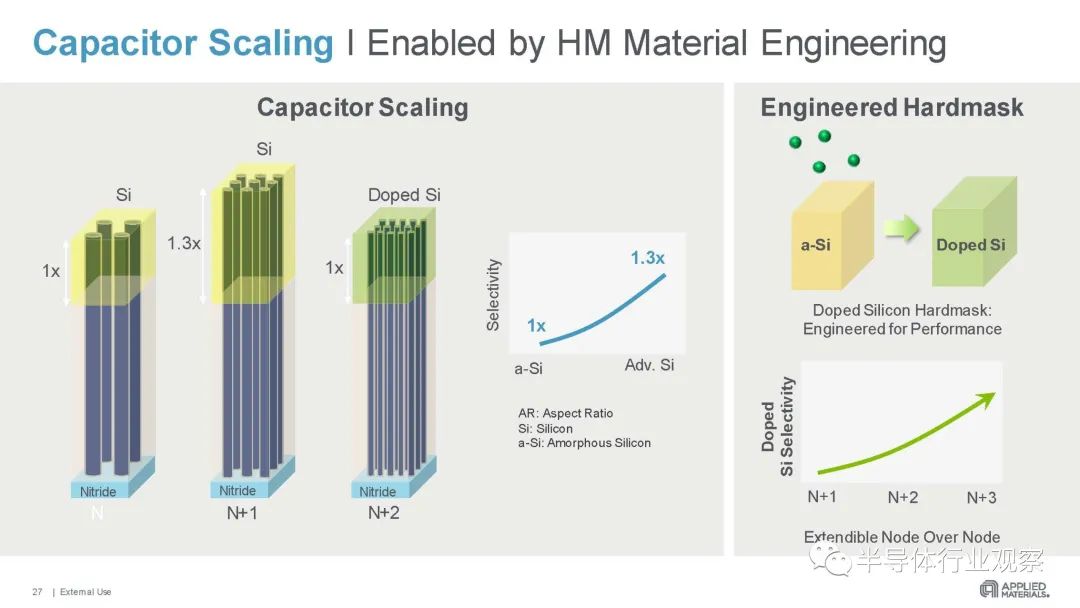

如今,非晶硅(a-Si)被用作硬掩模,将来掺杂的硅可以提供更好的选择性,从而可以实现更薄的硬掩模,但会产生难以去除的副产物,见图7。

图7.用于电容器缩放的改进硬掩模。

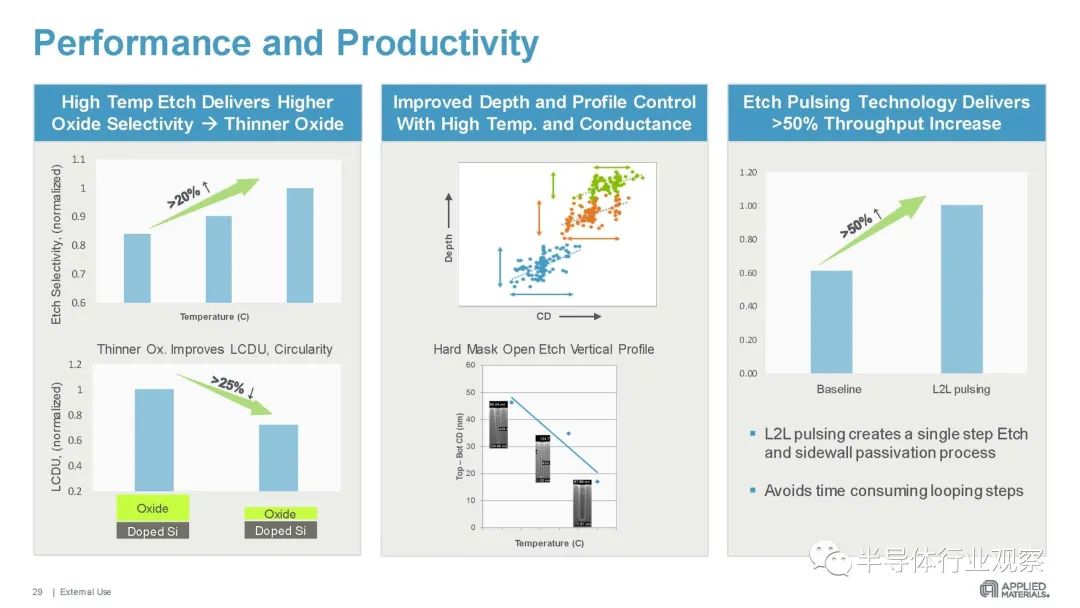

用于硬掩模的掺杂硅的问题在于它需要特殊的蚀刻,下一代工艺使用高温蚀刻。光刻胶用于对氧化物硬掩模进行图案化;然后在高温蚀刻机中使用氧化物硬掩模对掺杂的多晶硅硬掩模进行图案化,最后将掺杂的多晶硅硬掩模用于蚀刻电容器。蚀刻和沉积步骤之间的逐级脉冲蚀刻切换允许对电容器的高速蚀刻进行激进的化学使用,请参见图8。

图8.改进的性能和生产率。

期望上述工艺创新能够实现当前DRAM体系结构的持续微缩。

但从演讲中我们看到,在3至5年后,我们将需要一种新的DRAM架构。当中涉及的一个有趣的选择是3D化,将电容器从垂直结构变为堆叠的水平结构。

编辑:黄飞

-

DRAM扩展挑战越来越大2019-11-25 7234

-

3D闪存的制造工艺与挑战2025-04-08 2805

-

表面安装pcb设计工艺浅谈2012-08-20 2837

-

三星宣布:DRAM工艺可达10nm2015-12-14 3195

-

无新产能导致淡季变旺,DRAM合约价再飙涨到Q3【硬之城电子元器件】2017-06-13 3125

-

如何缓解GDDR6 DRAM实施所带来的挑战2021-01-01 2217

-

绿色制造带来多种挑战 破解工艺成本难题2009-11-12 1445

-

三星加速制程微缩 DRAM进入40纳米世代2009-11-18 685

-

半导体产业面临挑战 晶片微缩脚步渐缓2012-03-23 1068

-

DRAM和NAND技术的发展和面临的挑战2020-07-22 2511

-

HKMG工艺在DRAM上的应用2022-11-17 4032

-

动态随机存储器集成工艺(DRAM)详解2023-02-08 13157

-

使用虚拟制造评估先进DRAM电容器图形化的工艺窗口2023-11-16 1345

-

以工艺窗口建模探索路径:使用虚拟制造评估先进DRAM电容器图形化的工艺窗口2023-11-23 1468

-

应对传统摩尔定律微缩挑战需要芯片布线和集成的新方法2023-12-05 1333

全部0条评论

快来发表一下你的评论吧 !