浅析FPGA架构及相关的基本概念

电子说

描述

01

FPGA基础知识

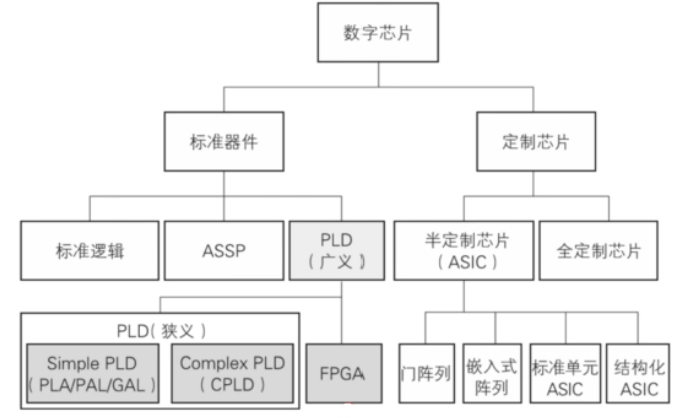

FPGA(Field Programmable Gate Array, 现场可编程逻辑阵列) 是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

1.1 FPGA与其他相关可编程器件

1.1.1****FPGA, ASIC和ASSP

ASIC以及ASSP的功能相对固定,是为了专一功能或专一领域而生,希望对它进行任何功能和性能的改善往往是无济于事,而FPGA则在产品发布后仍然可以对产品设计做出修改,大大方便了产品的更新和针对新的协议标准做出相应改进,从而加速产品上市时间,并降低产品失败的风险和维护成本。随着电子技术领域的发展,FPGA也正在向高集成,高性能,低功耗和低价格方向发展,并逐渐具备了与ASIC,ASSP相当的性能。

ASIC: 专用集成电路(Application Specific Integrated Circuit)

ASSP: 专用标准产品(Application Specific Standard Parts)

**1.1.2 **FPGA, ARM和DSP

在嵌入式系统设计领域,虽然ARM有很多外设,DSP具备强大的信号运算能力,但是这些功能FPGA都可以做到,所以在很多原型产品设计过程中(灵活性要求高、定制化程度高、性能要求高),会经常提出基于FPGA的方案,但是客观来说,FPGA的成本功耗和开发复杂性往往会让很多用户望而却步。

ARM: Advanced RISC Machines,ARM通常包含一颗强大的处理器内核,并且为这颗处理器量身配套了很多成熟的软件工具以及高级编程语言,同时在ARM内核处理器周边,各种各样精于控制的外设很多,如GPIO,PWM,AD/DA,UART,SPI,I2C等,使得ARM在控制和管理上有很大优势。

DSP: Digital Signal Processor, 即数字信号处理器,是一种独特的微处理器,有自己完整的指令系统,能够进行高速高吞吐量的数字信号处理,因此适合对各种语音,数据和视频做运算处理。

**1.1.3 **FPGA和PLD

PLD重构基于门级阵列(Gate Array),属于门级,即逻辑门是固定的,只有布线是可重构编程的,因此布线冗余较多;而FPGA重构基于查找表(LUT),属于逻辑簇级,即布线是固定的,而逻辑是可重构编程的,因此相对与PLD而言布线冗余较少,更适合构建大规模逻辑电路。

1.2 FPGA主流开发语言

**1.2.1 **VHDL

VHDL(VHSIC hardware description language)语言诞生于1983年,1987年被美国国防部和IEEE确定为标准的硬件描述语言。自从IEEE发布了VHDL的第一个标准版本IEEE 1076-1987后,各大EDA公司都先后推出了自己支援 VHDL 的 EDA 工具。VHDL 在电子设计行业得到了广泛的认同。此后IEEE又先后发布了IEEE 1076-1993和IEEE 1076-2000版本。

VHDL优点:语法严谨,层次结构清晰。

VHDL缺点:不够灵活,熟悉时间长。

**1.2.2 **Verilog HDL

Verilog HDL诞生于1983年,由Gateway设计自动化公司的工程师创立,菲尔·莫比(PhilMoorby)完成了Verilog的主要设计工作。1990年代初,开放Verilog国际(Open Verilog International, OVI)组织(即现在的Accellera)成立,Verilog面向公有领域开放。

1992年该组织寻求将Verilog纳入电气电子工程师学会标准 ,于是Verilog最终成为了电气电子工程师学会1364-1995标准(即Verilog-95)。后来Verilog经过多次版本更新,具备了一些新的实用功能,目前,Verilog-2001是Verilog的最主流版本,被大多数商业电子设计自动化软件包支持。2009年IEEE 1364-2005和IEEE 1800-2005两个部分合并为IEEE 1800-2009,成为了一个新的、统一的SystemVerilog硬件描述验证语言(hardware description and verification language, HDVL)。

Verilog 优点:类C语言,上手快速,易于使用。

Verilog 缺点:存在不能通过编译识别的错误。

1.3 FPGA器件主流企业

目前Altera(已被Intel公司收购)和Xilinx公司(已被AMD收购)是FPGA器件主流厂商,两家公司的可编程逻辑器件占到全球市场的近80%,其中Xilinx FPGA占近50%,而Altera占近30%。除这两家龙头企业外,偶尔也会有一些后来者,例如Lattice,京微雅格等。尽管不同公司的FPGA器件内部结构有所差异,但在开发流程、开发工具乃至原厂提供的各种支持上都大同小异,因此只要掌握FPGA的开发流程,任何厂商的器件都可以轻松上手。

02

FPGA基本架构

2.1 Xilinx FPGA基本架构

Xilinx的FPGA主要由可配置逻辑块(CLB)、时钟管理模块(CMT)、存储器(RAM/FIFO)、数字信号处理模块(DSP)和一些专用模块组成。

**2.1.1 **可配置逻辑块(CLB)

Xilinx FPGA逻辑是由阵列排布的CLB实现的,每一个CLB单元都和一个开关阵列相连,并受其控制从而实现逻辑功能。

CLB由基本结构Slice构成,而基本结构中又包含有查找表(LUT),存储单元,广函数多路器(Wide function Multiplexer)和进位逻辑,这种基本结构成为SLICEL。有些基本结构中还包含舒勇RAM存储数据的功能和使用32位寄存器移位功能,这种基本结构成为SLICEM。

2.1.2 时钟管理模块(CMT)

时钟管理模块(CMT)用于产生高质量的时钟,通常CMT会包含数字时钟管理模块(DCM)和锁相环电路(PLL),从而实现时钟的倍频与分频。

2.1.3 存储器(RAM/FIFO)

Xilinx FPGA都有内部的存储器块,例如Virtex-5内部包含若干块36KB大小可以灵活配置的同步双口RAM,这些RAM可以配置为多速率的FIFO存储器,极大地提高了设计的灵活性。

2.1.4 数字信号处理模块(DSP)

Xilinx FPGA中大多包含DSP资源模块,对于需要大量算法运算的应用,FPGA内部这类乘法运算单元就显得十分实用。例如7系列中最小的计算单元DSP48E1:

2.1.5 其他专用模块

除了上述模块外,在现代的Xilinx的FPGA产品中还有一些其他专用模块,例如:Rocket IO千兆位级收发器、PCI Express端点模块和三态以太网MAC模块等。

2.2 Altera FPGA基本架构

Altera的FPGA一般由逻辑阵列模块(LAB)、TriMatrix存储器模块(RAM)、数字信号处理模块(DSP)和锁相环模块(PLL)组成。

2.2.1 逻辑阵列模块(LAB)

逻辑阵列模块(LAB)的主要结构是适应逻辑模块(ALM),还包括一些进位链和控制逻辑等结构。

ALM中包含查找表(LUT),可编程寄存器,专用全加器,进位链,共享算术链和寄存器链。

**2.2.2 **FPGA, ARM和DSP

类似于Xilinx FPGA器件,Altera FPGA中同样包括不同大小的嵌入式RAM存储器资源,可以支持配置各种特性。

2.2.3 数字信号处理模块(DSP)

类似于Xilinx FPGA器件,Altera FPGA中同样含有DSP资源,从而实现多种最大性能和最小逻辑资源利用率的DSP功能。

2.2.4 锁相环(PLL)

类似于Xilinx FPGA器件内部的时钟管理模块,Altera FPGA中同样具备PLL锁相环资源,从而实现高质量的时钟生成。

2.3 LUT实现原理

PLD重构基于门级阵列(Gate Array),属于门级,即逻辑门是固定的,只有布线是可重构编程的,因此布线冗余较多;而FPGA重构基于查找表(LUT),属于逻辑簇级,即布线是固定的,而逻辑是可重构编程的,因此相对与PLD而言布线冗余较少,更适合构建大规模逻辑电路。

A,B,C有FPGA芯片的管脚输入后进入可编程连线,然后作为地址线连接到LUT,LUT中已经事先写入了所有可能的逻辑结果,通过地址查找到相应的数据后输出,从而实现组合逻辑,而FPGA中的时序逻辑由触发器协助实现。

03

FPGA应用领域与优势

3.1 信号采集处理

FPGA的并行处理特性在信号采集与处理方面具有很大的优势,例如一些高速ADC或图像传感器的数据采集与实时处理。尽管一些高端的嵌入式处理器也可实现信号采集与处理功能,但嵌入式软件程序的编译需要耗费更多的时间,在实时性要求较高的数据采集处理系统中将难以胜任。相比之下,FPGA的并行处理和可灵活配置的位宽等诸多优势得以显现。

3.2 通信协议实现

FPGA在通信协议的实现上具有更高的灵活性。尽管ARM等嵌入式芯片也可通过一定的协议进行数据交互,但这些通信协议接口大多是固定的,功能也相对有限。FPGA拥有更加丰富的电平接口,易于实现各种各样不同的协议,更适合于用户定制化较高的场景。同时相比于定制化芯片的设计生产,FPGA在成本和周期等各方面都具有一定的优势。

3.3 芯片原型验证

随着芯片制造工艺的提升,以及芯片复杂程度的增加,流片的成本也在不断攀升。利用FPGA在流片前期进行验证,可以极大的降低流片后芯片出现问题故障的概率,进一步节约芯片制造的成本。

3.4 系统实时控制

FPGA的并行特性在需要实时控制的系统中也发挥着很大的作用。尽管利用单片机可以实现对电机、显示器等不同执行终端的控制,但是单片机程序所需要的响应时间较长。在实时性要求很高的系统中,单片机的响应时间可能会导致系统无法达到需求标准,例如航天图像系统需要对航天器的工作情况进行实时监控与评估,FPGA便是很好的选择。

04

FPGA开发流程

4.1 需求分析—>模块划分

设计者根据项目需求,确定所需资源并选定FPGA型号,进而根据目标实现功能进行模块划分。由于FPGA的实现是并行的,对于一个项目的需求往往需要通过多次处理才能实现,因此要考虑分成多个模块以利于后期的代码升级,维护以及设计的综合优化。

4.2 设计输入—>综合优化

模块划分完成后,需要考虑不同模块的输入输出接口,此时根据原理图和相关硬件手册,进行底层设计输入工作。代码设计完成后,检查语法是否无误,进而进行代码的综合。

综合是将较高层次的电路描述转化为较低层次的电路描述,即将设计代码转化为底层的与门,非门,RAM,触发器等基本逻辑单元相互连接而成的网表。

综合完成后需要进行功能仿真。功能仿真不涉及任何时序上的延时,只是单纯验证代码所实现的功能是否符合要求。

4.3 实现—>时序收敛

功能仿真过后一般会进行一次全编译,然后对工程进行约束:包括全局约束(I/O接口约束)和时序约束。添加完时序约束后,需要进行实现(翻译、映射和布局布线),然后查看时序报告。在添加时序约束前后,变化最大的应该是布局布线。

一般对于较大的工程,编译往往耗费很多时间,因此可以查看映射后的时序报告进行前期的分析。这个报告的逻辑延时是完全准确的,布线延时却是通过一定比例推导得出的估计值,所以由此得到的时序报告并不完全准确。但是如果得到的估计延时偏大,时序明显达不到要求,那么设计者就应该先回头查找问题,想办法达到时序收敛。如果达到了时序收敛,并且设计者进行了充分的前期功能仿真,那么往下的时序仿真就可以不做,从而节省了时间。

4.4 仿真测试—>板级调试

仿真和板级调试是FPGA设计的主要验证手段。尽管板级调试能够直观真实的反映信号状态,也便于问题的寻找和定位,但是板级调试同步观察接口信号数量受限,而且很难观测到FPGA内部信号节点的状态。因此,仿真在FPGA开发验证中有着更重要的作用。

整个设计的验证过程如上图所示:

- 行为仿真的代码可以是不可综合的代码;

- 功能仿真是对成为硬件的门级网表进行验证,但不包含任何布局布线延时信息;

- 时序仿真是在功能仿真的基础上包含电路的延时信息;

- 板级调试验证最终功能是否实现。

前仿真:综合前仿真,行为仿真

审核编辑 黄昊宇

-

FPGA架构及相关基本概念2023-01-04 1543

-

Proteus涉及的基本概念2012-08-01 3040

-

Fpga Cpld的基本概念2012-08-20 2977

-

天线分集技术的基本概念介绍2019-07-02 2638

-

阻抗控制相关的基本概念2021-02-25 2276

-

FPGA功耗的基本概念,如何降低FPGA功耗?2021-04-30 1392

-

AGV的基本概念及基本结构组成2021-09-14 3026

-

单片机中断的基本概念2021-11-25 1112

-

STM32的中断系统基本概念2022-01-07 1307

-

ARM的体系架构基本概念2022-01-25 1421

-

PCIE基本概念与拓扑架构图2022-02-16 2796

-

FPGA高级班前言基本原理基本概念2010-02-09 534

-

FPGA学习教程之硬件设计基本概念2020-12-25 1366

-

FPGA设计中时序分析的基本概念2022-03-18 4483

-

MMU相关的基本概念2023-11-26 1534

全部0条评论

快来发表一下你的评论吧 !