莱迪思Avant平台:专为中端FPGA市场量身打造

描述

引言

几十年来,FPGA产品一直是设计工程师所熟知且经常使用的电子硬件。FPGA通常使用逻辑单元 (LC)来区分逻辑密度。可以根据逻辑单元的数量将FPGA市场可以分为三类:高端、中端和小型FPGA。尽管这些描述会随时间发生变化,但目前高端FPGA的逻辑单元普遍在500K以上,中端为100K至500K,小型FPGA则少于100K。

从架构的角度来看,许多FPGA供应商长期以来都未将中端FPGA领域视为战略重点,令人惊讶不已。中端FPGA已成为各类嵌入式、工业、自动化和机器人等应用的最佳选择。可以说,市场上已经将近十年没有出现过一款真正的中端FPGA了。

供应商意识到市场对中端FPGA的需求后,经常使用“瀑布式”开发来提供这些产品。基本上就是将针对高端FPGA优化的架构应用于中端 FPGA。虽然这些产品确实能填补中端产品的空白,但并未针对中端FPGA进行特别的优化。因为这些架构本应支持高达10倍的逻辑密度。这种策略可能对FPGA供应商有利,但对于中端FPGA客户来说,就另当别论了。

满足各类需求

客户真正需要的是专为中端市场而设计的中端FPGA,而不是对高端或小型FPGA架构进行一些调整。莱迪思Avant平台专为中端FPGA设计。与中端FPGA市场上的现有FPGA相比,Avant平台具有以下优势:

功耗远低于同类竞品器件

封装尺寸远小于同类竞品器件

DSP性能更高且支持最新AI算法的需求

25Gbps SERDES

支持DDR3L/DDR4/LPDDR4和DDR5

下一代安全性能

可靠性更高

莱迪思半导体长期以来专注于低功耗FPGA,服务于低密度FPGA市场。事实上,莱迪思的出货量是所有其他传统FPGA供应商的总和。如今该公司正凭借Avant平台强势打入中端FPGA市场。通过Avant平台,设计人员除了可以一如既往地获得莱迪思提供的低功耗、密度优化等特性外,还能获得更高的器件密度和性能。因此该系列器件可以提供更多高端功能,但同时具有中端(和小型)器件的尺寸和低功耗。

Avant FPGA平台的潜在应用十分广泛。在工业领域,它可以用于网络控制器、PLC、网络边缘计算、机器视觉和工业机器人。得益于其强大的DSP性能,它在汽车网络和软件定义无线电领域也很有价值。此外,通用无线通信、室内5G小基站和5G前传应用也是Avant的潜在应用领域。

Avant实现了一系列高带宽I/O标准,如PCIe Gen4、LPDDR4和DDR5,并提供强大的DSP和负载加速性能。Avant FPGA架构支持的时钟速率高达350 MHz,嵌入式RAM模块和DSP乘法/累加模块支持的时钟速率达625 MHz。这些器件是行业中提供25 Gbps SERDES功能的尺寸最小的FPGA。

充分保障安全

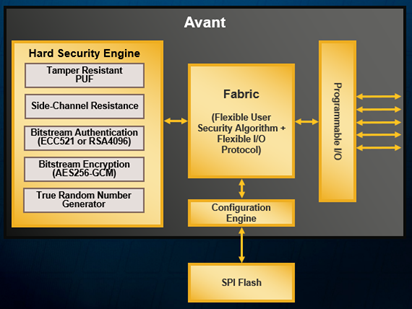

所有嵌入式设计的安全性应当是首要考虑因素。为此,莱迪思工程师确保Avant平台包含各类安全功能,如AES256-GCM、ECC、RSA、防篡改和物理不可克隆功能(PUF)。这些功能能够加密和验证配置和用户数据,从而确保FPGA即便受到恶意攻击也能安全无虞。软失效检测和纠正可快速检测导致软失效的环境因素,便于执行适当的操作。

身份验证和加密可以保护FPGA的配置位流。用户模式的安全功能则通过硬核加密引擎实现,这些引擎可作为FPGA架构中的嵌入式IP模块使用。针对侧信道和故障注入攻击的防篡改功能则通过密钥和敏感数据的归零来实现。

除了强大的安全性能外,Avant器件还能够抵御α粒子引起的瞬态软失效故障。单粒子翻转的检测和恢复需要快速进行,从而保障系统正常运行,增强可靠性。

最小化功耗

Avant平台降低功耗的一种策略是逻辑实现使用的是一个四输入LUT,而不是六输入LUT。四输入LUT只需要16个SRAM配置位来对LUT进行编程,而六输入LUT需要64个SRAM配置位。

功耗优化的另一个方面是减少高电容网络。较高的扇出网络会通过连接到高电容金属布线的高驱动强度缓冲器产生更大的电容。Avant架构则利用小型多路复用器和低扇出网络来降低功耗。还值得注意的是,Avant器件采用16纳米FinFET工艺制造,经过优化极大降低了漏电流。

丰富的架构

充足的DSP模块对于中端FPGA中的各种信号处理和AI功能至关重要。Avant器件提供多达1800个18 x 18乘法器,能够以625 MHz 的频率全流水线运行。该DSP模块还可以作为三个9 x 9或四个8 x 8乘法器,内置一个18位预加器和48位累加器。这些配置模式大大优于传统器件。此外,乘法器可以级联为27 x 18、36 x 18、27 x 27或36 x 36的配置。

I/O灵活性是Avant架构的基石。FPGA提供SERDES和并行I/O标准,可满足各种应用的需求。就SERDES标准而言,包括了PCIe Gen 4、25G以太网、DP/eDP、SLVS-EC、CoaXPress、JESD204B/C、eCPRI/CPRI、RoE和SyncE。此外,为了加速PCIe的实现,还提供了一个硬核PCIe控制器。GPIO支持多种接口,包括LVCMOS 0.9-3.3V、1.8 Gbps MIPI D-PHY、1.6 Gbps LVDS/subLVDS、I3C、SGMII和LVDS 7:1。

内部嵌入式存储器采用36 kbit存储块,支持单端口、伪双端口(1R1W)、真双端口(2RW)和ROM配置。莱迪思Radiant软件存储器编译器可以汇编和布局/布线最大64 kbit×256位(总共16 Mbit)的内部存储器块。存储器提供最高36 Mbit容量。

外部存储器接口包括DDR4、DDR5和LPDDR4(运行速度达2.4 Gbit/s)以及传统标准的DDR3L(1.866 Gbit/s)和LPDDR2(1.066Gbit/s)。这些实现都基于带有灵活软控制器的硬核MEMPHY。软核存储器控制器支持错误纠正码(ECC)。

小尺寸低功耗封装

从封装角度看,莱迪思设计团队的目标是以更低成本的封装提供更小的芯片,他们也做到了这一点。这一目标的实现得益于更低功耗的要求,从而使用更小的裸片和更低成本的封装,200K逻辑单元的芯片尺寸小至11x9 mm,500K逻辑单元的芯片尺寸小至15x13 mm。

莱迪思Radiant和莱迪思Propel工具功能强大且直观易用,用户可以使用便捷的设计向导和精确的实现高效地开发FPGA应用。这包括了编译器优化和分析,实现快速且可预测的设计收敛。可以通过统一的设计数据库、设计约束流程和全流程的时序分析实现这一目标。

Avant提供了一整套IP来支持该平台。有些是硬核(定制逻辑)配置,用于优化面积和性能,另一些则以软核形式提供(通过使用逻辑单元),实现最大的灵活性。PCIe就是硬核IP的一个例子,而外部存储器接口则使用MEMPHY和软控制器实现了部分硬化。此外,如果不使用软核,则不会占用任何空间。

专为中端FPGA设计

Avant平台设计初衷就是服务于中端FPGA市场。莱迪思在这一领域的投入让该平台具备了领先的强大功能、小尺寸和高性能。该平台现代化的功能集支持使用最新的接口标准进行互连,进一步增强了其领先地位。目前莱迪思Radiant和Propel设计工具已经支持Avant平台,便于莱迪思客户快速应用已有的软件知识。各类IP和开发板也已支持该平台。了解更多信息,请前往莱迪思Avant网站页面。

审核编辑:汤梓红

-

莱迪思Avant FPGA平台荣获2024年SEAL奖2024-05-13 988

-

莱迪思Avant™ FPGA平台荣获2024年环境和能源领导力奖2024-04-30 928

-

莱迪思在硬件产品层面推出了“Nexus+Avant”2024-04-10 1398

-

富昌电子为莱迪思新FPGA平台Lattice Avant™提供工程支持2023-03-20 2221

-

莱迪思推出全新低功耗中端Avant FPGA平台2023-01-04 824

-

莱迪思Avant-E FPGA器件为网络边缘处理而生2022-12-30 766

-

莱迪思正式进军中端FPGA,意欲又一个30亿美元的FPGA市场2022-12-12 3164

-

莱迪思推出全新Avant FPGA平台,进一步增强在低功耗FPGA领域的领先地位2022-12-07 598

-

基于莱迪思Nexus平台构建助力未来高性能数据中心发展2022-10-28 1449

-

莱迪思力推CertusPro-NX汽车级FPGA2022-09-15 862

-

基于莱迪思Nexus FPGA技术平台产品的主要特性分析2019-12-12 2862

-

Ximmerse VR/AR跟踪平台采用莱迪思的低功耗、小尺寸ECP5 FPGA2017-09-27 5926

-

莱迪思荣获中国"最具创新的FPGA移动电子平台"奖2012-09-10 1215

-

莱迪斯中端LatticeECP4 FPGA上市2011-12-14 1665

全部0条评论

快来发表一下你的评论吧 !