PCIe收发卡设计资料原理图:611-基于VU9P的2路4Gsps AD 2路5G DA PCIe收发卡

今日头条

描述

基于VU9P的2路4Gsps AD 2路5G DA PCIe收发卡

一、板卡概述

基于XCVU9P的5Gsps AD DA收发PCIe板卡。该板卡要求符合PCIe 3.0标准,包含一片XCVU9P-2FLGA2014I、2组64-bit/8GB DDR4、2路高速AD, 2路高速DA,支持外触发,外时钟。板卡工作温度范围0到60℃,板卡设计加工包含散热装置,支持服务器风冷散热。软件包括接口测试软件,支持甲方应用开发。

二、硬件组成

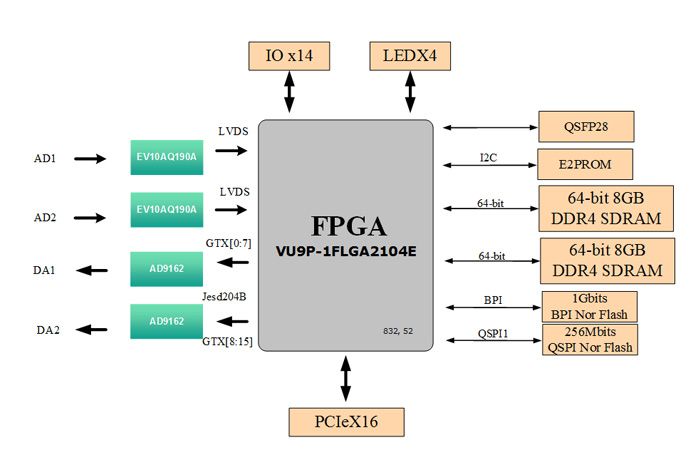

2.1 板卡逻硬件图如图所示:

2.2功能指标

板卡功能

参数

内容

ADC

芯片型号

EV10AQ190A

路数

2路ADC,

采样率

5Gsps(实际工作是4Gsps)

数据位

10bit

数字接口

DDR LVDS

模拟接口

交流耦合

模拟输入

-250mV~250mV

连接器

2路 SSMC(推荐型号:SSMC-JYWHD)

输入阻抗

50Ω

模拟指标

DAC

芯片型号

AD9162

路数

2路DAC

采样率

5Gsps(实际工作是5Gsps)

数据位

16bit

数字接口

JESD204B

模拟接口

交流耦合

模拟输出

-200mV~200mV

连接器

2路 SSMC(推荐型号:SSMC-JYWHD)

输出阻抗

50Ω

模拟指标

时钟1

PLL芯片

AD9516-1

板载晶振

10MHz 温补晶振VCXO

外输入时钟

默认10MHz,3.3V LVTTL电平,SSMC接口

时钟2

PLL芯片

HMC7044

板载晶振

100MHz VCXO

外输入时钟

SSMC接口

触发

路数

1路外输入,SSMC接口。

电平

3.3V LVTTL电平

FPGA

型号

XCVU9P-2FLGA2014I

外部缓存

板载两组64-bit DDR4,每组总容量支持4GB,可稳定工作于1200MHz(2400MT/s)。

加载方式

一片BPI Flash 用于程序配置 ,1片SPI x4 NorFlash,可用于参数存储。

PCIe

V3.0 PCIeX8; 2GB/s 采集

数字接口

光纤

支持1路QSFP28光纤接口,最高支持4X 25Gbps,可用于100G以太网开发应用。

外部IO

一路单端转差分输入,SSMC接口

一路差分转单端输出,SSMC接口

GPIO

14个GPIO备份使用,四个LED指示灯,四个用户按键。

软件

操作系统

Win7 64bit

功能

触发采集、连续采集,硬盘存储,回放显示

板卡标准

PCIe规范

板卡尺寸

全高PCIe标准卡

板卡重量

(含散热片)1Kg

板卡供电

12V(±10%);75W

工作温度

0到+60℃

三、软件内容

● FPGA软件开发工具Vivado2018.3 , Verilog语言开发;

● 接口软件内容包括如下:

● 板卡硬件测试;

● Flash加载测试代码;

● DDR4测试代码,两组同时工作、单独工作;

● AD、DA、时钟配置及采集接口程序测试(DA的Jesd204B IP使用Xilinx默认版本);

● PCIe3.0 x8模式XDMA测试,包含FPGA代码,在 Linux系统的PC机下的驱动;

● 触发信号测试代码;

● 其它GPIO测试代码。

以上程序提供测试用例,测试方法,测试报告及使用说明书

(备注:甲方提供软件测试验收的服务器,以保证后续使用的兼容性)

审核编辑 黄昊宇

-

8路SDI/HDMI/MIPI/PCIe-DMA音视频采集,V4L2驱动应用介绍2024-03-13 5365

-

基于XC7K325T的四路万兆PCIe光纤收发卡2014-11-24 6532

-

369-双路千兆网络PCIe收发卡解决方案2018-06-12 6195

-

PCIe数据卡设计资料第611篇:基于VU9P的双路5Gsps AD 双路6Gsps DA PCIe数据卡2022-01-25 698

-

光纤收发卡设计资料第295篇:基于 Kintex-7 XC7K325T的半高PCIe x4双路万兆光纤收发卡2022-01-27 1486

-

612XCVU9P板卡设计资料原理图:基于XCVU9P的32路光纤PCIeX16收发卡2023-01-06 1299

-

ADRV9009 PCIe射频收发平台2023-09-09 1746

-

基于VU9P的4路 100G光纤 6U VPX板卡2024-09-29 2173

-

XCVU13P板卡设计原理图:509-基于XCVU13P的4路QSFP28光纤PCIeX16收发卡2024-11-23 1957

-

PCIe收发卡设计资料:611-基于VU9P的2路4Gsps AD 2路5G DA PCIe收发卡2024-11-20 1196

-

XC7A100T板卡设计原理图:297-基于XC7A100T的PCIe千兆电口以太网收发卡2024-12-02 1790

-

设计原理图:U200E 基于VU9P的4路QSFP28光纤PCIeX16收发卡2025-05-29 972

-

PCIe数据卡设计资料第611篇-基于VU9P的双路5Gsps AD 双路6Gsps DA PCIe数据卡2025-09-19 831

-

【PCIE725G】青翼凌云科技基于 PCIe x16 总线架构的 JFM9VU9P FPGA 高性能数据预处理平台(100%国产化)2025-11-05 1200

-

【PCIE736】基于 PCIE X16 总线架构 4 路 QSFP28 100G 光纤通道处理平台(基于 VU3P FPGA)2025-12-23 1072

全部0条评论

快来发表一下你的评论吧 !