如何完成一个FPGA工程?

可编程逻辑

描述

如何完成一个FPGA工程?

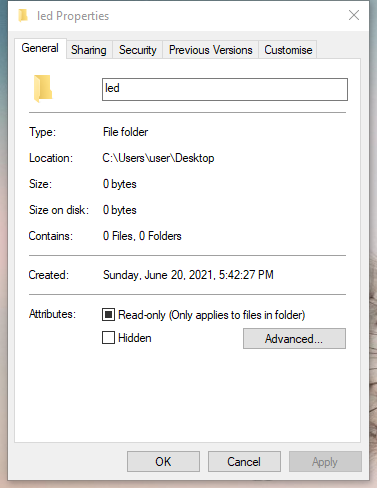

1.在你需要的路径下,新建一个文件夹。要求,路径中没有中文,否则,会造成错误。如图:

我是在桌面上新建了一个名为“led”的文件夹。

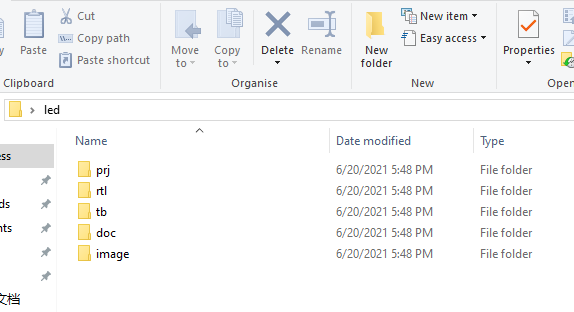

2.在这个led文件夹下,有这么一些子文件夹,如图:

上图中,prj为工程文件存放目录;rtl为verilog可综合代码存放目录;tb为测试文件存放目录;image为设计相关图片存放目录;doc为设计相关文档存放目录;prj文件夹下还建立了子文件夹ip,用于存放quartus中生成的IP核文件。

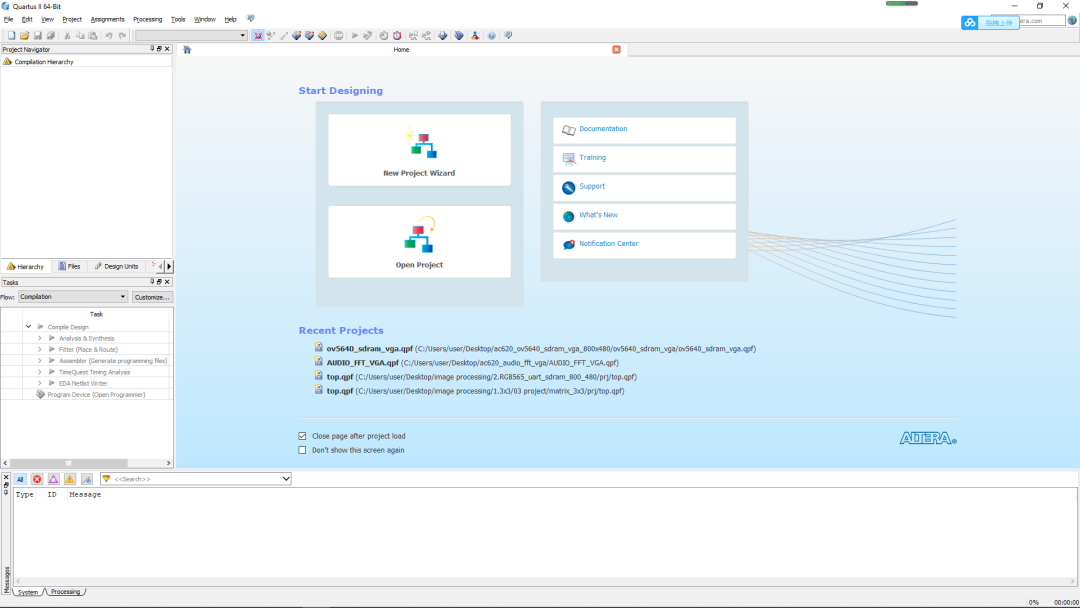

3.打开quartus软件,如图:

我电脑上装的是13.1版本,13.0版本略有不同,但外观并不影响使用。

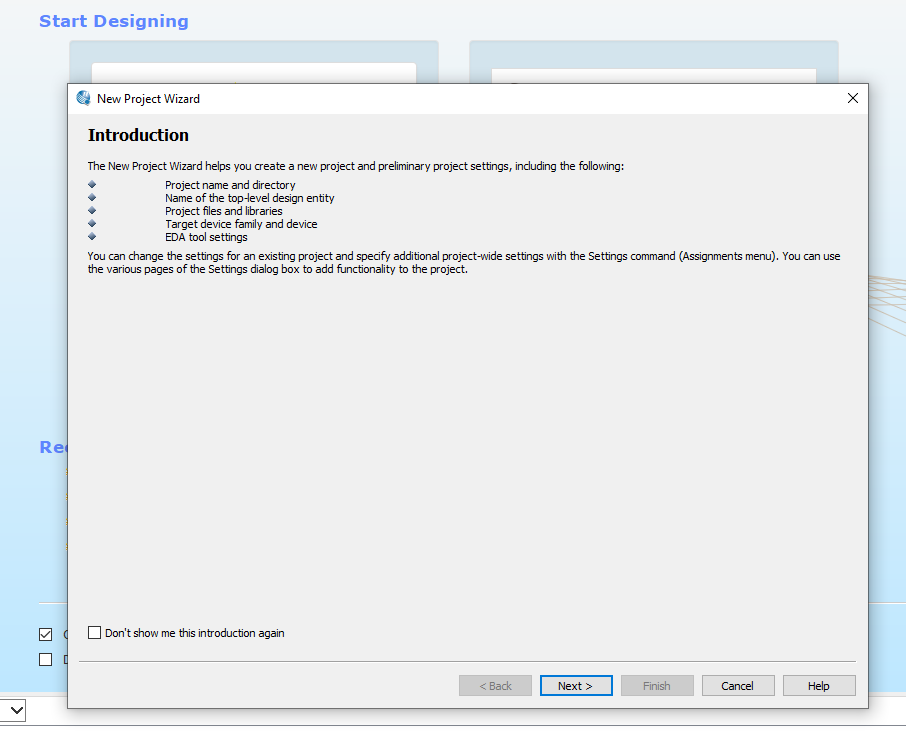

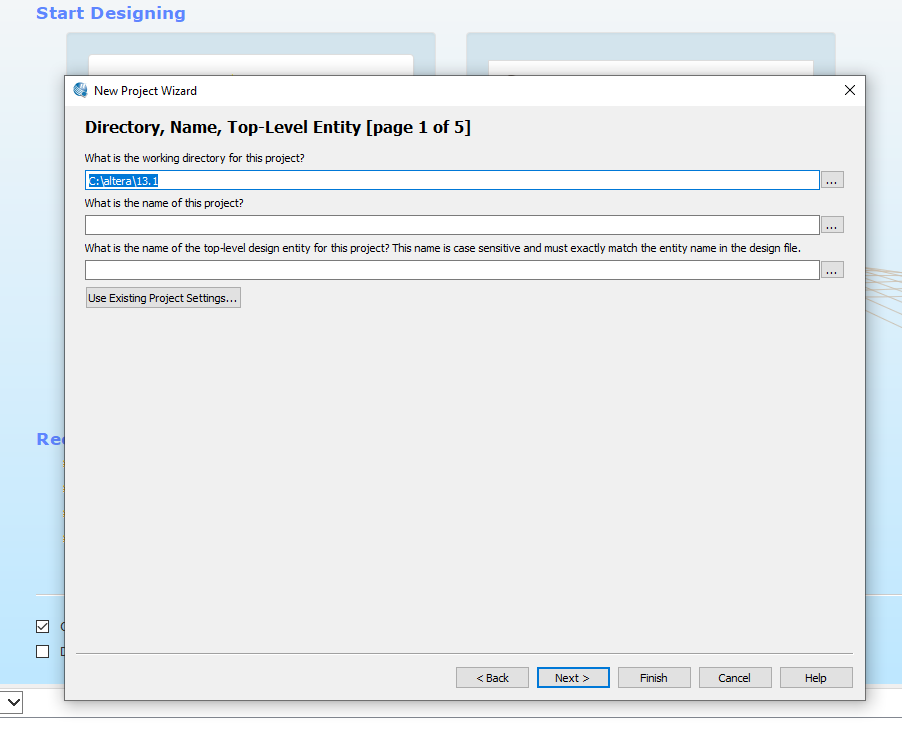

4.单击New Project Wizard来启动一个工程向导,或者在左上角File菜单栏下选择New Project Wizard亦可。弹出新窗口,如图:

点击Next,来到新界面:

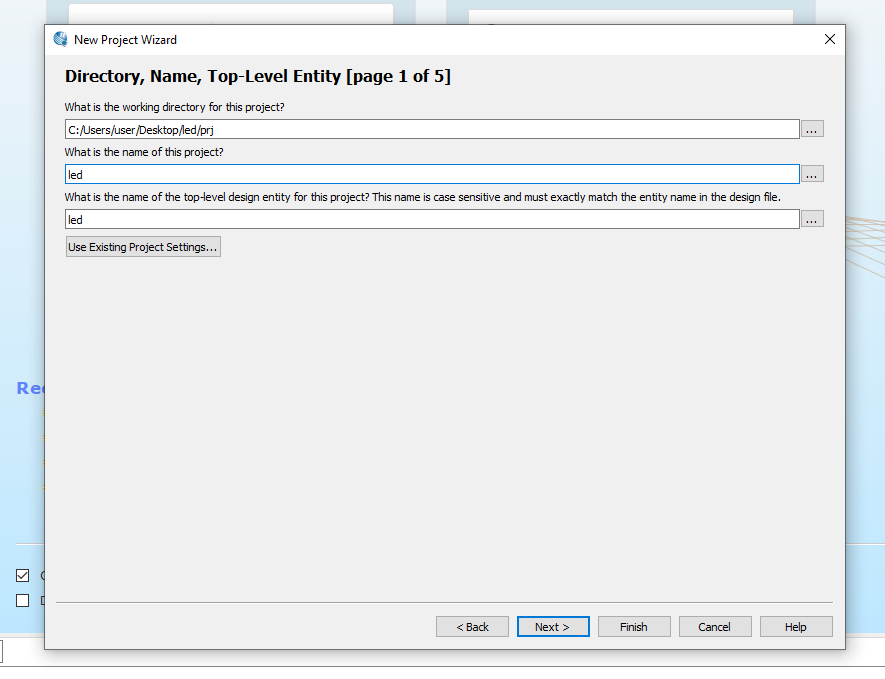

在第一栏中选择工程要存放的位置,注意,此路径中不可以有中文。在第二栏中填写此工程的名称,注意,此名称要和整个工程顶层模块的模块名一致。当填好第二栏,第三栏自动填好。我的测试工程如图:

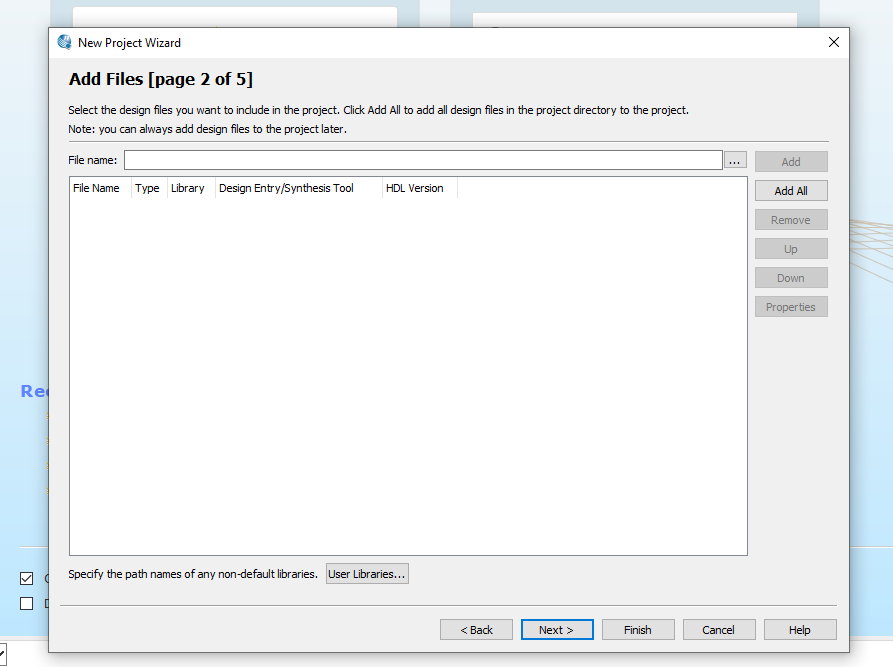

5.点击Next,进入新界面,如图:

这个界面是可以添加一些已经设计好的文件,这次测试工程先跳过,直接点Next,进入FPGA芯片选择界面,如图:

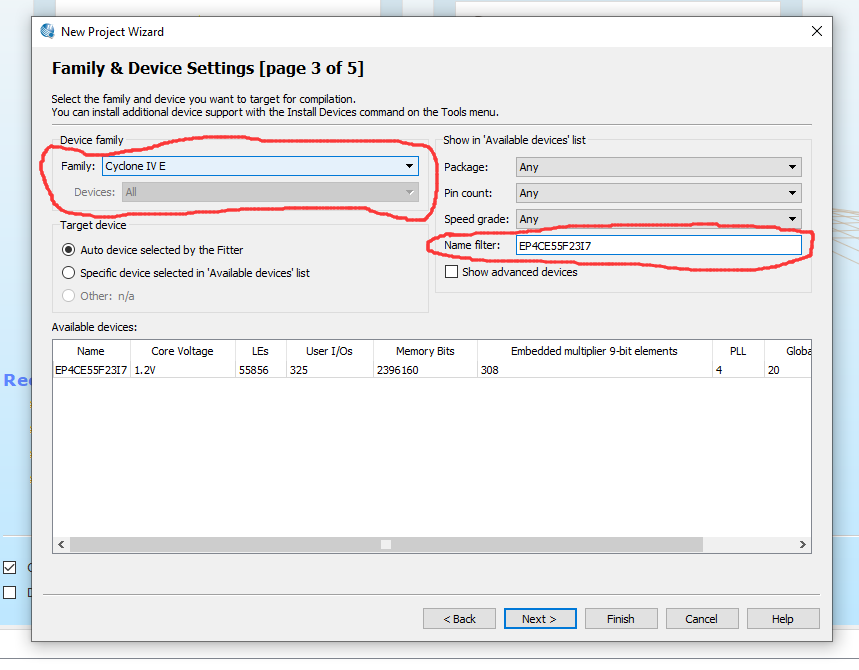

6.在图中,先选择左上角的器件型号,然后在右边那一栏填入你所要使用到的FPGA芯片的型号。在下方选中你所需要的FPGA芯片,然后点击Next,进入新界面:

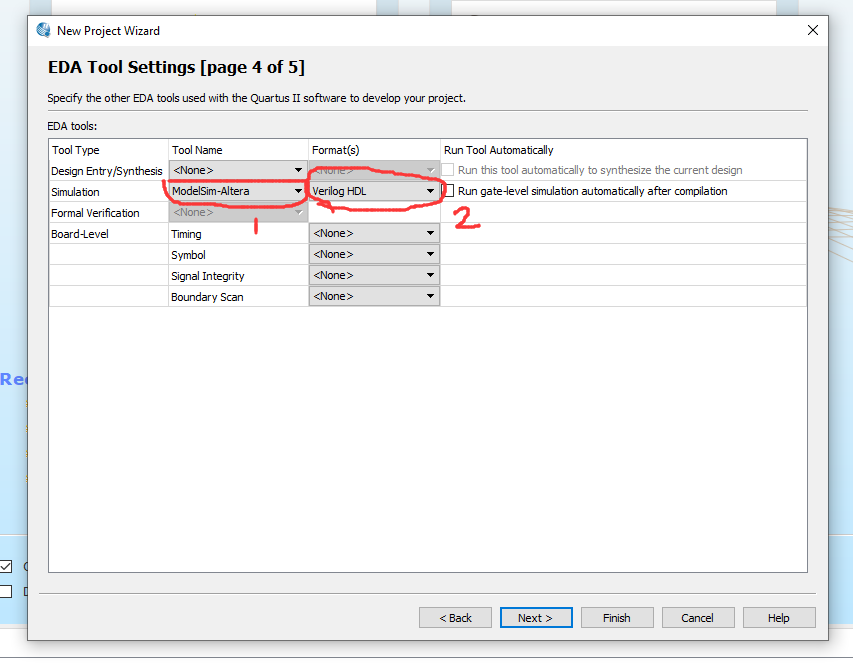

在这个界面中,一个是simulation,即仿真这一栏,对应图中标红的1处,要选择Modesim-Altera,同时在标红的2处要选择Verilog HDL,接着点击Next。如图:

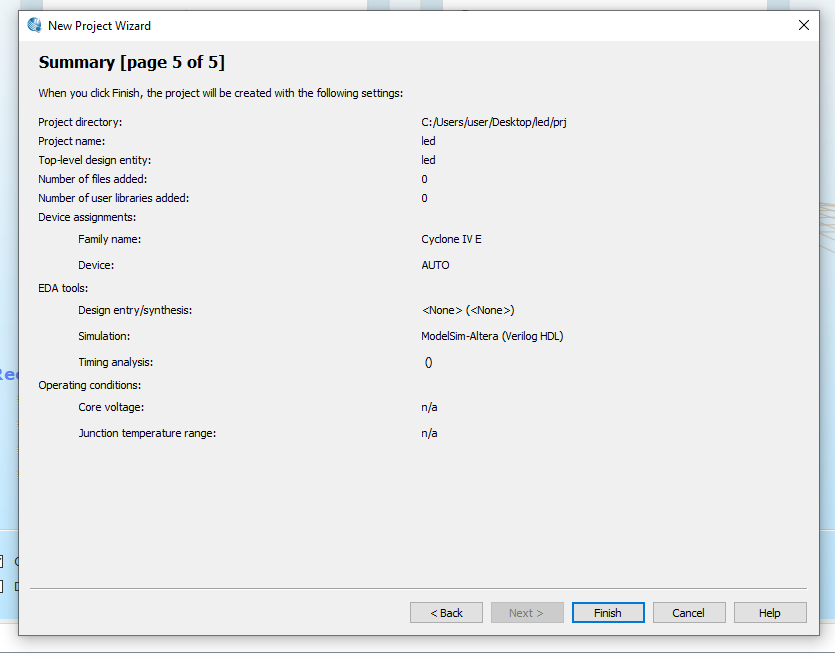

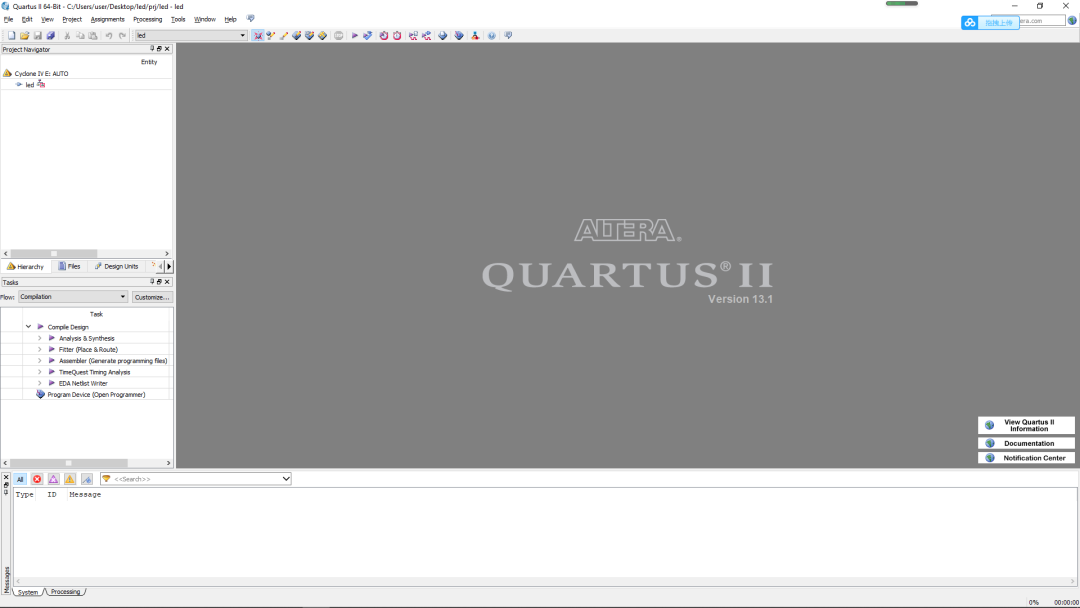

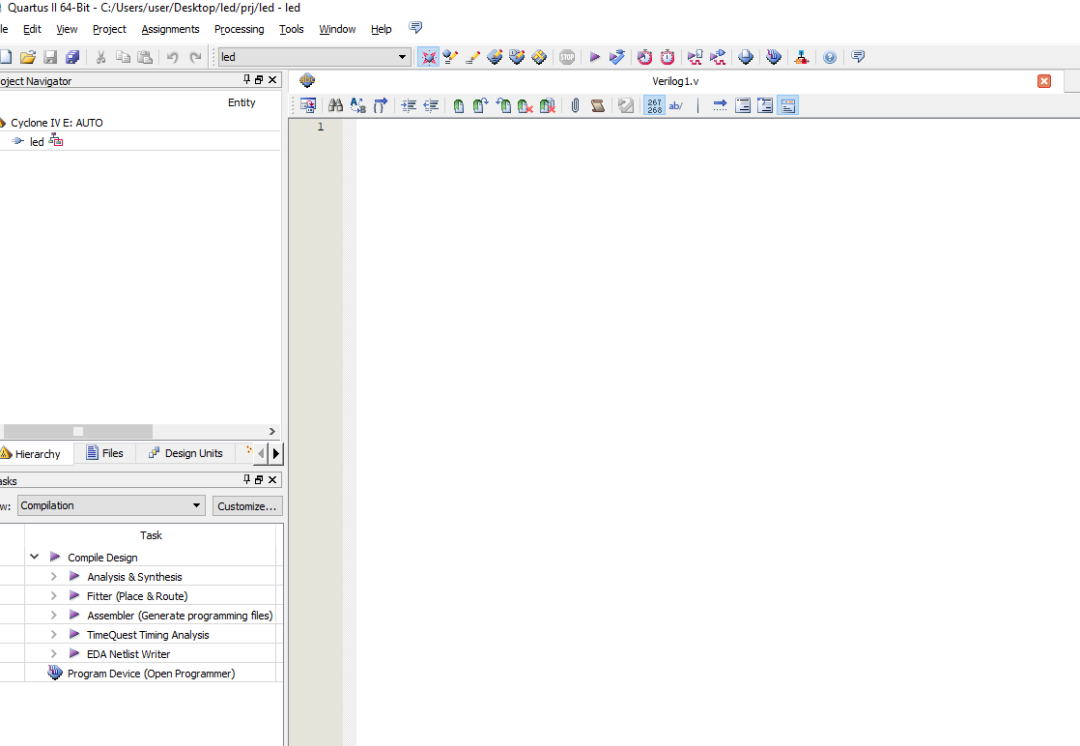

7.这个界面是对工程设置的各个参数信息进行汇总,直接点解Finish,完成工程的创建。然后界面变成这样:

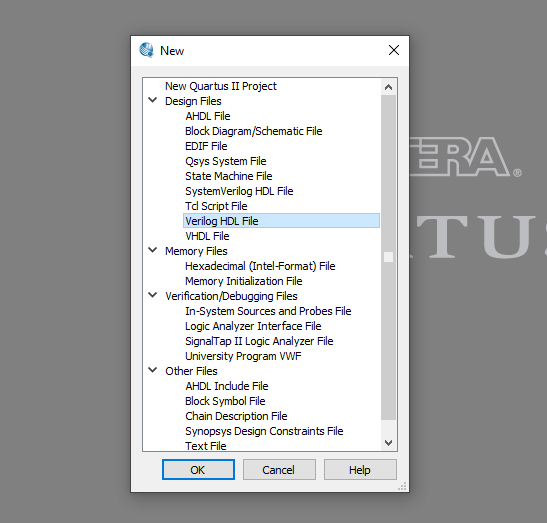

8.在工程新建完成后,选择左上角File---New---Verilog HDL File,如下图所示:

点击OK之后,来到新界面:

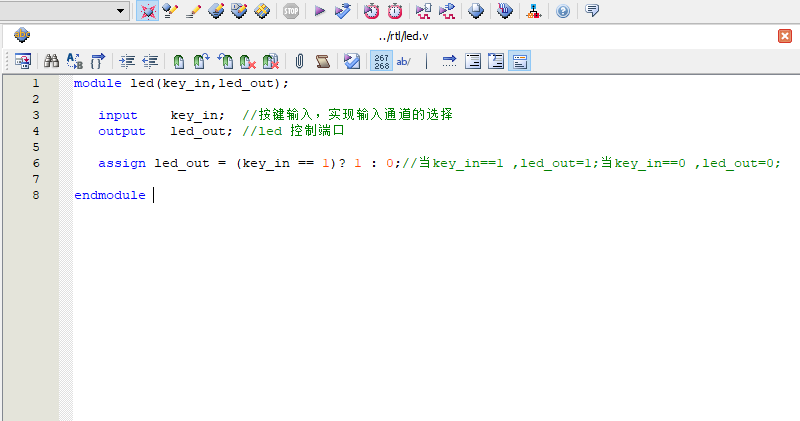

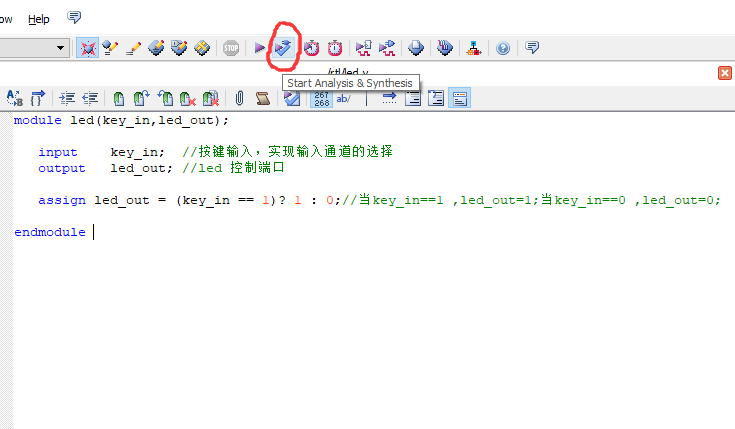

9.在新界面输入图中的代码:

|

module led(key_in,led_out); input key_in; //按键输入,实现输入通道的选择 output led_out; //led 控制端口 assign led_out = (key_in == 1)? 1 : 0;//当key_in==1 ,led_out=1;当key_in==0 ,led_out=0; endmodule |

语法下期会讲解,这一次,只需要知道在干嘛即可。这段代码的意思就是,外部来一个信号key_in,如果它是高电平1,则FPGA管脚输出led_out信号为一个高电平1;如果它是底电平0,则FPGA管脚输出led_out信号为一个底电平0。

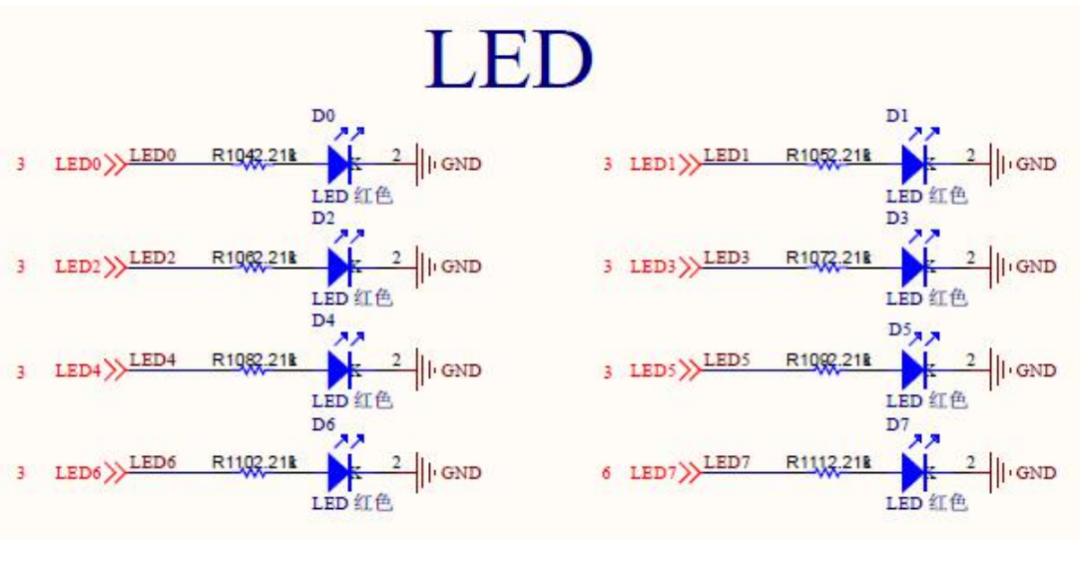

如图为硬木的开发板LED模块的电路,易得,只要来一个高电平1,LED就会亮;反之,来一个低电平0,LED就位暗。故,将led_out信号通过FPGA的管脚接到LED灯上,即可验证程序的正确性。

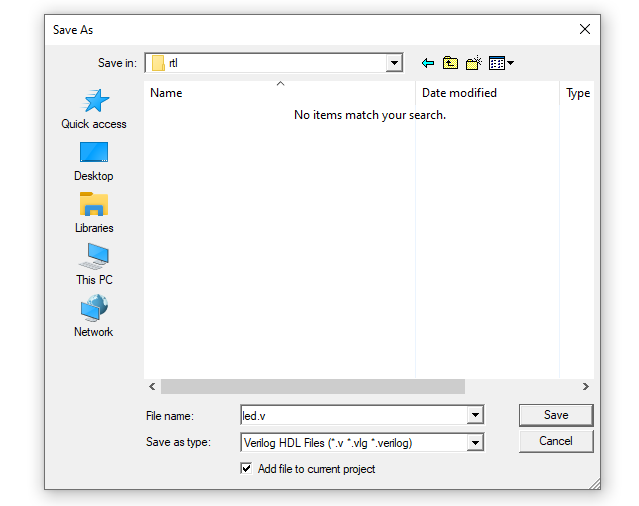

10.在代码编写完成,或者一开始新建了.v文件时,就应将文件保存至rtl文件夹之下。文件的名称为led。如图:

11.保存完了之后,点击如图的按钮,进行分析和综合。

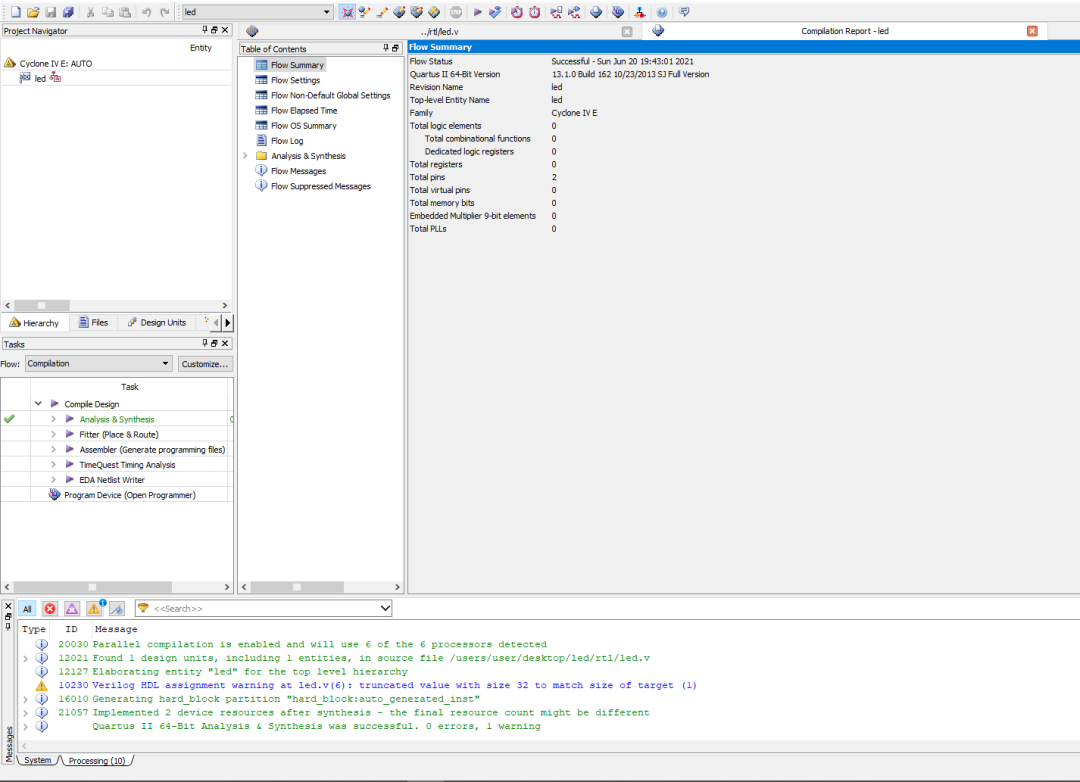

如果程序没有问题,则会出现如图界面,给出分析报告。

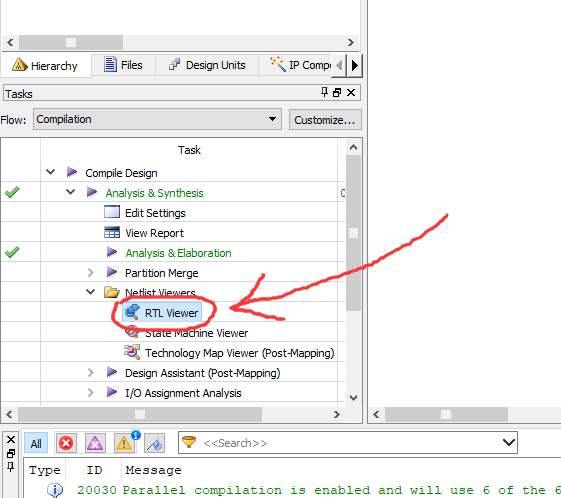

12.接着,可以在如图位置打开RTL图,对综合处理的电路进行查看。

此电路较为简单,没有太多的可看性,待后期遇到较为复杂的电路时,RTL图可以较为直观地展示电路各个模块之间及自身内部的结构。

致此,可综合电路的.v文件已经完成。

编辑:黄飞

- 相关推荐

- 热点推荐

- FPGA

- FPGA芯片

- Verilog HDL

-

解决FPGA一个解复用和时钟域转换问题2018-04-08 10614

-

FPGA入门:第一个工程实例之工程创建2015-02-12 4245

-

FPGA入门:第一个工程实例之设计输入2015-02-28 3897

-

Xilinx FPGA入门连载7:新建工程2015-09-18 6025

-

一个硬件工程师想重拾FPGA2016-10-10 3671

-

一个合格的FPGA工程师需要掌握哪些知识2017-05-14 4051

-

FPGA的第一个工程实例设计输入2019-02-13 2326

-

Xilinx Artix-7 FPGA快速入门、技巧与实例连载7——FPGA开发技能2019-04-10 2452

-

一个合格FPGA 工程师的基本要求2017-02-11 5533

-

fpga就业怎么样_fpga工程师是青春饭吗_fpga工程师发展前景2018-04-19 55541

-

如何在FPGA设计中创建一个中断事件2018-09-07 1091

-

NanoBoard 3000系列FPGA开发板助你数日内完成FPGA原型设计2018-10-20 1903

-

FPGA入门:第一个工程实例之功能仿真平台搭建2018-12-28 1404

-

FPGA视频教程之QuartusII使用简介与第一个工程实例的详细资料说明2019-03-01 1612

-

一个工程师关于FPGA项目的感言2022-02-16 2937

全部0条评论

快来发表一下你的评论吧 !