如何为DSP接口模式配置MAX2769C ADC寄存器

描述

MAX2769C ADC输出支持两种类型的基带接口:默认模式和DSP接口模式。本应用笔记讨论如何为DSP接口模式配置ADC寄存器。默认模式配置请参考MAX2769C数据资料。

介绍

MAX2769C是全球导航卫星系统(GNSS)接收器,在单芯片上集成GPS、GLONASS、伽利略和北斗导航卫星系统。这款单转换 GNSS 接收器旨在为工业应用和广泛的消费类应用(包括移动手机)提供高性能。

MAX2769C包括一个片内ADC,用于对下变频GNSS信号进行数字化处理。ADC输出CMOS逻辑电平,I和Q通道均具有一个或两个量化位,I通道最多为三个量化位。还提供I和Q模拟输出,可旁路片内ADC。

当使用ADC时,MAX2769C支持两种类型的基带接口:

在默认模式下,I和Q采样分别在I0和I1输出以及Q0和Q1输出上输出。用户可以选择寄存器配置使用每个I和Q样本的位数。每个CLK_OUT周期的I和Q输出上输出一个样本。

在DSP接口模式下,多达4位可以多路复用到单个输出上。

MAX2769C数据资料仅详细解释默认模式。本应用笔记说明如何配置DSP接口模式所需的寄存器。

DSP 接口模式

概述

DSP接口有两个目的。首先,DSP接口将ADC数据组装成帧,这些帧通过帧号在每个帧的开头插入时序信息。其次,DSP接口为多位ADC数据输出情况下的数据序列化提供了一种手段。

帧计数器的值作为时间戳插入到每个帧开头的数据流中。DIEID 代码的 2 位和STRM_BITS字的 2 位前缀为 28 位长的帧号,使得帧(时间戳)的总长度为 32 位,位于每个帧的开头。

在帧戳位之后,GPS 数据被序列化为位 0 的 16 位段,后跟位 1、位 2 和位 3。要序列化的位数由STRM_BITS字控制,该字在 1 位、2 位和 4 位大小写之间进行选择。

描述

片内多位ADC对下变频GPS信号进行数字化处理,并将数据输出为四个逻辑信号(位0、位1、位2、位3),分别代表I和/或Q通道中的符号/幅度、无符号二进制或二进制补码二进制数据。有关数据格式的详细说明,请参阅IC数据手册。

ADC的分辨率最多可设置为每通道3位。例如,符号/幅度格式的 2 位 I 和 Q 数据映射如下:位 0 = Sign_I,位 1 = Mag_I,位 2 = Sign_Q,位 3 = Mag_Q。

数据可以序列化为位 0 的 16 位段,后跟位 1、位 2 和位 3。要序列化的位数由STRM_BITS字控制,该字在位 0、位 0 和位 1、位 0 和位 2、位 0、位 1、位 2 和位 3 大小写之间进行选择。

如果仅序列化位 0,则数据流仅包含位 0 数据。如果选择了位 0 和位 1(或位 2)的序列化,则流数据模式由 16 位位 0 数据后跟 16 位位 1(或位 2)数据组成,后者后跟 16 位位 0 数据,依此类推。在这种情况下,串行时钟的速度必须至少是ADC时钟的两倍。

如果选择位 0、位 1、位 2、位 3 的 4 位串行,则串行时钟必须至少比 ADC 时钟快 4 倍。

如果使用小数时钟分频器,则串行(CLK_SER)和ADC (CLK_ADC)时钟之间的瞬时分频比在小数时钟分频器的控制下连续变化。例如,如果小数时钟周期等于串行时钟周期的 4.5 倍,则通过一系列交替的 /4 和 /5 周期实现 4.5 的平均分频比。

ADC数据并行加载到四个保持寄存器中,这些保持寄存器对应于四个ADC输出。保持寄存器的长度为16位,由ADC时钟计时,ADC时钟是从小数分频器输出获取的时钟。在16位ADC周期结束时,数据被传输到四个移位寄存器,并在下一个16位ADC周期内串行移位至输出。移位寄存器由串行时钟计时,该串行时钟必须足够快,以便在从ADC加载下一组数据之前将所有64 = 4 x 16位数据移出。在所有 64 位数据流式传输到输出后,数据遵循全零模式。DATA_SYNC信号用于表示每个有效 16 位数据片的开头。此外,ADC时钟每128至16,384个周期输出一个TIME_SYNC信号。

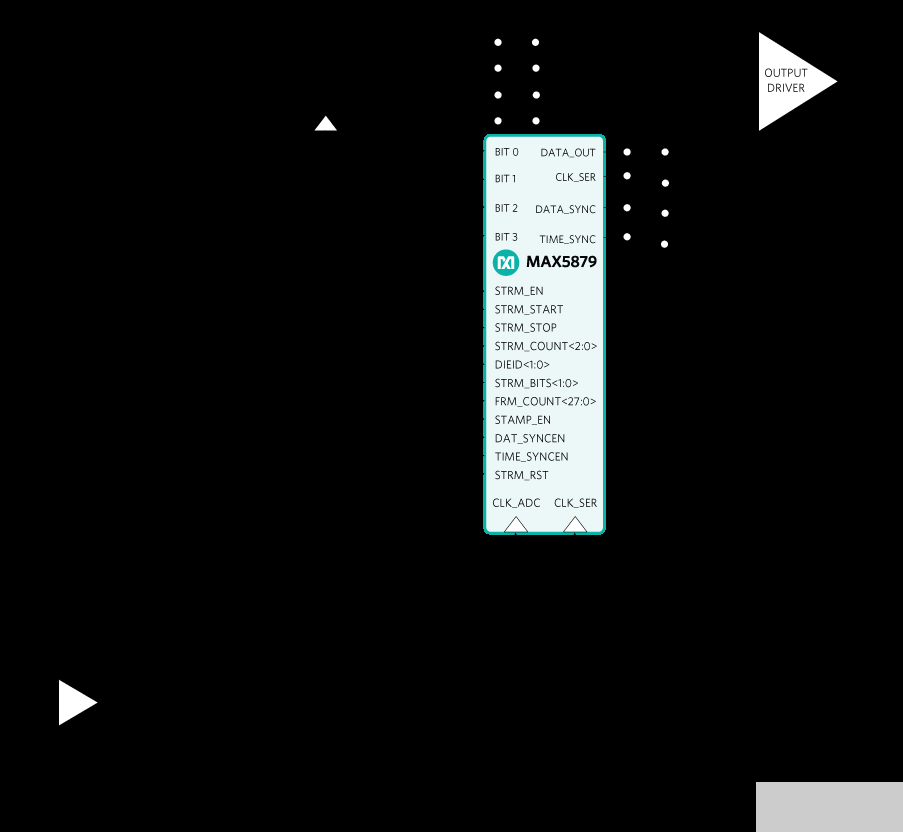

图1.顶级连接和控制信号。

3线SPI接口控制信号

STRM_EN:此命令配置IC,使DSP接口插入信号路径。同时,所有内部寄存器均被复位。

STRM_START:此命令的正边缘允许将数据流式传输到输出。它还支持时钟和帧同步输出。

STRM_STOP:此命令的正边缘禁用数据流到输出。它还禁用时钟和帧同步输出。

STRM_COUNT<2:0>:该控制信号选择数据(时间)计数器的长度;最小值为 128 位 (000),最大值为 16,394 位 (111)。

DIEID<1:0>:这个词标识IC的硬件版本。MAX2769C的默认版本对应于00。

STRM_BITS<1:0>:这个词定义了要流式传输到输出的位数。

00 = 位 0

01 = 位 0,位 1 10 = 位 0,位 2

11 = 位 0,位 1,位 2,位 3

FRM_COUNT<27:0>.这个词定义了开始流式传输的帧号。当命令STRM_EN启用流模式,但未收到命令STRM_START时,此模式处于活动状态。在这种情况下,帧计数器在断言STRM_EN时重置,并开始计数。当帧数达到FRM_COUNT定义的值时,流式传输开始。

STAMP_EN:此信号允许在每帧的开头插入帧号。如果禁用,则仅将ADC数据流式传输到输出。

DAT_SYNCEN:该控制信号使DATA_SYNC输出端的同步脉冲成为可能。每个脉冲的上升沿与有效数据流的开头重合,有效数据流始终从位 0<0> 数据开始,并在 16、32 或 64 个周期后停止,具体取决于流的位数。

TIME_SYNCEN:当通过 STRM_EN 命令启用流时,此信号始终启用时间同步脉冲的输出。否则,时间同步脉冲仅在数据流在输出端处于活动状态时可用,即在STRM_START和STRM_STOP命令限制的时间间隔内。

STRM_RST:此命令重置所有计数器,而不考虑流周期内的时间。

图2.方框图。

时序图

在DSP接口模式下,基带是MAX2769C DATA_SYNC、TIME_SYNC和DATA_OUT输出的接收器。DATA_SYNC、TIME_SYNC和DATA_OUT信号置位在CLK_SER的上升沿,需要锁存到时钟下降沿的基带中。图3和图4显示了DSP接口信号的功能时序。

图3.时序图。

图4.具有时间戳输出的时序图。

| 计时值 | ||||

| 时间 | SYw | 偏差 | ||

| t延迟 | 0ns | ±2纳秒 | ||

|

0.5 | ±0.03 | ||

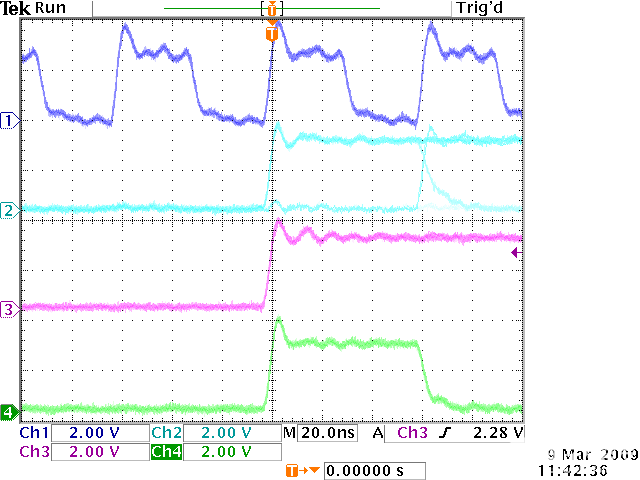

表1中的数字表示通常预期的时序值和与标准值的预期最大偏差。图5进一步显示了实际应用中三种信号之间的关系。

CLK_SER信号的占空比主要由施加在MAX2769C引脚15 (XTAL)上的基准信号的占空比决定。所提供的数字适用于使用Rakon IT3205CE系列16.368MHz TCXO作为参考的情况。

本数据代表Maxim迄今为止为提供具体应用指导所做的最大努力,但不作任何保证。

图5.CLK_SER、DATA_OUT和TIME_SYNC之间的关系。深蓝色 (1) = CLK_SER,浅蓝色 (2) = DATA_OUT,粉红色 (3) = TIME_SYNC,绿色 (4) = DATA_SYNC。

寄存器配置

| 位名 |

位置 (0 = LSB) |

违约 | 功能 |

| STRM_EN | 11 | 0 | 用于串行数据流的DSP接口使能。该位配置IC,使DSP接口插入信号路径。设置 1 启用接口,或设置 0 禁用接口。 |

| STRM_START | 10 | 0 | 此命令的正边缘允许将数据流式传输到输出。它还支持时钟、数据同步和帧同步输出。 |

| STRM_STOP | 9 | 0 | 此命令的正边缘禁用数据流到输出。它还禁用时钟、数据同步和帧同步输出。 |

| STRM_COUNT | 8:6 | 111 |

将时间计数器的长度设置为 128 (000) 到 16384 (111)。 注意:IC数据手册将这些位显示为保留位,但这些位仍然可以控制。 |

| STRM_BITS | 5:4 | 01 | 流式传输的位数。D[5:4] = 00: I MSB;01: 我 MSB, I LSB;10: I MSB, Q MSB;11: I MSB, I LSB, Q MSB, Q LSB. |

| STAMP_EN | 3 | 1 | 该信号允许在每帧的开头插入帧号。如果禁用,则仅将ADC数据流式传输到输出。 |

| TIME_SYNCEN | 2 | 1 | 当通过 STRM_EN 命令启用流时,此信号始终启用时间同步脉冲的输出。否则,时间同步脉冲仅在数据流在输出端处于活动状态时可用,例如,在STRM_START和STRM_STOP命令限制的时间间隔内。 |

| DAT_SYNCEN | 1 | 0 | 该控制信号使能DATA_SYNC输出端的同步脉冲。每个脉冲与对应于给定输出位的16位数据字的开头重合。 |

| STRM_RST | 0 | 0 | 此命令重置所有计数器,而不考虑流周期内的时间。 |

| 位名 |

位置 (0 = LSB) |

违约 | 功能 |

| L_CNT | 27:16 | 256天 | 设置 L 计数器的值。000100000000 = 256 小数时钟分频器,10000000000 = 2048 小数时钟分频器 |

| M_CNT | 15:4 | 1563年 | 设置 M 计数器的值。011000011011 = 1563 小数时钟分频器,100000000 = 2048 小数时钟分频器 |

| FCLKIN是 | 3 | 0 | 小数时钟分频器。设置1以选择来自小数时钟分频器的ADC时钟,或设置0以绕过来自小数时钟分频器的ADC时钟。 |

| ADCCLK | 2 | 0 | ADC 时钟选择。设置0以选择来自基准分频器/乘法器的ADC和小数分频器时钟。 |

| 瑟克 | 1 | 1 | 0 选择来自基准分频器的串行器时钟。 |

| 模式 | 0 | 0 | DSP接口模式选择,设置为1表示标准模式操作。 |

审核编辑:郭婷

-

用DSP的I2C接口配置TVL320AIC12K的寄存器,为什么读出寄存器的数据显示为默认值?2024-10-25 417

-

MAX2112寄存器配置问题2016-03-09 5235

-

如何在stm32上通过SPI将32位字传输到GPS接收器芯片(MAX2769C)?2023-01-30 1806

-

ARM I2C 总线接口的寄存器设置2009-03-14 1931

-

MPC860寄存器配置2011-06-08 1198

-

MAX11120-MAX11128低功耗,逐次逼近寄存器串行ADC2012-01-31 3095

-

DSP2812寄存器详解2016-01-08 1170

-

MAX2769 GPS接收机用户指南 - 用户指南 - Maxi2016-05-18 986

-

max2769cfcen配置使用指南2017-03-28 1391

-

MAX2769 GPS接收机用户指南2017-04-06 1324

-

如何编程MAX32620FTHR平台及配置寄存器2018-10-11 4309

-

IO口配置常用的8个寄存器 1.62021-11-29 2815

-

GPIO寄存器2021-12-08 1397

-

STM32F103寄存器配置相关学习 —— GPIO2022-01-17 1238

-

如何为 DSP 接口模式配置 MAX2769C ADC 寄存器2022-11-16 141

全部0条评论

快来发表一下你的评论吧 !