数字控制振荡器(NCO)的FPGA实现

FPGA/ASIC技术

描述

NCO(N umerically Controlled Oscillator)是用于产生一个理想的、数字可控的正弦或余弦波的数字控制式振荡器,其实现方法有实时计算法和查表法等多种。实时计算法的正弦波样本以实时计算产生,该方法因其计算需要耗费很多时间,因而只能产生较低频率的正弦波,而且存在计算精度与计算时间的矛盾。由于在需要产生高速的正交信号时,实时计算法将无法实现。因此,在实际应用中一般采用最有效、最简单的查表法,即事先根据各个NCO正弦波的相位计算好相位的正弦值,并按相位作为地址信息存储该相位的正弦值数据。

1 NCO的基本原理

在通过相位累加产生地址信息时,通常需要输出当前时刻的相位值所对应的正弦值,即以参考频率源对相位进行等可控间隔采样。众所周知,理想的正弦波信号S(t)可以表示成:

式(1)说明,信号s(t)在振幅A和初相φ确定之后,其频率可以由相位来唯一确定。即:

NCO就是利用式(2)中φ(t)与时间t成线性关系的原理来进行频率合成的,也就是说,在时间t=△t间隔内,正弦信号的相位增量△φ与正弦信号的频率f可构成一一对应关系,也就是说,对式(2)两端进行微分后有:

。

由上面的讨论可知:

其中,△θ为一个采样间隔△t之间的相位增量,采样周期

。故式(3)可改写为:

由式(4)可知,如果可以控制△θ,就可以控制不同的频率输出。由于△θ受频率控制字FCW的控制,即:

,所以,改变FCW就可以得到不同的输出频率f0,然后经代换处理可得如下方程:

式(5)和式(6)中的L为相位累加器的位数。根据Nyquist准则,允许输出的频率最高为FCLK/2,即

。但在实际工程中,由于受到低通滤波器的限制,一般输出的频率

。

2 NCO的性能指标

NCO的性能指标包括信号频率分辨率、信噪比(SNR)、无杂散动态范围(SFDR)和输出的信号正交性。这些性能指标取决于NCO的数据位数。NCO的数据位数包括用于表示相位数据的位数n和表示相位的正弦值数据的位数nb,二者之间存在nb取决于n的关系,且前者必须能够表示相位变化时其相位正弦值变化的最小值和最大值。而这又分为两种情况:

第一种情况是相位最小变化值的正弦值最小变化发生在π/2-△φ~π/2,π/2~π/2+△φ,3π/2-△φ~3π/2,3π/2~3π/2+△φ,同时其相位的取值是在0~2π间且等间隔地分为2n爪取值点,因此,由正弦波的特性可知:只需要讨论相位在π/2-△φ与π/2取值点的正弦值之差:

第二种情况是相位最小变化值的正弦值的最大变化发生在0~△φ,π-△φ~π,π~π+△φ,2π-△φ~2π取值点处。该情况可以通过类似于第一种情况的推导方法得到:

设计时可以根据式(9)和式(10)较好地取值n和nb,以避免相位的分辨率发生钝化,并很好地达到设计要求。

NCO的噪声是因为存在正弦值的量化误差而引入的,且量化误差由表示正弦值的位数决定,其近似关系为:

式中,B是作为寻址ROM的地址的舍位位数,n是相位位数。NCO的另一个性能参数是频率分辨率△f,该参数取决于相位位数,其关系式为:

3 NCO在FPGA中的实现

NCO的查找表是一个正弦值表,该表的正弦值是按照相位作为存储地址来进行存储的,而且一般以相位递增的方式存储。利用正弦波的奇偶对称性,可以把2π相位分成4等份,然后利用各等份之间的对称性来实现地址信息的映射,通常只存储[0,π/2]象限内的幅度码。

相位累加器可完成相位累加,即每来1个时钟就累加1次φ=φ+△φ,且采用流水线方式工作。本设计采用QUARTUS II中IP核自带的一种32位累加器来实现相位的累加。

逻辑转换完成后,可采用小表结构功能块把相位累加器产生的最高2位信号转换为地址控制信号和象限转换控制信号。其中地址控制信号是根据最高两位信号来控制地址从0开始递增方式产生还是从2L开始以递减方式产生。

正弦表是每来一个时钟输出一个大于零的正弦值数据,这些数据可作为象限变换器的输入,由象限变换器完成数据的象限变换。其转换原则是:象限控制信号根据正弦信号的对称性把查表得到的数据转换为正负数据,并对于正弦信号的1、2象限数据进行加零操作,而对3、4象限的数据进行求补运算。余弦数据也同样,在1、4象限对数据进行加零操作,2、3象限数据进行求补运算。

4 仿真结果

利用上述小表结构实现的NCO可以输出多种频率信号并减少资源消耗,影响系统输出频率的因素主要是工作频率和器件性能。

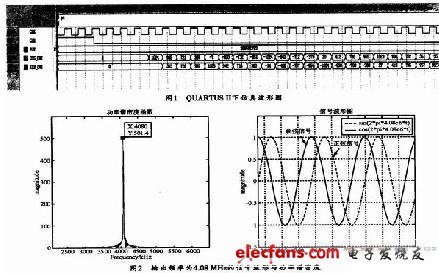

图1所示是整个NCO在QUARTUS II中的仿真波形图。

在图1所示的波形图中,CLK是时钟输入频率(为65.6 MHz),CLR为系统复位信号,相位累加器的位数L为32位,输出信号幅度位数为12位(包括符号位),相位宽度为12位,这样,由式(5)便可得到频率控制字FCW为269591793,图1中的COS_OUT与SIN_OUT是系统输出信号,频率为4.08 MHz。

由式(11)、(12)、(13)可得,此系统的信噪比和SFDR分别为74 dB和84 dB。

图2所示是将波形文件中的正弦余弦数据读入MATLAB中所显示出来的波形。

5 结束语

本文通过分析数控振荡器的实现原理和性能,给出了通过FPGA来实现NCO的具体方法,同时通过QUARTUSⅡ中的仿真验证了本设计的正确性。结果证明,用该方法设计的NCO可以输出多种频率的信号,同时也可以减少资源消耗。

-

pptvjun

2016-10-13

0 回复 举报写得比较清楚,尤其是原理从最基本的交代起,容易入门,我看了许多其他的文章,千篇一律,直接就给个结果,对我这种初学者来说简直就是灾难,加油楼主。 收起回复

pptvjun

2016-10-13

0 回复 举报写得比较清楚,尤其是原理从最基本的交代起,容易入门,我看了许多其他的文章,千篇一律,直接就给个结果,对我这种初学者来说简直就是灾难,加油楼主。 收起回复

-

基于FPGA的NCO设计方案2012-01-06 8113

-

MG32F02A/U 64/128 NCO(数字控制振荡器)2021-07-02 1671

-

基于FPGA的数控振荡器原理及设计方法2021-07-15 4213

-

基于DSP的数字振荡器的设计与实现2021-08-09 1709

-

M0系列亮点: NCO和CCL, 可PWM细致调频和内置编程逻辑2023-08-29 909

-

数字控制的非稳态多谐振荡器电路图2009-04-06 679

-

指数式数字控制振荡器电路图2009-04-15 497

-

数字控制式无稳态多谐振荡器电路图2009-05-16 524

-

基于FPGA和SRAM的数控振荡器的设计与实现2010-01-07 1298

-

数字控制振荡器,数字控制振荡器电路原理分析2010-03-23 2654

-

CMOS振荡器设计2011-06-15 11878

-

基于FPGA的数控振荡器的设计2017-11-23 4289

-

数控振荡器的基本原理及如何在FPGA中实现设计2020-08-26 3838

-

数字控制振荡器的作用与原理分析2024-02-09 4279

-

数字振荡器的实现要求有哪些2024-09-25 1028

全部0条评论

快来发表一下你的评论吧 !